Fターム[5F083FR02]の内容

半導体メモリ (164,393) | 強誘電体メモリ (1,733) | キャパシタを有するもの(破壊読出型) (1,245) | 1Tr/1C型 (791)

Fターム[5F083FR02]に分類される特許

41 - 60 / 791

半導体装置及びその製造方法

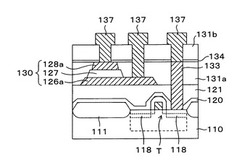

【課題】水分又は水素の侵入による強誘電体キャパシタの性能劣化をより確実に防止できるとともに、製造工程数の増加を回避できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板110上にトランジスタTを形成した後、第1の絶縁膜121を形成する。次に、第1の絶縁膜121上に強誘電体キャパシタ130を形成し、その上に第2の絶縁膜131aを形成する。次に、第2の絶縁膜131aの上面を平坦化して強誘電体キャパシタ130の上部電極128aの上面と連続するようにした後、トランジスタTの不純物領域118に接続するプラグ133を形成する。その後、酸化アルミニウム等により水素バリア層134を形成し、その上に第3の絶縁膜131bを形成する。次いで、強誘電体キャパシタ130及びプラグ133に接続する配線137を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 製造工程における強誘電体キャパシタの劣化を抑制することが可能な半導体装置およびその製造方法を提供する。

【解決手段】 加工後のキャパシタ側面に、例えば、第二の保護膜としての第二のCeZrO膜125を形成し、熱処理を加えることでCeZrO膜中の酸素原子が、キャパシタの誘電体膜であるPZT膜120および酸化物により形成されるキャパシタの電極の酸素欠損を補充するように拡散することとなる。但し、加工後のキャパシタ側面にCeZrO膜125を形成した後に、熱処理の工程をあえて追加して行わない場合であっても、CeZrO膜125の形成後に層間絶縁膜を形成するCVD工程において加熱が行われ、PZT膜120およびキャパシタの電極に酸素供給が行われることとなる。

(もっと読む)

半導体装置およびその製造方法

【課題】特性の優れた強誘電体キャパシタを有する半導体装置を提供する。

【解決手段】Ir膜117と、IrO2膜122と、Ir膜117とIrO2膜122との間に設けられたPZT膜120,121と、を含む強誘電体キャパシタを有する、半導体装置を製造する方法であって、

Ir膜117の上に導電膜118を形成し、導電膜118の上にSRO膜119を形成し、SRO膜119を結晶化する第1の熱処理を行い、スパッタ法により、SRO膜119の上にシードPZT膜120を形成し、シードPZT膜120を結晶化する第2の熱処理を行い、CVD法により、シードPZT膜120の上にバルクPZT膜121を形成する。

(もっと読む)

半導体記憶装置

【課題】強誘電体膜の膜質を均一化するチェインFeRAM型半導体記憶装置を提供する。

【解決手段】半導体記憶装置80は、同一素子形成領域に隣接配置される、一対のソース/ドレイン層5を有するメモリトランジスタTR1及びTR2と、メモリトランジスタのソース/ドレイン層5の他方とメモリトランジスタTR2のソース/ドレイン層5の一方に、ビア及びバリアメタル膜13を介して接続される強誘電体キャパシタCAP1及びCAP2とを有する。強誘電体キャパシタCAP1及びCAP2は、バリアメタル膜13上に設けられ、四角錐台形状の下部電極14と、下部電極14を覆うように設けられる強誘電体膜15とを共有し、強誘電体キャパシタCAP1は、強誘電体膜15上に設けられる第1の上部電極16aを有し、強誘電体キャパシタCAP2は、強誘電体膜15上に設けられ、第1の上部電極16aと離間して配置される第2の上部電極16bを有する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】キャパシタの周囲を覆う下部水素バリア膜と上部水素バリア膜とによって、キャパシタを構成する容量絶縁膜の水素による劣化を防止すると共に、下部水素バリア膜と上部水素バリア膜との接続部によるキャパシタ形成領域の面積の増大を防止できるようにする。

【解決手段】半導体記憶装置は、半導体基板101の上に形成された下部水素バリア膜110と、下部水素バリア膜110の上に形成され、強誘電体又は高誘電体からなる容量絶縁膜113を含む少なくとも1つのキャパシタ115と、キャパシタ115の上方及び側方を覆うと共に、キャパシタ115の周辺領域において下部水素バリア膜110と接続される接続部119を有する上部水素バリア膜118とを有している。ここで、下部水素バリア膜110と上部水素バリア膜118との接続部119における接続面は、半導体基板101の主面に向かう方向に延びている。

(もっと読む)

強誘電体キャパシタの形成方法、強誘電体キャパシタおよび電子デバイス

【課題】キャパシタ特性の良好な強誘電体キャパシタを提供することにある。

【解決手段】本発明の強誘電体キャパシタの形成方法は、(a)基体10の上方に第1導電層20aを形成すること、(b)前記第1導電層20a上に、酸素を有する強誘電体物質を含む強誘電体層30aを形成すること、(c)前記強誘電体層30a上に第2導電層40aを形成すること、(d)前記第2導電層40a上にマスクM1を形成すること、(e)前記マスクM1を用いて、少なくとも前記第2導電層40aをエッチングすることにより、前記第1導電層20、前記強誘電体層30、及び該第2導電層40からなるキャパシタを形成すること、(f)前記(e)の工程の後、前記エッチングにより露出した前記強誘電体層30の露出面にフッ素を付着させること、(g)前記キャパシタに熱処理を施すこと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】PZTの配向性を向上できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、絶縁膜を形成する工程と、絶縁膜上方に、Ptで下部電極用導電膜を形成する工程と、下部電極用導電膜を、酸素を含む雰囲気に曝し、Ptの酸化膜を形成する工程と、下部電極用導電膜上に、PZTで強誘電体膜を形成する工程と、強誘電体膜上に、上部電極用導電膜を形成する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタの下部電極材料の選択自由度が高く、ビア工程の少ない半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板101上に形成されたスイッチングトランジスタ301A,301Bと、拡散層121と、トランジスタ301上に形成された層間絶縁膜131と、下部電極211、強誘電体膜212、及び上部電極213を含む強誘電体キャパシタ201A,201Bと、上部電極213の上方に形成された配線層141と、上部電極213と配線層141とを電気的に導通させる第1のプラグTWと、拡散層121と配線層141とを電気的に導通させる第2のプラグV1A,V1Bと、下部電極211の側方に配置されており、下部電極211と拡散層121とを電気的に導通させる第3のプラグCSFとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体特性である分極量を維持しつつ疲労特性を向上させた信頼性が高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、基板101の上に形成され、高融点金属を含む導電体膜131と、導電体膜131の上に形成された複数の金属元素を含む強誘電体金属酸化膜132とを備えている。強誘電体金属酸化膜132は、複数の金属元素のうちの一の金属元素と酸素元素との化学量論的結合を、一の金属元素と酸素元素との酸素欠損を含む結合よりも多く含む。

(もっと読む)

容量素子及びその製造方法

【課題】リーク電流を実用レベルまで低減し且つ半導体集積回路装置の微細化を進めても十分なメモリの保持特性を保証できる電荷量を確保する。

【解決手段】容量素子216は、AがAサイトを占める元素、BがBサイトを占める元素、Oが酸素原子を表すとき、一般式ABO3 により表される単純プロベスカイト型結晶構造の金属酸化物からなる容量絶縁膜214と、これを挟み込む第1の電極及び第2の電極212及び215を備える。Aサイトにはビスマスの陽イオン、Bサイトには遷移元素である第1の元素の陽イオンが配置されている。Aサイト及びBサイトの少なくとも一方は、ビスマス及び第1の元素以外の金属元素より選ばれた第2の元素の陽イオンによって一部置換されている。第2の元素の陽イオンによる置換量は、容量絶縁膜214と、第1の電極212及び第2の電極215との界面のうち少なくとも一方において最大となっている。

(もっと読む)

強誘電体メモリ装置及びその製造方法

【課題】強誘電体膜の結晶化のための焼き締めによる熱処理不足によるメモリ特性の低下、特に強誘電体膜の残留分極特性の低下を防止しながら、製造プロセスの低温熱処理化を実現できる強誘電体メモリ装置を提供する。

【解決手段】強誘電体メモリ装置は、p型半導体基板1上に、下部電極10、ペロブスカイト型結晶構造を持つ強誘電体膜からなる容量絶縁膜11及び上部電極12がこの順に積層して形成された強誘電体キャパシタを備えている。上部電極12上に形成され、集光により強誘電体膜12を選択的に加熱する凸型レンズ14をさらに備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体膜を用いたキャパシタの更なる特性の向上を実現し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上方に形成された下部電極48と;下部電極上に直接形成され、Laが添加されたチタン酸ジルコン酸鉛の第1の強誘電体膜50と、第1の強誘電体膜上に直接形成され、第1の強誘電体膜より膜厚が薄く、LaとCaとSrとが添加されたチタン酸ジルコン酸鉛の第2の強誘電体膜52とを有するキャパシタ誘電体膜54と;キャパシタ誘電体膜上に形成された上部電極60とを有するキャパシタを有している。

(もっと読む)

強誘電体キャパシタの製造方法

【課題】 強誘電体メモリにおいて、強誘電体キャパシタのリーク電流の面内ばらつきを抑制することが困難である。

【解決手段】 基板の上に、導電性の下部電極膜を形成する。下部電極膜の上に、下方の一部分が結晶化され、表層部はアモルファス状態である強誘電体材料からなるキャパシタ誘電体膜を形成する。キャパシタ誘電体膜の上に、導電性の第1の上部電極膜を形成する。第1の上部電極膜を形成した後、722℃以下の温度で熱処理を行って、キャパシタ誘電体膜のアモルファス状態の部分を結晶化させる。結晶化させた後、第1の上部電極膜の上に、第1の上部電極膜よりも厚い導電性の第2の上部電極膜を形成する。

(もっと読む)

半導体記憶装置

【課題】COB構造の強誘電体半導体メモリにおいて、信号劣化が発生する強誘電体膜の周辺領域の面積を減らす。

【解決手段】選択ワード線に直交する方向に隣接する2つのセルトランジスタで通過ワード線を共有させ、各セルのワード線を1.5本にすることにより、キャパシタの形状を正方形に近づける。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】1容量素子当たりの面積を、微細加工に問題を起こすことなく縮小できるようにする容量素子を有するメモリーのような半導体装置を提供する。

【解決手段】酸素バリア膜16、層間絶縁膜17(酸化シリコン膜)上に、薄いエッチングストッパー膜18(窒化シリコン膜)、層間絶縁膜19(酸化シリコン膜)を形成し、酸素バリア膜16の直上にそれより大きい開口部をドライエッチングにより形成する。その後、強誘電体材料を容量絶縁膜とする容量素子の下部電極21を開口部20上を含むように形成する。開口部20を形成するための層間絶縁膜19のエッチングはエッチングストッパー膜18で容易に停止できるので、下地層間絶縁膜17がエッチングされない。こうして酸素バリア膜16を縮小し、容量素子占有面積を小さくできる。

(もっと読む)

半導体記憶装置

【課題】データ読出し動作において、不要なリストア動作を省略し、破壊されたデータのリストア時間を従来よりも長くすることができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、プレート駆動信号PDSと、データ書込みを示すライト信号WRITEと、センスアンプから外部へのデータ読出しまたは外部からセンスアンプへのデータ書込みの実行可能期間の終了を示す動作終了信号PRECHとを受け取り、ライト信号および動作終了信号に基づいてプレート駆動信号を有効または無効にするプレート制御回路PCCとを備え、プレート制御回路は、実行可能期間にプレート駆動信号を有効にし、プレート制御回路は、実行可能期間内に1度もライト信号が活性化されなかったときには実行可能期間終了時にプレート駆動信号を無効にし、実行可能期間内に少なくとも1度ライト信号が活性化されたときにはプレート駆動信号を有効にしたままにする。

(もっと読む)

半導体装置の製造方法

【課題】製造工程における強誘電体キャパシタの劣化を抑制する。

【解決手段】半導体装置の製造方法は、半導体基板100の上方に、Pbを含む強誘電体120を有するキャパシタ層を形成し、前記キャパシタ層をRIEにより加工して、前記強誘電体を有するキャパシタを形成し、Pb、酸素および鉛単体酸化物を含む雰囲気で、前記キャパシタを熱処理し、前記熱処理の際に、前記雰囲気内における前記鉛単体酸化物の分圧は、前記強誘電体内におけるPbにより生じる前記鉛単体酸化物の蒸気圧以上、かつ前記雰囲気内における前記鉛単体酸化物の蒸気圧以下である。

(もっと読む)

強誘電体メモリー装置の製造方法

【課題】強誘電体メモリー装置の歩留りを向上させる。

【解決手段】本発明の製造方法は、強誘電体キャパシタ3の上に第1層間絶縁膜12を形成し上部電極33に通じる下部コンタクトホールを形成する工程と、下部コンタクトホールの内側と第1層間絶縁膜12の上とに導電材料を成膜し第1層間絶縁膜12の上の導電材料をエッチングにより除去するとともに下部コンタクトホールの内側に導電材料からなる下部プラグ層42を形成する工程と、第1層間絶縁膜12の上に第2層間絶縁膜13を形成し第2層間絶縁膜13の上をCMP法で平坦化した後に第2層間絶縁膜13を貫通して下部プラグ層42に通じる上部コンタクトホール46をエッチングにより形成する工程と、上部コンタクトホール46の内側に下部プラグ層42に導通する上部プラグ層43を形成する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】良好な特性の半導体装置を良好な歩留りで製造可能な製造方法を提供する

【解決手段】半導体基板10A上に絶縁膜を形成する工程と、絶縁膜上に感光性材料51を塗布する工程と、半導体基板10Aの周辺部に形成された感光性材料51を除去する工程と、感光性材料51に対してプリベイクを行い、感光性膜52を形成する工程と、感光性材料51が除去された領域と離間するように、感光性膜52に対して露光を行う工程と、露光された感光性膜52に対して現像を行うことにより、レジストパターンを形成する工程と、レジストパターンをマスクとして、絶縁膜にコンタクトホールを形成する工程と、コンタクトホール内にプラグ導電部を形成する工程と、プラグ導電部上に強誘電体キャパシタを形成する工程と、強誘電体キャパシタに対して、酸素雰囲気中で熱処理を行う工程と、を含む。

(もっと読む)

半導体装置

【課題】 求められる特性が異なる複数のキャパシタを同一基板上に混載するには、さらなる工夫が必要とされる。

【解決手段】 下部電極、上部電極、及び両者の間に配置された誘電体膜を含む下層キャパシタが、半導体基板の上に配置されている。第1の層間絶縁膜が、第1のキャパシタを覆う。複数の上層キャパシタが、第1の層間絶縁膜の上に配置されている。上層キャパシタは、下部電極、上部電極、及び両者の間に配置された誘電体膜を含み、平面視において、下層キャパシタに重なる。半導体基板の上に、上層キャパシタに対応して複数のトランジスタ配置されている。トランジスタは、上層キャパシタとともにメモリセルを構成する。

(もっと読む)

41 - 60 / 791

[ Back to top ]