Fターム[5F083GA05]の内容

Fターム[5F083GA05]の下位に属するFターム

リーク電流の低下 (1,514)

Fターム[5F083GA05]に分類される特許

1,001 - 1,011 / 1,011

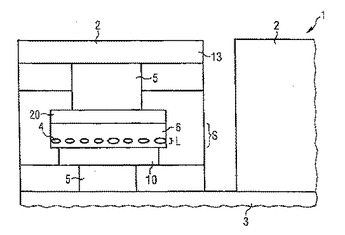

半導体集積メモリーおよび半導体集積メモリーの製造方法

本発明は、2つの電極(10,20)間に配置された記憶媒体(6)を備えた半導体集積メモリー(1)に関する。上記記憶媒体(6)は、例えば相変化媒体であってもよい。記憶媒体(6)は、電流によって第1状態または第2状態に設定される。その結果、情報項目を記憶させることができる。本発明によれば、材料(4)からなる不純物粒子が注入された面(L)が設けられている。その結果、記憶媒体における電流密度が局部的に上昇し、プログラミングのために必要とされるプログラミング電流を低減できる。その結果、相変化媒体を含むメモリー素子の電流消費を低減できる。したがって、相変化媒体を含むメモリー素子を、トランジスタなどの他の部品と共に、最小構造寸法で実施することができ、単一の半導体回路に集積することができ、別個のサブ回路に配置する必要がなくなる。  (もっと読む)

(もっと読む)

半導体集積回路装置

記憶回路STCと比較回路CPとを用いたメモリセルで構成されるメモリアレイにおいて、比較回路CPを構成する複数のトランジスタのうち、ゲート電極がサーチ線に接続されるトランジスタのソースまたはドレインのいずれか一方の電極を高電圧にプリチャージされる方のマッチ線HMLrに接続する。また、マッチ線判定回路MDrを低電圧にプリチャージされるマッチ線LMLrに配置して、情報の比較結果に応じてこのマッチ線に発生した比較信号電圧を弁別する。このようなメモリアレイ構成と動作により、マッチ線対におけるサーチ線駆動雑音の影響を回避しつつ、低電力かつ高速に比較動作を行うことができる。このため、検索動作を高速に行うことが可能な低電力コンテント・アドレッサブル・メモリを実現することができる。 (もっと読む)

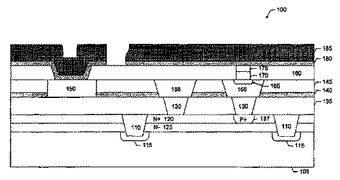

ゲートによるジャンクションリーク電流を使用してフラッシュメモリをプログラミングする技術

メモリ素子をプログラムする方法と、ゲートによる接合リーク電流を利用してプログラムされたメモリ素子を提供する。本素子は、基板上のフローティングゲートと、基板内の活性領域と、フローティングゲートに隣接する第2ゲートを少なくとも含むことができる。本方法は、第1ゲートにバイアスをか印加することによってフローティングゲートの下の基板内に反転領域を生成する工程と、第2ゲートの付近に臨界電界を生成する工程を含むことができる。臨界電界を生成する工程は、活性領域に第1ポジティブバイアスを印加する工程と、第2ゲートに第1ポジティブバイアスより小さいバイアスを印加する工程を含むことができる。本素子は、活性領域に印加されるゼロボルトより大きい第1バイアスと、第2ゲートに印加される第1バイアスより大きい第2バイアスをさらに含む。第1バイアスと第3バイアスは、フローティングゲートと選択ゲートの間において基板内にリーク電流を生成するために選択される。  (もっと読む)

(もっと読む)

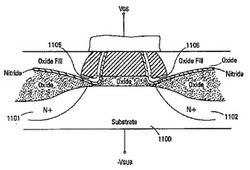

自己整合型電荷分離構造NROMフラッシュメモリ

【課題】電荷捕獲領域が重ならずにセルを小さくすることが可能なトランジスタを提供する。

【解決手段】窒化物リードオンリーメモリ(NROM)セルは、窒化物層を有し、前記窒化物層は、トランジスタの中心部の下方に配置されない。前記窒化物層を有するゲート絶縁層は、2つの部分を有する。各部分は、構造分離された(structurally defined and separated)電荷捕獲領域を有する。電荷は、トランジスタの動作方向に応じて、ある特定の捕獲領域に蓄積される。前記ゲート絶縁層の前記2つの部分は、ポリシリコンゲート構造体の中間部分から外側部分を分離する。

(もっと読む)

相変化メモリ、相変化メモリアセンブリ、相変化メモリセル、2D相変化メモリセルアレイ、3D相変化メモリセルアレイおよび電子部品

本発明の相変化メモリは、相変化材料から成るメモリ材料層と相互に距離を置いて配置された第1および第2電気接点とを有し、この接点を通って電流信号がメモリ材料層のスイッチングゾーンを横断する。前記電流信号を利用して結晶相とアモルファス相の間の相変化、したがってスイッチングゾーンの相変化材料の抵抗変化を誘発する。本発明の相変化メモリの新しい概念はスイッチングゾーンが第1および第2電気接点の間の相変化メモリの水平方向に沿って配置され、電流信号が前記水平方向に沿ってスイッチングゾーンを通って伝導される。 (もっと読む)

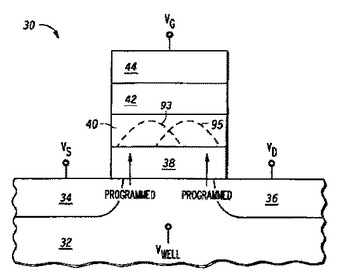

個別電荷蓄積素子を有するメモリのプログラミング

不揮発性メモリ(100)は、個別電荷蓄積素子(40)を有するトランジスタ群(30)から成るアレイを含む。トランジスタに対しては、2ステップ書き込み方法(60)を使用して書き込みを行ない、この方法では、第1ステップ(68)が低ゲート電圧によるホットキャリア注入(hot carrier injection:HCI)書き込みである。第2ステップ(78)を幾つかのメモリセルに対して選択的に利用して注入電荷分布を変え、トランジスタメモリセル内部の各メモリビットの間の電荷分布間隔を大きくする。書き込みを行なう第2ステップは、書き込み操作に長い余分な時間が加わることなく行われる。一の例では、第1ステップにおいて電子を注入し、そして第2ステップにおいてホールを注入する。2つのステップを実行して分布が形成される結果、蓄積媒体の中心部分の電子電荷が取り除かれる。  (もっと読む)

(もっと読む)

ビア開口部中に形成されるポリマーメモリデバイス

本発明は、ビア内にポリマーメモリデバイスを製造する方法に関する。この方法は、少なくとも1つの金属を含む層をその上に備える半導体基板を提供するステップと、この金属を含む層中に少なくとも1つの銅コンタクトを形成するステップと、銅コンタクト上に少なくとも1つの絶縁層を形成するステップと、絶縁層に少なくとも1つのビアを形成し、銅コンタクトの少なくとも一部を露出するステップと、ビアの下側部分にポリマー材料を形成するステップと、ビアの上側部分にトップ電極材料層を形成するステップとを含む。  (もっと読む)

(もっと読む)

半導体装置

【課題】 消費電力が小さく、かつ動作速度が速い半導体装置を提供する。

【解決手段】 DRAMコアセルのリードゲート1は、各々のゲートがそれぞれノードN1,N2を介してビット線BL,/BLに接続されるNチャネルMOSトランジスタ61,63と、各々のゲートがともに列選択信号CSLRを受けるNチャネルMOSトランジスタ2,3とを含み、MOSトランジスタ2,3のゲート酸化膜はMOSトランジスタ61,63のゲート酸化膜よりも薄い。したがって、列選択信号CSLRの振幅電圧の低電圧化を図ることができる。

(もっと読む)

半導体集積回路装置

【課題】 入力回路の簡素化と製品管理の取り扱いを簡便にしつつ、実質的な低消費電力化及び素子の微細化に適合して安定した入出力伝達特性を実現できる入力回路を備えた半導体集積回路装置を提供する。

【解決手段】 外部端子から供給される入力信号を受ける差動増幅回路に第1と第2の動作電圧を第1と第2のスイッチMOSFETを介して供給するようにし、バイアス電圧発生回路により上記入力信号が上記第1と第2の動作電圧の中心電圧付近にあるときに上記第1と第2スイッチMOSFETをオン状態にし、その入力信号が継続的に一定期間上記第1電圧又は第2電圧にあるときには、それに対応した出力信号を形成すべく上記第1又は第2スイッチMOSFETのいずれか一方をオン状態に他方をオフ状態にする制御電圧を形成し、上記第1動作電圧と第2動作電圧に対応した第1振幅の入力信号と、上記第1動作電圧と第2動作電圧の間の所定の中間電圧に対応した第2振幅の入力信号の双方の供給を可能とする。

(もっと読む)

半導体記憶装置

【課題】 ゲート絶縁膜の劣化を防止すると共に、浮遊ゲート内のキャリアの電荷量を正確に制御できるようにする。さらに、書き込み時の消費電力を不要にする。

【解決手段】 開示されている半導体記憶装置は、浮遊ゲート6に一部分が接すると共に他部分がP型シリコン基板1に接するようにモット絶縁体7を設け、このモット絶縁体7に金属−絶縁相転移を生じさせる。そして、浮遊ゲート6に対してキャリアである電子の注入又は放出を行う場合、ゲート酸化膜5を通じてではなく、モット絶縁体7の金属相を通じてキャリアの注入又は放出を行う。

(もっと読む)

半導体記憶装置

【課題】 多ビットのデータを入出力可能であって、動作速度の遅延や消費電力の増大を抑えたDRAMを提供する。

【解決手段】 このDRAMでは、多数のグローバル入出力線対GIOがサブワードドライバ領域24間のメモリセルアレイ上を走る。ローカル入出力線対LIOはメモリサブブロック26ごとに複数に分割される。グローバル入出力線対GIOとローカル入出力線対LIOを接続するスイッチング素子30はセンスアンプ領域22上に分散して配置される。1つのローカル入出力線対LIOには複数のビット線対が共通に接続される。

(もっと読む)

1,001 - 1,011 / 1,011

[ Back to top ]