Fターム[5F083GA06]の内容

Fターム[5F083GA06]の下位に属するFターム

高抵抗化(SRAMのみ) (2)

Fターム[5F083GA06]に分類される特許

141 - 160 / 1,512

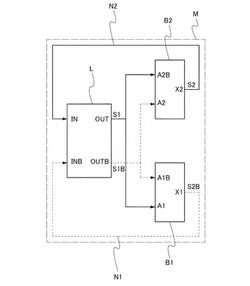

記憶装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な記憶装置、及び該記憶装置を有する半導体装置を提供する。

【解決手段】第1の入力端子、及び第1の入力端子の入力信号の反転信号が入力される第2の入力端子、並びに第1の信号が出力される第1の出力端子、及び第1の信号の反転信号が出力される第2の出力端子、を有するレベルシフタと、第1の信号が入力される第3の入力端子、及び第1の信号の反転信号が入力される第4の入力端子、並びに第3の出力端子を有する第1のバッファと、第1の信号の反転信号が入力される第5の入力端子、及び第1の信号が入力される第6の入力端子、並びに第4の出力端子を有する第2のバッファと、を有し、第1のバッファの第3の出力端子から出力される信号が、レベルシフタの第1の入力端子に入力され、第2のバッファの第4の出力端子から出力される信号が、レベルシフタの第2の入力端子に入力される。

(もっと読む)

固集積フラッシュメモリーセルストリング、セル素子、及びこの製造方法

【課題】優れた縮小化特性を有し、閾値電圧の散布を減らすことができるフラッシュメモリーセルストリング及びこの製造方法を提供する。

【解決手段】本発明は、フラッシュメモリーセルストリング及びこの製造方法に関する。前記フラッシュメモリーセルストリングは、多数のセル素子及び前記セル素子の端部に連結されるスイッチング素子を含む。前記セル素子は、半導体基板と、半導体基板に順次に積層される透過絶縁膜と、電荷貯蔵ノードと、コントロール絶縁膜と、制御電極とを備え、ソース/ドレーンが形成されないことを特徴とする。前記スイッチング素子は、セル素子に連結される側にソースまたはドレーンを含まないし、セル素子に連結されない側にソースまたはドレーンを含むが制御電極と重なり、又はまたは重ならないことを特徴とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

半導体装置

【課題】所望のタイミングでデータの評価、書き換えを行うことができる半導体装置を提供する。

【解決手段】フリップフロップ回路と、選択回路と、選択回路を介して前記フリップフロップ回路と電気的に接続する不揮発性記憶回路と、を含むレジスタ回路と、ビット線と、データ線と、を有し、データ線はフリップフロップ回路と電気的に接続し、ビット線は、選択回路を介して不揮発性記憶回路と電気的に接続し、選択回路は、データ線の電位またはビット線の電位に応じたデータを選択的に不揮発性記憶回路に格納する半導体装置。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1及び第2のノードを有する論理回路と、第1のノードに接続された第1の記憶回路と、第2のノードに接続された第2の記憶回路と、第1のノード、第2のノード、第1の記憶回路、及び第2の記憶回路に接続されたプリチャージ回路と、を有し、読み出しの際に、プリチャージ回路は、プリチャージ電位を第1のノード及び第2のノードに出力し、第1の記憶回路及び第2の記憶回路は、チャネルが酸化物半導体膜に形成されるトランジスタを含む記憶装置である。

(もっと読む)

記憶回路

【課題】短時間の電源停止により消費電力を抑えることができ、電源再開時において誤動作を引き起こすことなく初期化することのできる信号処理装置の記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性記憶部に記憶していたデータ信号を、不揮発性記憶部に保持する。不揮発性記憶部では、オフ電流が極めて小さいトランジスタを用いることによって、容量素子に保持されたデータ信号は長期間にわたり保持する。こうして、不揮発性記憶部は電源の供給が停止した間も論理状態を保持する。また電源停止時に容量素子で保持されたデータ信号は、電源再開時にはリセット回路を導通状態とすることで、誤動作を引き起こすことのない電位にする。

(もっと読む)

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のトランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電位を保持させることで行う。メモリセルの読み出しは、ビット線にプリチャージ電位を供給した後ビット線への電位の供給を止め、ビット線の電位がプリチャージ電位に保たれるか、または電位が下がるか、により行う。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜に酸素ドープ処理を行って、第1の絶

縁膜に酸素原子を供給し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに

、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半

導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された

酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳す

る領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

記憶素子の駆動方法及び半導体装置の駆動方法

【課題】記憶素子(DRAM)の保持情報の多値化を簡便に行うこと。

【解決手段】記憶素子(DRAM)が有するトランジスタがオン状態の期間において、当該記憶素子(DRAM)に対して情報の書き込みを行う配線(ビット線)の電位を変動させることで、当該記憶素子(DRAM)が有する容量素子に蓄積される電荷量を制御する。これにより、当該記憶素子(DRAM)を有する半導体装置の構造を複雑化せずとも記憶素子(DRAM)の保持情報を多値化することが可能である。

(もっと読む)

半導体装置

【課題】高速動作、低消費電力である半導体装置の提供。

【解決手段】結晶性のシリコンをチャネル形成領域に有する第1のトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子である第2のトランジスタとを有する。第2のトランジスタは第1のトランジスタを覆う絶縁膜上に位置する。第1及び第2のトランジスタは、ソース電極又はドレイン電極を共有している。上記絶縁膜は、加熱により一部の酸素が脱離する第1の酸化絶縁膜と、酸素の拡散を防ぎ、なおかつ当該第1の酸化絶縁膜の周囲に設けられた第2の酸化絶縁膜とを有し、第2のトランジスタが有する酸化物半導体膜は、上記第1の酸化絶縁膜に接し、かつチャネル形成領域である第1の領域と、第1の領域を挟み、第1及び第2の酸化絶縁膜に接する一対の第2の領域とを有する半導体装置。

(もっと読む)

半導体記憶装置

【課題】単位面積あたりのメモリモジュールの記憶容量を増加させる。また、消費電力の小さなメモリモジュールを提供する。

【解決手段】半導体装置は、ビット線と、二以上のワード線と、トランジスタおよびキャパシタからなるサブメモリセルを二以上有するメモリセルと、を有する。トランジスタのソースまたはドレインの一方がビット線と接続し、トランジスタのソースまたはドレインの他方がキャパシタと接続し、トランジスタのゲートがワード線の一と接続し、キャパシタの容量が各サブメモリセルで異なる。

(もっと読む)

半導体装置

【課題】電源電圧の供給を停止しても、論理回路部間の接続関係、又は各論理回路部内の回路構成を維持できる半導体装置を提供する。また、論理回路部間の接続関係の変更、又は各論理回路部内の回路構成の変更を高速で行うことができる半導体装置を提供する。

【解決手段】再構成可能な回路において、回路構成や接続関係等のデータを記憶する半導体素子に酸化物半導体を用いる。特に、半導体素子のチャネル形成領域に、酸化物半導体が用いられている。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1乃至第4のノードを有する論理回路と、第1のノード、第2のノード、及び第3のノードと接続された第1の制御回路と、第1のノード、第2のノード、及び第4のノードと接続された第2の制御回路と、第1のノード、第1の制御回路、及び第2の制御回路に接続された第1の記憶回路と、第2のノード、第1の制御回路、及び第2の制御回路に接続された第2の記憶回路と、を有する記憶装置である。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性半導体装置の高集積化を図ることのできる技術を提供する。

【解決手段】スイッチ用nMIS(Qs)のスイッチゲート電極SGと、スイッチ用nMIS(Qs)にワード線に対して交差する方向に沿って隣接するメモリ用nMIS(Qm)のメモリゲート電極MGとの間に、スイッチ用nMIS(Qs)のソース/ドレイン領域SDHとして機能し、同時にメモリ用nMIS(Qm)のドレイン領域Dとして機能する半導体領域を形成し、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)側のソース/ドレイン領域SDHを構成する半導体領域の形状と、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)と反対側(ビット線側)のソース/ドレイン領域SDLを構成する半導体領域の形状とを非対称とする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】微細化によっても順方向電流が減少することが無いようにする。

【解決手段】実施形態は、第1の配線と、その上に積層されたメモリセルと、その上に形成された第2の配線とを有するセルアレイ層を備え、メモリセルが、電流制御素子、可変抵抗素子及びこれらの間に配置されたシリサイド用金属層を有する。第1の配線又は第1の配線層を形成し、その上に電流制御素子を形成する半導体層、シリサイド用金属層及び可変抵抗素子を形成する可変抵抗素子層を順次形成する。可変抵抗素子層及びシリサイド用金属層を半導体層に達するまで第1のエッチングにより選択的に除去し、少なくとも露出したシリサイド用金属層の側面を覆うように第1の保護層を形成し、選択的に除去した部分に対応する半導体層の部分を第2のエッチングにより選択的に除去し、可変抵抗素子、シリサイド用金属層及び半導体層を覆うように第2の保護層を形成する。

(もっと読む)

半導体記憶装置

【課題】低電圧化を可能にする。

【解決手段】実施形態は、第1の配線と、その上に積層されたメモリセルと、その上に第1の配線と交差するように形成された第2の配線とを有するセルアレイ層を備え、メモリセルが極性の異なる電気信号が印加されることにより電気的書き換えが可能な可変抵抗素子及び可変抵抗素子に双方向の電流を流す電流制御素子を直列に接続してなる。電流制御素子は、i型半導体とその両側に接する第1及び第2導電型半導体とを有する。第2導電型半導体中の第2の不純物の拡散長は第1導電型半導体中の第1の不純物の拡散長より長く、第1導電型半導体とi型半導体との接合部に、第2導電型半導体とi型半導体との接合部よりも多くのインパクトイオンを発生させるインパクトイオン化促進部が形成される。

(もっと読む)

半導体装置

【課題】フローティングボディにデータを記憶するメモリセルを備えた半導体装置において、トリガ素子となる能動素子を設けなくともメモリセルの導通、非導通状態を確実に制御する。

【解決手段】ビット線BLと、ワード線WLと、第1の端子がビット線に接続され、第2の端子がワード線に接続されたメモリセル66と、メモリセルに対するデータの書込み時に、書込みデータの如何に係わらず、ビット線とワード線を選択し、メモリセルを導通させた後、ビット線の電圧レベルを書込みデータに応じた電圧レベルに設定し、メモリセルにデータを書込む制御回路を備える。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、単位面積あたりの記憶容量を増加させる。

(もっと読む)

記憶素子及び記憶装置

【課題】電力の供給が停止した後もデータを保持することができる、新たな構成の記憶素子を提供することを目的の一とする。

【解決手段】記憶素子は、ラッチ回路と、第1の選択回路と、第2の選択回路と、第1の不揮発性記憶回路と、第2の不揮発性記憶回路と、を有する。また、第1の不揮発性記憶回路及び第2の不揮発性記憶回路は、それぞれトランジスタ及び容量素子を有する。第1及び第2の不揮発性記憶回路のそれぞれが有するトランジスタは、チャネルが酸化物半導体膜に形成されるトランジスタである。当該トランジスタは、オフ電流が極めて低いため、トランジスタと容量素子の接続点であるノードにデータが入力された後、トランジスタがオフ状態となり、電源電圧の供給が停止しても、長期間にわたりデータを保持することができる。

(もっと読む)

141 - 160 / 1,512

[ Back to top ]