Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

2,181 - 2,200 / 2,405

半導体記憶装置及びその製造方法

【課題】 相変化メモリ素子を備える半導体記憶装置の集積密度を上げる。

【解決手段】 相変化メモリセルは、直列に接続された相変化メモリ素子21〜23とダイオードとから構成される。隣接する2つの相変化メモリセルは、共通の活性領域48内に順次に形成されたn型半導体層8及びp型半導体層9とで形成されたダイオードを有し、且つ、双方のビット線コンタクトプラグは、n型半導体層の下層に配置される高濃度n型半導体層7に接続された、サイドウオール膜26を有する共通のビット線コンタクトプラグ27bで構成する。

(もっと読む)

不揮発性メモリ装置ならびにそのプログラム方法および読取り方法

【課題】共通ソースラインを除去し、2つのメモリブロックがソース選択ラインを介して電圧の印加を受けるソース選択トランジスタを共有して、チップサイズを減らす不揮発性メモリ装置ならびにそのプログラム方法および読取り方法を提供する。

【解決手段】複数のメモリブロックを含んでなる不揮発性メモリ装置において、複数のメモリブロックは、2つのメモリブロックごとに、ソース選択ラインを介して電圧の印加を受けるソース選択トランジスタを共有して構成される。

(もっと読む)

不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法

【課題】

マクロサイズを小さく抑えて、更なる高集積化を進めることが可能な不揮発性半導体記憶装置を提供する。

【解決手段】

不揮発性半導体記憶装置は、半導体基板1と複数のメモリセル10a、10bとを具備する。半導体基板1は、複数の溝6を有する。複数のメモリセル10a、10bは、溝6の内面に沿い、溝6の深さ方向に一側面17a、17bにつき二以上並んでいる。複数のメモリセル10a及び10bは、ソースとして機能する第1拡散層7及び9aと、ドレインとして機能する第2拡散層9a及び8とを備えていても良い。その場合、第1拡散層7及び9aと第2拡散層9a及び8とは、溝6での深さ方向の高さが異なる。

(もっと読む)

電気スイッチおよびそれを用いた記憶素子

金属が添加された強誘電体基板と、前記強誘電体基板に設置された一対の電極と、前記強誘電体基板の一部の分極の方向を変化させ得る電界印加部とを備えている。  (もっと読む)

(もっと読む)

デンドリマーを用いるメモリ素子

【課題】不揮発性特性を有し、高集積度および低消費電力の特性を実現して製造工程が単純であるうえ、製造コストが低いメモリ素子を提供する。

【解決手段】上部電極10と下部電極30との間に有機材料層20を含むメモリ素子100であって、有機材料層20が、少なくとも1つの電子供与基(electron donating group)および少なくとも1つの電子受容基(electron accepting group)を有するデンドリマーを含む。

(もっと読む)

半導体メモリ

【課題】 メモリセルの占有面積を小さくした強誘電体メモリを提供する。

【解決手段】 強誘電体メモリは、セルトランジスタN0とセルトランジスタに一端が接続される強誘電体容量C0とをそれぞれ有する複数のメモリセルCELLと、セルトランジスタN0にそれぞれ接続される複数のワード線WLと、ワード線と交差し強誘電体容量の他端に接続される複数のプレート線PLと、セルトランジスタに接続される複数のローカルビット線LBLと、ローカルビット線に選択的に接続されるグローバルビット線GBLとを有する。更に、強誘電体メモリは、読み出し時にローカルビット線の電位を非選択プレート線と同等の電位に維持しながら前記メモリセルによるローカルビット線への電荷量を検出するセンスアンプユニットSAUを有する。

(もっと読む)

メモリ素子及びその製造方法

【課題】コントロールゲートとフローティングゲートを垂直形態で構成し、セルを小さくし、高カップリング比を実現し、プログラミング時電圧を低減したスプリットゲートフラッシュEEPROMとその製造方法を提供し、コントロール及びフローティングゲートを一部オーバーラップして消去特性を向上する。

【解決手段】トレンチを備えた半導体基板と、トレンチ両側壁に形成したトンネリング酸化膜と、トンネリング酸化膜上のトレンチ両側壁に独立に順次形成したフローティングゲート、誘電体膜及びコントロールゲートと、フローティングゲート、誘電体膜及びコントロールゲート側壁に形成したバッファ誘電体膜と、トレンチ底面半導体基板に形成したソースジャンクションと、ソースジャンクションに電気接続し、バッファ誘電体膜間のトレンチ内に形成したソース電極と、トレンチを除く半導体基板表面に形成したドレインジャンクションを有する。

(もっと読む)

半導体記憶装置

【課題】素子の微細化(高集積化)と信頼性の高い安定した高速メモリ動作ができ、2ビット以上の記憶保持ができる半導体記憶装置を提供する。

【解決手段】半導体基板10上に第1,第2の拡散層領域17,18を形成し、その第1,第2の拡散層領域17,18を連結するようにチャネル形成領域31を形成する。上記チャネル形成領域31上にゲート絶縁膜12を形成し、そのゲート絶縁膜12上にゲート電極13を形成する。また、上記ゲート絶縁膜12およびゲート電極13の両側の側壁に電荷保持体61,62を形成する。上記チャネル形成領域31にカーボンナノチューブを用いる。

(もっと読む)

不揮発性メモリデバイスの電荷注入方法

【課題】いわゆるNAND型MONOSメモリデバイスにおいて、1つのメモリトランジスタに対するデータの書き込みと消去をビット単位で任意に行うことを可能にする。

【解決手段】書き込みにおいては、選択されたメモリトランジスタの電荷蓄積膜(ONO膜)30の第1局部と第2局部に独立に、いわゆるCHE注入により電子を注入する(第1および第2の電荷注入ステップ)。一方、消去においては、第1局部(A部)に対する電子の注入時にドレインとして機能するソース・ドレイン領域22側で、バンド−バンド間トンネル電流に起因したホールを発生させ、これをA部に注入し、注入したホールによって、A部に注入されている電子の少なくとも一部を電気的に相殺する(第3の電荷注入ステップ)。第3の電荷注入ステップにおいて第2局部(A部と反対側の局部)にホールを注入する場合はソースとドレインの機能を入れ替える。

(もっと読む)

不揮発性半導体メモリ

不揮発性のメモリセルトランジスタは、ドレインからソースのみに電流が流れ、かつソース側のみで電荷を交換する指向性を有している。ワード線に接続される一対のメモリセルトランジスタのソースとドレインおよびドレインとソースとがそれぞれ接続されている。データの書き換え動作中に、一対のメモリセルトランジスタのソースおよびドレインには、逆の電圧が印加される。メモリセルトランジスタの指向性により、電荷蓄積層に対する電荷交換は、ソース領域のみで行われる。したがって、一方のメモリセルトランジスタのデータのみを書き換えできる。この結果、メモリセルサイズを増加させることなく、メモリセル毎にデータを書き換えできる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置、その製造方法、その書き込み方法、その読み出し方法、記録媒体並びに半導体記憶装置

【課題】電荷捕獲量の調節を容易且つ確実に行い、情報ばけ等の不都合の発生を防止し

て所望の多値情報を記憶する。

【解決手段】ソース領域3−ドレイン領域4間のチャネル領域Cとゲート電極6との間

に、ゲート酸化膜11、シリコン窒化膜12、シリコン酸化膜13、シリコン窒化膜14

、シリコン酸化膜15、シリコン窒化膜16及びシリコン酸化膜17が順次積層されてな

る電荷捕獲膜5が配されて半導体記憶装置が構成される。ここで、各窒化膜12,14,

16とその下層の各酸化膜11,13,15,17との間に存するトラップに電荷を蓄積

することで、4値("00","01","10","11")の情報が記憶される。

(もっと読む)

制御可能なナノメカニカルメモリ素子

メモリ装置は、区別可能な双安定状態を振幅変調下で呈するメカニカル素子を備える。これらの状態は、所定周波数の駆動信号の適用によって、動的に双安定性となるか多安定性となる。ヒステリシス効果に関連した素子の固有共振は、区別可能な複数の状態を特定の周波数範囲に亘って生じる。共通コンタクト上に設けられた異なる周波数範囲に対応する多様な素子を持つ複数の装置は、改良された密度で形成される。これらの装置は、起磁式、容量式、圧電式及び/又は光学式方法によって励起され、そして読み取られる。これらの装置は、平面方位付けされるか面外方位付けされて、3次元メモリ構造を可能にする。DCバイアスが、周波数応答をシフトして、素子の状態を弁別するための代替法を可能にすることに使用される。 (もっと読む)

不揮発性強誘電体メモリ装置

【課題】 本発明は不揮発性強誘電体メモリ装置に関し、強誘電体の分極状態に従いメモリセルのチャンネル抵抗が変化する特性を利用して不揮発性メモリセルの読取り/書込み動作を制御する技術を開示する。

【解決手段】

このような本発明は、ボトムワードラインの上部に絶縁層を形成し、絶縁層の上部にN型ドレイン領域、P型チャンネル領域及びN型ソース領域でなるフローティングチャンネル層を形成し、フローティングチャンネル層の上部に強誘電体層を形成し、強誘電体層の上部にワードラインを形成し、強誘電体層の極性に従いチャンネル領域に誘導される抵抗状態を制御して、メモリセルアレイの読取り/書込み動作を制御することになる。

(もっと読む)

不揮発性記憶素子、その製造方法及び動作方法

【課題】不揮発性記憶素子、その製造方法及び動作方法が開示される。

【解決手段】この素子は、基板上にゲート絶縁膜を介在して形成された浮遊ゲートと、前記浮遊ゲート上に形成されたトンネル絶縁膜と、前記ゲート絶縁膜を通じる電荷の注入を誘導する選択ゲート電極と、前記トンネル絶縁膜を通じる電荷のトンネリングを誘導する制御ゲート電極と、を含む。前記選択ゲート電極は前記制御ゲート電極と絶縁されている。本発明による記憶素子は浮遊ゲート上に選択ゲート電極及び制御ゲート電極を形成して、各ゲート電極に電圧を印加することによって書き込み及び消去が可能である。

(もっと読む)

ゲート制御ダイオードを使用するメモリ・セルおよびこれの使用方法、半導体構造

【課題】改良型3T1Dメモリ・セルを提供する。

【解決手段】メモリ・セルは、(1)第1の端子がビットラインに結合され、制御端子が第1の制御線に結合されている書込みスイッチ1325と、(2)2端子半導体デバイスの第1の端子が書込みスイッチの第2の端子に結合され、第2の端子が少なくとも1つの第2の制御線に結合され、第2の端子に対する第1の端子の電圧が閾値電圧を超えるときのキャパシタンスが閾値電圧を超えないときのキャパシタンスよりも大きくなる2端子半導体デバイス1330と、(3)制御端子が第2の制御線に結合され、第1の端子がビットラインに結合されている読出し選択スイッチ1340と、(4)制御端子がゲート制御ダイオードの第1の端子と書込みスイッチの第2の端子とに結合され、第1の端子が読出し選択ゲートの第2の端子に結合され、さらに、第2の端子が接地されている読出しスイッチ1345と、を備える。

(もっと読む)

チャージトラップインシュレータメモリ装置

【課題】ナノスケールチャージトラップインシュレータメモリ装置において維持特性を向上させ、多数のセル絶縁層を用いて多数のチャージトラップインシュレータセルアレイが垂直方向に積層してセル集積容量を高める技術を開示する。

【解決手段】チャージトラップインシュレータに格納されたデータがビットラインに出力される直列に連結された多数のメモリセルと、第1の選択信号の状態に従いビットラインと前記多数のメモリセルを選択的に連結する第1のスイッチング素子と、第2の選択信号の状態に従いセンシングラインと複数個のメモリセルを選択的に連結する第2のスイッチング素子とを含み、チャージトラップインシュレータの極性に従い抵抗が変化するP型フロートチャンネルと、P型フロートチャンネルの両側に形成されたP型ドレイン領域及びP型ソース領域とを含む。

(もっと読む)

台形のビット線を有するメモリ装置、およびその製造方法

メモリ装置(100)およびその製造方法が提供される。メモリ装置(100)は、半導体基板(110)と、半導体基板(110)に配置される電荷トラップ誘電体スタック(116、118、120)とを含む。ゲート電極(122)が電荷トラップ誘電体スタック(116、118、120)上に配置されており、ここでゲート電極(122)は半導体基板(110)の一部(114)内でチャネル(124)を電気的に画定する。メモリ装置(100)は、1組のビット線(112)を含み、ビット線は下方部分と、実質的に台形の上方部分とを有する。  (もっと読む)

(もっと読む)

半導体記憶装置とその製造方法

【課題】DRAMのメモリセルを構成するトランジスタとして良好な特性を持ち、且つ微細化にも好適な構成の半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体基板11と、この半導体基板11上に形成された素子分離領域28と、この素子分離領域28の間の前記半導体基板上に形成され凸部を有する素子形成領域30と、この素子形成領域30の凸部に形成されたチャネル部を有するトランジスタTraと、このトランジスタTraに接続されて前記半導体基板内または半導体基板上に形成されたキャパシタCt、Csとを具備し、前記素子形成領域30の凸部は前記トランジスタTraのチャネル幅方向に沿って互いに対面する第1、第2斜面とこの第1、第2斜面間に形成された上面とを有し、この上面のチャネル幅方向の幅が60nm以下で、かつ前記第1、第2斜面の延長で作られる頂角が鋭角であることを特徴とする半導体記憶装置。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】書き込み電流の低減と微細化に適したMTJ素子の形状を提案する。

【解決手段】本発明の例に関わるMTJ素子は、磁化方向が固定される第1強磁性層と磁化方向が磁場に応じて変化する第2強磁性層とを備える。第2強磁性層は、長軸方向を持つ本体部11aと、本体部11aから長軸とは異なる方向に突出する1つの突出部11bとから構成される。

(もっと読む)

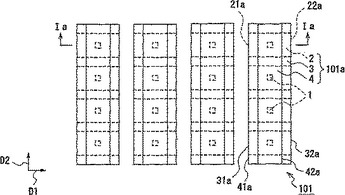

強誘電体メモリ装置

この発明は、メモリセルトランジスタとメモリセルキャパシタとからなるメモリセルを複数有する強誘電体メモリ装置(101)において、各メモリセルキャパシタ(101a)を、各メモリセルキャパシタ毎に独立した下部電極(2)と、該下部電極(2)上に形成された強誘電体層(3)と、該強誘電体層(3)上に形成され、複数が共通に接続されてプレート電極を形成する上部電極(4)とから構成し、上部電極の幅を、強誘電体層の幅よりも狭くしたものである。この発明に係る強誘電体メモリ装置では、上部電極の幅を強誘電体層の幅より小さくしたことにより、上部電極と下部電極との間での電流リークを防止することができ、これにより、上部電極と下部電極との間での電流リークの発生を招くことなくメモリセルキャパシタの配置間隔を縮小して、より小さいメモリセルサイズを実現することができる。  (もっと読む)

(もっと読む)

2,181 - 2,200 / 2,405

[ Back to top ]