Fターム[5F083GA10]の内容

Fターム[5F083GA10]に分類される特許

181 - 200 / 1,175

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

半導体装置、及び半導体装置の制御方法。

【課題】簡便な半導体装置の評価試験を実現する。

【解決手段】半導体装置10は、それぞれ内部信号MAを生成する第1及び第2のコアチップCC0,CC1を備え、第1及び第2のコアチップCC0,CC1のそれぞれに、貫通電極を介して他方のコアチップとスパイラル接続された第2及び第3のノードN2,N3を設け、この第2及び第3のノードN2,N3を介して、観測対象の内部信号MAを外部に出力することを技術思想とするものである。こうして出力される複数の内部信号MAを外部のテスター等によって観測することで、各コアチップの評価試験を並列に行える。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】メモリセルが3次元的に積層された不揮発性半導体記憶装置で、メモリセルの投影面積を小さくすることができ、従来の平面型のフローティングゲート構造と類似の構造の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、シート状のチャネル半導体膜111の高さ方向に複数のメモリセルMCを有するメモリストリングが基板上にほぼ垂直に配置される。フローティングゲート電極膜109は、第2の方向に延在し、トンネル誘電体膜110を介してチャネル半導体膜111の第1の主面上に形成される。制御ゲート電極膜103は、第1の方向に延在する共通接続部1031と、共通接続部1031から第2の方向に突出し、フローティングゲート電極膜109の上部または下部に電極間絶縁膜108を介してメモリセルMCごとに設けられる電極構成部1032と、を有する。

(もっと読む)

不揮発性メモリ装置

【課題】 パストランジスタ間の空間確保が可能な不揮発性メモリ装置を提供する

【解決手段】 不揮発性メモリ装置100が備える行デコーダ120は、パストランジスタ部123_L、123_Rを含む。パストランジスタ部123_L、123_Rは、メモリブロック110の左右に配列される。ブロック選択信号BLKWL1によって共通ゲートを形成するパストランジスタ端Pass TR 0とパストランジスタ端Pass TR 8とは、選択的に活性化される第1駆動信号ラインSI1及び第2駆動信号ラインSI2によって独立して駆動される。互に異なるブロック選択信号BLKWLによって駆動されるパストランジスタは、1つの活性領域の上に形成され得る。これにより、1つの活性領域の上に2つのパストランジスタを形成する場合、パストランジスタ部123_L、123_Rのチャンネル方向の大きさを減らすことができる。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においてリードデータの有効幅(ウィンドウ幅)を十分に確保する。

【解決手段】積層された複数のコアチップCC0〜CC7と、コアチップを制御するインターフェースチップIFとを備える。コアチップのそれぞれは、メモリセルアレイ70と、データ用の貫通電極TSV1と、メモリセルアレイ70から読み出されたリードデータをデータ用の貫通電極TSV1に出力する出力回路RBUFOとを備える。コアチップにそれぞれ設けられたデータ用の貫通電極TSV1は互いに共通接続され、コアチップにそれぞれ設けられた出力回路RBUFOはインターフェースチップIFより供給されるリードクロック信号RCLKDDに応答して活性化される。これにより、各コアチップの動作速度にばらつきが存在する場合であってもデータバス上でリードデータの競合が生じることがない。

(もっと読む)

側壁構造化スイッチャブル抵抗器セル

【課題】抵抗を大きくして感知されやすくするとともに、リセット電流を小さくし、製造中の損傷も抑制できる抵抗率スイッチング素子を提供する。

【解決手段】第1の伝導性電極28を形成するステップと、第1の伝導性電極28の上に絶縁構造13を形成するステップと、絶縁構造の側壁上に抵抗率スイッチング素子14を形成するステップと、抵抗率スイッチング素子14の上に第2の伝導性電極26を形成するステップと、第1の伝導性電極28および第2の伝導性電極26の間に抵抗率スイッチング素子14と直列にステアリング素子を形成するステップと、を含み、第1の伝導性電極28から第2の伝導性電極26への第1の方向における抵抗率スイッチング素子14の高さTは第1の方向に垂直な第2の方向における抵抗率スイッチング素子14の厚さIより大きい。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、酸化シリコン膜上に、酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている非晶質酸化物半導体層を形成し、該非晶質酸化物半導体層上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体層の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体層を形成する。

(もっと読む)

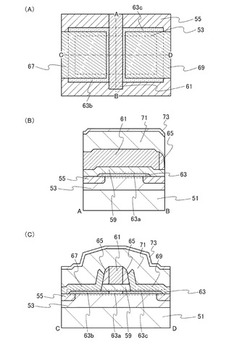

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

有機分子メモリおよびその製造方法

【課題】メモリセルに流れる電流を制御し、安定した動作と高い信頼性を備える有機分子メモリを提供する。

【解決手段】第1の電極と、第1の電極と異なる材料で形成される第2の電極と、第1の電極と第2の電極との間に設けられる有機分子層であって、有機分子層を構成する抵抗変化型分子鎖の一端が第1の電極と化学結合し、抵抗変化型分子鎖の他端と第2の電極との間に空隙が存在する有機分子層と、を備える有機分子メモリ。

(もっと読む)

有機分子メモリ

【課題】電荷保持特性に優れた有機分子メモリを提供する。

【解決手段】実施の形態の有機分子メモリは第1の導電層と、第2の導電層と、第1の導電層と第2の導電層との間に設けられ、電荷蓄積型分子鎖または抵抗変化型分子鎖を含み、電荷蓄積型分子鎖または前記抵抗変化型分子鎖が縮合多環系の基を備える有機分子層と、を備えている。

(もっと読む)

半導体装置の製造方法

【課題】エッチング加工により高アスペクト比の構造体の形成が可能な半導体装置の製造方法を提供すること。

【解決手段】異なる材料からなる複数の膜を積層して少なくとも酸化シリコン膜を含む積層膜を形成する工程と、前記積層膜上にハードマスクパターンを形成する工程と、前記ハードマスクパターンをエッチングマスクに用いて前記積層膜を異方性エッチングして所定の形状の積層膜パターンを形成する工程と、前記ハードマスクパターンを除去する工程と、を含み、前記ハードマスクパターンは、第1ハードマスク層と第2ハードマスク層とが少なくとも1層ずつ以上積層されて構成され、前記第1ハードマスク層は、前記第2ハードマスク層よりもウェットエッチングによる剥離性が良い材料からなり、前記積層膜の直上には前記第1ハードマスク層が配置される。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去動作を的確に実行する。

【解決手段】

制御回路は、データ消去動作を実行する場合において、ドレイン側選択トランジスタ及びソース側選択トランジスタの少なくとも一方においてホールを発生させて柱状半導体層に供給して少なくとも第1電圧まで上昇させる。そして、複数のワード線のうちの第1のワード線に対し、第1電圧よりも小さい電圧を第1の期間の間印加する一方、第1のワード線とは別の第2のワード線に対し、第1電圧よりも小さい電圧を第1の期間とは異なる第2の期間の間印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】上側のメモリセルと下側のメモリセルとの間におけるデータリテンションのばらつきを低減できる不揮発性半導体記憶装置を提供する。

【解決手段】第1のメモリセルMC111は、第1のラインWL11の半導体基板SBと反対側に配されている。第2のラインBL11は、第1のメモリセルMC111を介して第1のラインWL11に交差する。第2のメモリセルMC211は、第2のラインBL11の半導体基板SBと反対側に配されている。第3のラインWL21は、第2のメモリセルMC211を介して第2のラインBL11に交差する。第1のメモリセルMC111は、第1の抵抗変化層R111と第1の整流層D111とを有する。第1の抵抗変化層R111は、カーボン系の材料で形成されている。第2のメモリセルMC211は、第2の抵抗変化層R211と第2の整流層D211とを有する。第2の抵抗変化層R211は、金属酸化物で形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】3次元に積層されたメモリセルトランジスタにおける誤動作を防止する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20と、半導体基板の上方に形成された第1導電層40と、第1導電層の上方に順に積層された第2導電層43、電極間絶縁膜53’、および第3導電層43と、一対の貫通ホール49の内面上、および一対の貫通ホールの下端を連結させる連結ホール50の内面上に形成されたブロック絶縁膜53と、電荷蓄積層54と、トンネル絶縁膜55と、半導体層SPと、一対の貫通ホールの間に位置し、第2導電層、電極間絶縁膜、および第3導電層を分断するスリット46内に埋め込まれた絶縁材59と、第2導電層および第3導電層の表面上に形成されたシリサイド層58と、を具備し、スリットの内面に沿った第2導電層と第3導電層との間の距離は、積層方向に沿った第2導電層と第3導電層との距離よりも大きい。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造工程数の削減が可能な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1、第2積層体、第1、第2半導体ピラー、第1、第2メモリ膜、接続部及び分断部を備えた不揮発性半導体記憶装置が提供される。第1、第2積層体は、第1軸に沿って積層された複数の第1、第2電極膜と、第1、第2電極膜間に設けられた第1、第2電極間絶縁膜と、をそれぞれ含む。第1、第2半導体ピラーは第1、第2積層体を第1軸に沿って貫通する。第2積層体は、第1積層体と並置される。接続部は第1、第2半導体ピラーを接続する。第1メモリ膜は、第1、第2電極膜と、第1、第2半導体ピラーとの間に設けられる。分断部は、第1、第2半導体ピラー間で第1、第2電極膜を分断し、接続部に接し、第1メモリ膜に用いられる材料を含む積層膜を含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリブロックを縮小化可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、半導体基板、メモリストリング、複数の第1導電層、第2導電層、及び第3導電層を有する。メモリストリングは、半導体基板に対して垂直方向に直列接続された複数のメモリセル、ダミートランジスタ、及びバックゲートトランジスタを有する。複数の第1導電層は、メモリセルのゲートと電気的に接続されている。第2導電層は、ダミートランジスタのゲートと電気的に接続されている。第3導電層は、バックゲートトランジスタのゲートと電気的に接続されている。第2導電層は、第3導電層と短絡している。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 チャネルにおける電子の移動度低下を抑制する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】

実施形態に係る不揮発性半導体記憶装置は、基板を持つ。基板上方には、絶縁膜及び電極膜が交互に積層された積層体が設けられている。前記積層体を貫き、前記積層体中に弗素を含むシリコンピラーが設けられている。前記シリコンピラーの前記積層体に対向する面上にトンネル絶縁膜が設けられている。前記トンネル絶縁膜の前記積層体に対向する面上には電荷蓄積層が設けられている。前記電荷蓄積層の前記積層体に対向する面上に前記電極膜と接するようにブロック絶縁膜が設けられている。前記シリコンピラー中に埋込部が設けられている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】安定した性能と高い生産性とを実現する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、メモリセルアレイ部と、第1平面内においてメモリセルアレイ部と並置されたコンタクト部と、を備えた不揮発性半導体記憶装置が提供される。メモリセルアレイ部は、積層体、半導体層、メモリ膜を含む。積層体は、第1平面に対して垂直な第1軸に沿って積層された複数の電極膜とそれらの間の電極間絶縁膜とを含む。半導体層は電極膜の側面に対向する。メモリ膜は電極膜と半導体層との間に設けられ電荷保持層を含む。コンタクト部は、コンタクト部絶縁層と複数のコンタクト電極とを含む。コンタクト部絶縁層は、コンタクト部絶縁膜と粒子とを含む。コンタクト電極はコンタクト部絶縁層を第1軸に沿って貫通する。コンタクト電極は電極膜に接続される。

(もっと読む)

半導体記憶装置

【課題】低消費電力且つ省スペースな半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、異なる抵抗状態によってデータを記憶する複数のメモリセルからなるメモリセル層を有するメモリセルアレイと、第1配線及び第2配線を介して前記メモリセルにアクセスするアクセス回路とを備え、メモリセルは、第1極性の所定の電圧が印加されると抵抗状態が第1抵抗状態から第2抵抗状態に遷移し、第2極性の所定の電圧が印加されると抵抗状態が第2抵抗状態から第1抵抗状態に遷移し、アクセス回路は、選択したメモリセルに接続された第1配線及び第2配線に前記メモリセルのアクセスに必要な電圧を印加する共に、非選択の前記メモリセルに接続された第1配線及び第2配線の少なくとも一方をフローティング状態にして、選択したメモリセルにアクセスすることを特徴とする。

(もっと読む)

不揮発性記憶装置

【課題】記憶容量の増大を図ることができる不揮発性記憶装置を提供する。

【解決手段】実施形態に係る不揮発性記憶装置は、第1の方向に延びる複数本のワード線を含むワード線配線層と、前記第1の方向に対して交差する第2の方向に延びる複数本のビット線を含むビット線配線層と、各前記ワード線と各前記ビット線との間に配置されたピラーと、を備える。前記ピラーは、電流を流すか否かを選択する電流選択膜と、前記電流選択膜に積層された複数枚の抵抗変化膜と、を有する。1枚の前記抵抗変化膜は、金属と、酸素又は窒素と、を含有し、残りの前記抵抗変化膜は、前記金属と、酸素又は窒素と、電気陰性度が前記金属の電気陰性度よりも高い高電気陰性度物質と、を含有する。そして、前記残りの抵抗変化膜における前記高電気陰性度物質の濃度は、前記抵抗変化膜間で相互に異なる。

(もっと読む)

181 - 200 / 1,175

[ Back to top ]