Fターム[5F083GA10]の内容

Fターム[5F083GA10]に分類される特許

221 - 240 / 1,175

半導体記憶装置

【課題】動作速度が高い半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、一方向に沿って相互に平行に配列された複数枚のゲート電極膜と、前記一方向に延び、前記複数枚のゲート電極膜を貫通する半導体部材と、前記ゲート電極膜と前記半導体部材との間に設けられた電荷蓄積膜と、を備える。前記ゲート電極膜における前記半導体部材に対向した端部には、前記一方向に沿って突出した凸部が設けられており、前記ゲート電極膜間の空間の一部は気体層となっている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】 セル面積の縮小が可能であり、かつ、最小加工寸法がメモリセルを構成する材料の膜厚に制限されない半導体記憶装置を提供すること。

【解決手段】 半導体記憶装置において、Y方向に延伸する複数のワード線WL1nの上方に、ゲート絶縁膜104、X方向に延伸するチャネル106、X方向に延伸する抵抗変化素子108を順に形成し、複数のワード線のそれぞれの上方に、チャネルの一部および抵抗変化素子の一部を配置する(MC11n)。係る構成により、セル面積を縮小し、かつ、設計の自由度を担保しうる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コストが低い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、絶縁膜及び電極膜が交互に積層された積層体を形成する工程と、前記積層体上に、サイズが相互に異なる複数のホールが形成されたハードマスクを形成する工程と、マスク材料を堆積させることにより、最も小さい前記ホールを閉塞させると共に、その他の前記ホールを小さくする工程と、前記マスク材料及び前記ハードマスクをマスクとしてエッチングを施すことにより、前記その他のホールの直下域において、各所定枚数の前記絶縁膜及び前記電極膜を除去して、コンタクトホールを形成する工程と、前記コンタクトホールを介してエッチングを施すことにより、前記電極膜の一部分を除去して隙間を形成する工程と、前記隙間内に絶縁材料を埋め込む工程と、前記コンタクトホール内に導電材料を埋め込む工程と、を備える。

(もっと読む)

半導体記憶装置

【課題】擬似的に記憶容量を増加させる。

【解決手段】ダミービット線領域において半導体基板に対して垂直方向に延びる一対の柱状部およびその連結部に沿って形成されるメモリストリングを構成する第1シリコンピラーと、シャント領域において半導体基板に対して垂直方向に延びる一対の柱状部およびその連結部に沿って形成されるメモリストリングを構成する第2シリコンピラーと、第1シリコンピラーおよび第2シリコンピラーの一対の柱状部の一方に接続され、メモリストリングの上方に形成されたソース線と、第1シリコンピラーの一対の柱状部の他方に接続され、ソース線と同レベルに形成された第1配線、および第2シリコンピラーの一対の柱状部の他方に接続され、ソース線と同レベルに形成された第2配線と、を具備し、第1配線はダミービット線に接続され、第1配線および第2配線は同レベルで接続されている。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

記憶装置及びその製造方法

【課題】高集積化が可能な記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る記憶装置は、下部電極層と、前記下部電極層上に設けられ、複数の微小導電体が隙間を介して集合したナノマテリアル集合層と、前記ナノマテリアル集合層上に設けられ、導電性であり、前記微小導電体に接し、開口部が形成された保護層と、前記保護層上に設けられ、前記保護層に接した上部電極層と、を備える。

(もっと読む)

不揮発性半導体記憶装置の動作方法

【課題】制御部を増加せずにブロックサイズを小さくできる不揮発性半導体記憶装置の動作方法を提供する。

【解決手段】メモリストリングを有するメモリ部と、メモリ部を制御する制御部と、を備える不揮発性半導体記憶装置110の動作方法である。メモリストリングは、直列に接続された複数のトランジスタを含み、複数のトランジスタのうちの一部である第1グループGR1と、第1グループの隣りに接続された第1調整用トランジスタTr−AJと、調整用トランジスタの第1グループとは反対側に接続されたトランジスタを含む第2グループGR2と、を有する。制御部は、第1グループのトランジスタの閾値の書き換えを行ったのち、第1調整用トランジスタに、閾値の書き換えによって生じた第2グループのトランジスタの閾値の相対的な変動分を調整する第1調整用閾値を設定する制御を行う。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

不揮発性メモリ装置

【課題】一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供することによって、読出しマージン減少による信頼性の下落を防止できる不揮発性メモリ装置が提供される。

【解決手段】本発明の実施形態による不揮発性メモリ装置は、基板と直交する方向に積層された複数のメモリセルを含むメモリセルアレイと、ワードラインを通じて前記メモリセルアレイに連結された行選択回路と、前記ワードラインに提供される電圧を発生する電圧発生回路と、を含み、前記電圧発生回路は、目標電圧レベルまで段階的に増加させる方式に前記電圧を発生する。本発明の実施形態による不揮発性メモリ装置は、一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供できる。したがって、読出しマージン減少による信頼性の下落が防止され得る。

(もっと読む)

熱処理装置

【課題】半導体薄膜を低熱負荷で均一に改質することのできる熱処理装置を提供する。

【解決手段】熱処理装置100の光学系は、一対の透明基板10A、10Bと、透明基板10A、10Bのそれぞれに設けられた透明電極11A、11Bと、透明電極11A、11Bに挟まれた液晶材12と、透明基板10A、10B、透明電極11A、11Bおよび液晶材12を挟む一対の偏光板13A、13Bとを備えたライトバルブアレイ4を有している。透明電極11Bは、ライトバルブアレイ領域14内でマトリクス状に細分化され、それぞれの透明電極11Bには、駆動回路15の選択スイッチを介して独立に電圧が印加される。

(もっと読む)

記憶装置

【課題】誤書込みを防止することが可能な記憶装置を提供する。

【解決手段】複数のメモリセルが直列に接続されたNANDセルユニットと、NANDセルユニットの一方の端子に接続する第1の選択トランジスタと、NANDセルユニットの他方の端子に接続する第2の選択トランジスタと、第1の選択トランジスタと接続するソース線と、該ソース線と交差し、且つ第2の選択トランジスタと接続するビット線とを有し、第1の選択トランジスタ及び第2の選択トランジスタは、チャネル領域が酸化物半導体層で形成されたトランジスタである。

(もっと読む)

不揮発性半導体記憶装置

【課題】データ保持特性を向上させた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1配線と第2配線との間に配置され、抵抗を変化させる可変抵抗素子を有するメモリセルを備える。メモリセルは、可変抵抗層、第1電極層、第2電極層、及び第1バリアハイト制御層を備える。可変抵抗層は、可変抵抗素子として機能する。可変抵抗層は、炭素(C)、珪素(Si)、及び水素(H)を含み、又は炭素(C)、珪素(Si)、及び水素(H)を含み且つ窒素(N)及び酸素(O)の少なくともいずれか一方を含む。第1電極層は、可変抵抗素子の一方の面側に設けられている。第2電極層は、可変抵抗素子の他方の面側に設けられている。第1バリアハイト制御層は、絶縁物からなり且つ可変抵抗層の一方の面と第1電極層との間に構成されている。

(もっと読む)

半導体メモリ装置及びそのリペア方法

【課題】 本発明は単一の半導体装置を構成する複数個のチップでヒューズ情報を伝送できる半導体装置に関することである。

【解決手段】半導体装置は信号伝送部及び信号受信部を含む。信号伝送部は第1チップに配置されて、伝送制御信号に同期してヒューズ情報を伝送する。信号受信部は第1チップ及び第2チップに各々配置されて、受信制御信号に同期して前記ヒューズ情報を受信する。

(もっと読む)

電界効果トランジスタを備える半導体素子及びその製造方法

【課題】電界効果トランジスタを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成され、第1活性領域の上面及び向き合う側面を経て伸張する第1ゲート電極を有する第1導電型の第1FET素子と、前記第1FET素子上に形成された層間絶縁膜と、前記層間絶縁膜上に形成され、第2活性領域の上面及び向き合う側面を経て伸張する第2ゲート電極を有する第2導電型の第2FET素子と、を備える。

(もっと読む)

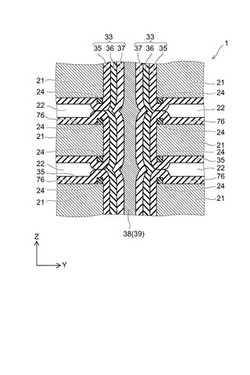

半導体記憶装置

【課題】さらなるDRAMの大記憶容量化を図る。

【解決手段】半導体記憶装置が、単結晶半導体材料を含む基板の一部を有する駆動回路と、当該駆動回路上に設けられる多層配線層と、当該多層配線層上に設けられるメモリセルアレイ層とを有する。すなわち、当該半導体記憶装置においては、駆動回路と、メモリセルアレイとが重畳して設けられる。したがって、単結晶半導体材料を含む基板に駆動回路及びメモリセルアレイを同一平面に設ける場合と比較して、当該半導体記憶装置の集積度を高めることが可能となる。

(もっと読む)

気化装置及び成膜装置

【課題】液体ソースを気化して成膜処理に用いられる処理ガスを得るにあたり、気化量を安定させ、かつ処理ガス濃度を高めること。

【解決手段】液体ソースを貯留するための気化室3の天井部に面接触した状態で、毛細管現象により液体ソースが広がる繊維体からなる面状体41を設ける。また、一端側が前記面状体41に接続され、他端側が前記気化室3内の液体ソースに接触するように、前記液体ソースを毛細管現象により吸い上げて面状体41に供給する吸い上げ部42を設ける。気化室3を加熱することにより、面状体41が加熱され、液体ソースが液面から気化すると共に、面状体41の表面からも気化するので、処理ガス濃度を高めることができる。また、吸い上げ部42のみが液体ソースに接触しているので、液面の高さ位置が変動しても、面状体への液体ソースの拡散状態に影響がなく、安定した気化量を確保することができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み時間の短縮及び読み出し電圧の上昇の抑制を図る不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリ部と、制御部と、を備える。メモリ部は、積層構造体と、半導体ピラーと、記憶層と、内側絶縁膜と、外側絶縁膜と、メモリセルトランジスタと、を有する。制御部は、メモリセルトランジスタの各閾値を正または負の一方に設定する制御、及び各閾値のうち0ボルトから最も離れた第n閾値の分布の幅よりも、第n閾値と同じ符号の第m(mはnよりも小さい1以上の整数)閾値の分布の幅を狭く設定する制御を行う。

(もっと読む)

半導体装置

【課題】制御チップと複数の被制御チップが積層されたタイプの半導体装置において、コマンド信号よりも層アドレス信号を早く伝送させる。

【解決手段】互いに異なる層情報を保持する複数の被制御チップCC0〜CC7と、被制御チップCC0〜CC7に対して層アドレス信号A13〜A15及びコマンド信号ICMDを共通に供給する制御チップIFとを備える。層アドレス信号A13〜A15を構成する各ビットは、複数の第1の貫通電極のうち、被制御チップごとに並列接続された少なくとも2本の貫通電極を経由して伝送され、コマンド信号ICMDを構成する各ビットは、出力切り替え回路及び入力切り替え回路によって選択された対応する1本の貫通電極を経由して伝送される。これにより、コマンド信号ICMDよりも先に層アドレス信号A13〜A15が各被制御チップに到達する。

(もっと読む)

半導体装置およびその製造方法

【課題】デバイス特性に優れた半導体装置およびその製造方法を提供する。

【解決手段】実施の一形態の半導体装置は、第1および第2の領域を有する機能膜と、前記基板の前記第1の領域に設けられ、第1の幅を有する第1の溝と、前記基板の前記第2の領域に設けられ、第1の幅よりも広い第2の幅を有する第2の溝と、前記第1の溝を埋めるように高分子材料を前駆体として形成された第1の絶縁膜と、前記第1の幅を上回る直径を有し、前記第2の溝を埋める微粒子と、前記第2の溝内で前記微粒子間および前記微粒子と前記第2の溝との間隙を埋める前記高分子材料とを前駆体として形成された第2の絶縁膜とを持つ。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

221 - 240 / 1,175

[ Back to top ]