Fターム[5F083GA10]の内容

Fターム[5F083GA10]に分類される特許

241 - 260 / 1,175

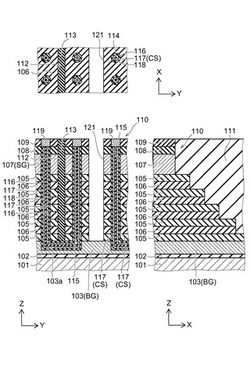

半導体記憶装置の製造方法

【課題】製造が容易なNAND型半導体記憶装置の製造方法を提供する。

【解決手段】製造方法は、基板101上に第1絶縁膜105及び第2絶縁膜106を交互に積層して積層体110を形成する工程と、第1絶縁膜105及び第2絶縁膜106の積層方向に延び、積層体110を貫通する貫通孔114を形成する工程と、貫通孔114の内面上に、MONOS116を構成するブロック絶縁膜、チャージトラップ膜及びトンネル誘電体膜の少なくとも一部を形成する工程と、トンネル誘電体膜上にチャネル半導体117を形成する工程と、積層体110にトレンチ121を形成する工程と、トレンチ121を介してエッチングを施すことにより、第2絶縁膜106を除去する工程と、第2絶縁膜106を除去した後の空間内に導電材料を埋め込む工程と、を備える。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供すること。

【解決手段】トランジスタと、容量素子と、を有し、トランジスタは、第1の酸化物半導体層と、第1の酸化物半導体層と接するソース電極およびドレイン電極と、第1の酸化物半導体層と重なるゲート電極と、第1の酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、容量素子は、ソース電極またはドレイン電極と、ソース電極またはドレイン電極と接する第2の酸化物半導体層と、第2の酸化物半導体層と接する容量素子電極と、を有する半導体装置である。

(もっと読む)

半導体記憶装置

【課題】高速動作が可能な半導体記憶装置を提供する。

【解決手段】実施形態によれば、基板、配線層、メモリ層、回路層及び第1、第2コンタクト配線を含む半導体記憶装置が提供される。配線層は、基板に平行な第1方向に沿う第1配線と、第2配線と、を含む。メモリ層は基板と配線層との間に設けられる。メモリ層は、第1配線と接続されたメモリセルを含む第1メモリセルアレイ部と、第1メモリセルアレイ部と第1方向に沿って並置され第1配線と接続されたメモリセルを含む第2メモリセルアレイ部と、を含む。回路層はメモリ層と基板との間に設けられ、回路部を含む。第1コンタクト配線は、第1メモリセルアレイ部と第2メモリセルアレイ部との間で、回路部の一端と第1配線とを接続する。第2コンタクト配線は、第1メモリセルアレイ部の第1コンタクト配線とは反対の側で、回路部の他端と第2配線とを接続する。

(もっと読む)

半導体記憶装置

【課題】動作速度の向上と面積の縮小を図る。

【解決手段】半導体記憶装置は、半導体基板100と、前記半導体基板上に形成され、データを記憶する複数のメモリセルが配置されたメモリセルアレイ部Aと、前記メモリセルアレイ部上に絶縁層を介して形成され、かつ、前記絶縁層および前記メモリセルアレイ部を貫通する孔106内に形成されて前記半導体基板に接続された単結晶半導体層109と、前記単結晶半導体層上に形成された回路部Bと、を具備し、前記メモリセルアレイ部上における前記単結晶半導体層の下部側は、上部側よりもGe濃度が高い。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においていずれかのバンクがアクティブ状態であるか否かを判定する。

【解決手段】バンクアドレス信号BA及びアクティブ信号ACT0を出力するインターフェースチップIFと、インターフェースチップIFに積層され、それぞれ対応するバンクアドレス信号BA及びアクティブ信号ACT0を受けて独立にアクティブ状態となる複数のメモリバンクを備えるコアチップCC0〜CC7とを備える。コアチップCC0〜CC7は、其々に含まれる複数のメモリバンクの少なくとも1つがアクティブ状態であるか否かを示すローカルバンクアクティブ信号MCIDTをインターフェースチップIFに其々出力し、インターフェースチップIFは、ローカルバンクアクティブ信号MCIDTの少なくとも1つが活性状態を示すときにバンクアクティブ信号PMCITを活性化させる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】複数のメモリセルを3次元状に配置し、かつ、メモリセルにMONOS型トランジスタを使用するNAND型不揮発性メモリにおいて、データ保持特性の劣化を抑制することができる技術を提供する。

【解決手段】ギャップ絶縁層GIL1の右端部側に凹部CUが形成されている。このとき、この凹部CUの形状を反映するように、凹部CUの内部に上部電位障壁層EB2と電荷蓄積層ECが形成されており、この凹部CUの形状を反映した電荷蓄積層ECの内側に形成される下部電位障壁層EB1によって、凹部CUが完全に埋め込まれている。このため、凹部CUを埋め込んだ下部電位障壁層EB1の表面は平坦になっており、この平坦になっている下部電位障壁層EB1の内側に柱状半導体部PSが形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】面積の縮小を図る。

【解決手段】不揮発性半導体記憶装置は、複数のメモリストリング200を具備し、各メモリストリングは、一対の柱状部A、および一対の柱状部の下端を連結させるように形成された連結部Bを有する半導体層SPと、柱状部に直交したコントロールゲートCGと、一対の柱状部の一方と直交し、コントロールゲートの上方に形成された第1選択ゲートSGSと、一対の柱状部の他方と直交し、コントロールゲートの上方に形成され、第1選択ゲートと同一レベルでかつ一体である第2選択ゲートSGDと、柱状部とコントロールゲートとの各交差部に形成されたメモリセルトランジスタMTrと、柱状部と第1選択ゲートとの交差部に形成された第1選択トランジスタSSTrと、柱状部と第2選択ゲートとの交差部に形成された第2選択トランジスタSDTrと、を含む。

(もっと読む)

半導体メモリ装置及びその動作方法

【課題】不揮発性メモリ装置及びその製造方法を提供すること。

【解決手段】本発明の不揮発性メモリ装置の製造方法は、セル領域及び周辺回路領域を有する基板上に層間絶縁膜及びゲート電極膜が交互に積層されたゲート構造物を形成するステップと、前記セル領域の前記ゲート構造物を選択的にエッチングして、複数層の前記ゲート電極膜を一方向から分離させる第1トレンチを形成するステップと、前記周辺回路領域のコンタクト予定領域に対応する前記ゲート構造物を選択的にエッチングして、第2トレンチを形成するステップと、を含む。

(もっと読む)

不揮発性メモリ装置及びその製造方法

【課題】不揮発性メモリ装置及びその製造方法を提供すること。

【解決手段】直列に接続した複数のメモリセルを含むメモリストリングと、前記メモリストリングの両端部にそれぞれ接続する第1及び第2選択トランジスタとを、含む不揮発性メモリ装置であって、前記メモリストリングが、第1半導体層145、及びメモリゲート絶縁膜を隔てて前記第1半導体層145と接する第2導電層125を含み、前記第1及び第2選択トランジスタが、それぞれ、前記第1半導体層145の一端及び他端と接続する第2及び第3半導体層165A、165Bを含み、前記第2導電層125が配置されない領域の前記第1半導体層145と接する第4半導体層165Cと、を含む。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは容量素子の容量を減らすと、データの読み出しエラーが発生しやすくなった。

【解決手段】1つの主ビット線MBL_mに複数個のセルを接続させる。各セルはサブビット線SBL_n_mと2乃至32個のメモリセル(MC_n_m_1、等)を有する。さらに各セルは選択トランジスタSTr_n_mと読み出しトランジスタRTr_n_mを有し、読み出しトランジスタRTr_n_mのゲートにはサブビット線SBL_n_mを接続する。サブビット線SBL_n_mの寄生容量は十分に小さいため、各メモリセルの容量素子の電荷情報を読み出しトランジスタRTr_n_mでエラーなく増幅でき、主ビット線MBL_mに出力できる。

(もっと読む)

トランジスタおよびメモリアレイ

【課題】大きな順方向−逆方向電流比を有するスイッチングデバイスを提供する。

【解決手段】トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

読み出しマージンが改良されたマルチビット磁気ランダムアクセスメモリセル

【課題】読み出しマージンが改良されたマルチビット磁気ランダムアクセスメモリセルを提供する。

【解決手段】第1の磁化方向を有する第1の磁性層21と第2の磁化方向を有する第2の磁性層23との間にトンネル障壁層22を備える磁気ランダムアクセスメモリ(MRAM)セルであって、第2の磁化方向が、第1の磁化方向に対して第1の方向から第2の方向に調節可能であり、前記磁気トンネル接合がさらに電気的に接続されるスイッチング抵抗素子62を備え、スイッチング抵抗素子を通してスイッチング電流が流されるときに第1のスイッチング抵抗レベルから第2のスイッチング抵抗レベルに切り換えることができるスイッチング抵抗を有し、それにより、MRAMセルのMRAMセル抵抗が、接合抵抗及びスイッチング抵抗の抵抗レベルに応じて少なくとも4つの異なるセル抵抗レベルを有することができる磁気ランダムアクセスメモリ(MRAM)セル。

(もっと読む)

半導体記憶装置

【課題】メモリセルの特性の劣化を抑制した半導体記憶装置を提供する。

【解決手段】メモリセルは、ダイオード層、可変抵抗層、及び電極層を備える。ダイオード層は、整流素子として機能する。可変抵抗層は、可変抵抗素子として機能する。電極層は、可変抵抗層とダイオード層との間に設けられ、可変抵抗層及びダイオード層に接するように形成されている。電極層は、窒化チタンにて構成された窒化チタン層を備える。ここで、窒化チタン層内の第1領域における窒素原子に対するチタン原子の割合を第1割合とし、窒化チタン層内であって且つ第1領域よりも可変抵抗層に近い第2領域における窒素原子に対するチタン原子の割合を第2割合とする。この場合、第2割合は第1割合よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】データの取り扱いが容易な半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、基板と、前記基板上に設けられ、それぞれ複数の絶縁膜及び電極膜が交互に積層され、前記基板の上面に対して平行な第1の方向側の端部において、それぞれが各前記電極膜の上面によって構成された複数のテラスが前記第1の方向のみに沿って階段状に形成された積層体と、前記テラスに接続され、前記電極膜を、前記基板の上面に平行な方向であって前記第1の方向に対して直交する第2の方向に引き出し、前記基板に接続する導電部材と、前記積層体の中央部に設けられ、前記絶縁膜及び前記電極膜の積層方向に延びる半導体ピラーと、前記電極膜と前記半導体ピラーとの間に設けられた電荷蓄積層と、を備える。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法

【課題】消費電力の少ない新規の半導体メモリ装置を提供する

【解決手段】書き込みトランジスタWTr_n_mのソースと読み出しトランジスタRTr_n_mのゲートとキャパシタCS_n_mの一方の電極を接続し、書き込みトランジスタWTr_n_mのゲートとドレインを、それぞれ書き込みワード線WWL_nと書き込みビット線WBL_mに、キャパシタCS_n_mの他方の電極を読み出しワード線RWL_nに、読み出しトランジスタRTr_n_mのドレインを読み出しビット線RBL_mに接続した構造とする。ここで、読み出しビット線RBL_mの電位はフリップフロップ回路FF_mのような反転増幅回路に入力され、反転増幅回路によって反転された電位が書き込みビット線WBL_mに出力される構造とする。

(もっと読む)

半導体装置

【課題】複数のメモリチップが積層された半導体装置においてリードライトバスの本数及び配線長を削減する。

【解決手段】積層された複数のメモリチップCC0〜CC7を備え、各メモリチップは複数のメモリバンクBank0〜Bank7と、各メモリバンクにそれぞれ割り当てられた複数のリードライトバスRWBS0〜RWBS7と、リードライトバスにそれぞれ割り当てられ当該メモリチップを貫通して設けられた複数の貫通電極TSV1とを備える。積層方向から見て互いに同じ位置に設けられた貫通電極TSV1はチップ間において共通接続される。メモリチップのそれぞれは、アクセスが要求されたことに応答して積層方向から見て互いに異なる位置に設けられたメモリバンクを同時に活性化し、これにより、平面位置の異なる貫通電極TSV1を介してデータの入出力を同時に行う。

(もっと読む)

半導体装置およびその製造方法

【課題】高品質な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、第1の配線L2(i)と、第1の配線と交差する第2の配線L3(j)と、第1の配線と第2の配線とが交差する各領域に設けられ、一端が第1の配線に接続され、且つ他端が第2の配線に接続され、可変抵抗素子25及び非オーミック素子D−mimが直列接続されたメモリセル構造CUsと、を備え、非オーミック素子は、絶縁層22として、第1の層22aと、第1の層のバンドギャップとは異なるバンドギャップを有し、第1の層上に設けられた第2の層22bと、第2の層のバンドギャップとは異なるバンドギャップを有し、第2の層上に設けられた第3の層22cとを備えている。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】工程数の増大を抑制しつつ、3次元集積化を図るとともに、制御ゲート電極と浮遊ゲート電極との間のカップリング比を向上させる。

【解決手段】柱状半導体10と、柱状半導体10の側面にトンネル絶縁膜9を介して形成された浮遊ゲート電極8と、浮遊ゲート電極8を取り囲むようにブロック絶縁膜7を介して形成された制御ゲート電極2、3´、4を設ける。

(もっと読む)

241 - 260 / 1,175

[ Back to top ]