Fターム[5F083GA29]の内容

Fターム[5F083GA29]に分類される特許

1 - 20 / 165

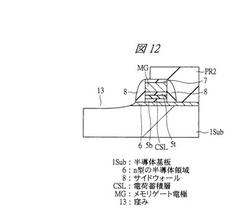

半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

メモリ装置

【課題】増加されたメモリ容量を具現できるメモリ装置を提供する。

【解決手段】メモリ装置は、水平な共通導電領域の上に配置され、前記共通導電領域に一端が電気的に連結され、互いに離隔水平な第1選択ラインの上で互いに平行に延長され前記水平な第1選択ラインと交差し前記垂直な半導体柱の側面に対向する側面を包含する水平な第1選択ラインと、前記水平な第1選択ラインと前記垂直な半導体柱との間に、そして前記水平な第2選択ラインと前記垂直な半導体柱との間に介在される少なくとも1つの誘電パターンを包含する選択構造体を含む。前記メモリ装置は、前記選択構造体の上に配置され前記垂直な半導体柱に電気的に連結されたメモリセルを含むメモリセルアレイをさらに含む。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】熱工程による負担を減らし、メモリセル特性の向上を図る。

【解決手段】本実施形態による不揮発性半導体記憶装置の製造方法よれば、基板上30に、コントロールゲートCGとなる導電膜を形成する。前記導電膜の上面から下面まで貫通するホール40を形成する。前記ホールの内面上に、ブロック絶縁膜150を形成する。前記ブロック絶縁膜上に、電荷蓄積膜151を形成する。前記電荷蓄積膜上に、トンネル絶縁膜152を形成する。前記トンネル絶縁膜上に、半導体層SPを形成する。前記半導体層上に、前記ホールが埋め込まれないように酸素乖離の触媒作用を有する材料を含む膜153を形成する。前記ホールの内側から前記膜を介して、前記トンネル絶縁膜と前記半導体層との界面を酸化する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を劣化させることなく、半導体材料または絶縁膜の結晶特性を改善することができる低温アニールを用いた半導体装置の製造方法、並びに、このような低温アニールに適した半導体装置を提供する。

【解決手段】本実施形態による半導体装置は、半導体基板の上方に設けられた金属からなる下部電極と、下部電極の上方に設けられた金属からなる上部電極と、下部電極と上部電極との間に設けられた結晶層とを備える。下部電極および上部電極の各膜厚は、結晶層の結晶化に用いられるマイクロ波の周波数に対応する表皮効果における表皮層よりも薄い。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

記憶回路

【課題】短時間の電源停止により消費電力を抑えることができ、電源再開時において誤動作を引き起こすことなく初期化することのできる信号処理装置の記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性記憶部に記憶していたデータ信号を、不揮発性記憶部に保持する。不揮発性記憶部では、オフ電流が極めて小さいトランジスタを用いることによって、容量素子に保持されたデータ信号は長期間にわたり保持する。こうして、不揮発性記憶部は電源の供給が停止した間も論理状態を保持する。また電源停止時に容量素子で保持されたデータ信号は、電源再開時にはリセット回路を導通状態とすることで、誤動作を引き起こすことのない電位にする。

(もっと読む)

記憶装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な記憶装置、及び該記憶装置を有する半導体装置を提供する。

【解決手段】第1の入力端子、及び第1の入力端子の入力信号の反転信号が入力される第2の入力端子、並びに第1の信号が出力される第1の出力端子、及び第1の信号の反転信号が出力される第2の出力端子、を有するレベルシフタと、第1の信号が入力される第3の入力端子、及び第1の信号の反転信号が入力される第4の入力端子、並びに第3の出力端子を有する第1のバッファと、第1の信号の反転信号が入力される第5の入力端子、及び第1の信号が入力される第6の入力端子、並びに第4の出力端子を有する第2のバッファと、を有し、第1のバッファの第3の出力端子から出力される信号が、レベルシフタの第1の入力端子に入力され、第2のバッファの第4の出力端子から出力される信号が、レベルシフタの第2の入力端子に入力される。

(もっと読む)

ルチル結晶構造を備えた酸化チタン膜の製造方法

【課題】高温のアニールを必要とせずに、誘電率の高いルチル結晶構造の酸化チタン膜を形成する。

【解決手段】非晶質の酸化ジルコニウム膜上に、チタンプリカーサとしてメチルシクロペンタジエニルトリスジメチルアミノチタンを用いてALD法により非晶質の酸化チタン膜を形成し、300℃以上の温度でアニールして結晶化することでルチル結晶構造を有する酸化チタン膜が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】アモルファス半導体膜の結晶化を低温で短時間に行うことができ、大粒径の結晶粒を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】実施形態による半導体装置の製造方法では、基板上にアモルファス半導体膜を形成する。さらに、前記方法では、前記基板上にマイクロ波を照射することにより、前記アモルファス半導体膜をアニールして、前記アモルファス半導体膜から多結晶半導体膜を形成する。さらに、前記方法では、前記多結晶半導体膜をチャネルとするトランジスタを形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させる。

【解決手段】シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させ、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成し、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を用いた半導体装置であるトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させる。具体的には、酸化物半導体膜を用いたトランジスタのゲート絶縁膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、接合リーク電流を低減可能で、かつトランジスタの信頼性を向上させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート電極61よりも上方に配置されたゲート絶縁膜21、及びゲート電極61の上面61aを覆う水素含有絶縁膜62と、水素含有絶縁膜62を介して、ゲート電極用溝17の上部17Bを埋め込むフッ素含有絶縁膜63と、を備え、ゲート絶縁膜21と接触する第1及び第2の不純物拡散領域65,66の面に、半導体基板13に含まれるシリコンと水素含有絶縁膜62に含まれる水素とが結合したSi−H結合、及び半導体基板13に含まれるシリコンとフッ素含有絶縁膜63に含まれるフッ素とが結合したSi−F結合を有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 チャネルにおける電子の移動度低下を抑制する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】

実施形態に係る不揮発性半導体記憶装置は、基板を持つ。基板上方には、絶縁膜及び電極膜が交互に積層された積層体が設けられている。前記積層体を貫き、前記積層体中に弗素を含むシリコンピラーが設けられている。前記シリコンピラーの前記積層体に対向する面上にトンネル絶縁膜が設けられている。前記トンネル絶縁膜の前記積層体に対向する面上には電荷蓄積層が設けられている。前記電荷蓄積層の前記積層体に対向する面上に前記電極膜と接するようにブロック絶縁膜が設けられている。前記シリコンピラー中に埋込部が設けられている。

(もっと読む)

記憶装置

【課題】アモルファスシリコンを記憶部に用いる記憶装置の動作電圧を低減し、かつ、それを低温プロセスで形成する。

【解決手段】実施形態に係わる記憶装置は、結晶化されたSixGe1−x (0≦x<1)層を含む第1の電極EL1と、金属元素を含む第2の電極EL2と、第1及び第2の電極EL1,EL2間に配置され、アモルファスSi層を含む可変抵抗部VRと、アモルファスSi層内の金属元素を含むフィラメントの長さを制御する制御回路とを備える。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の構成材料の特性劣化を抑制しつつ、基板とゲート絶縁膜との界面の界面準位密度を効率的に低減することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、基板100上に、ゲート絶縁膜102とゲート電極103とを含むトランジスタを形成する。さらに、基板100上に1層の配線層110を形成する処理と、1層の配線層110を配線パターンに加工する処理を1回以上行うことにより、基板100上に、1層以上の配線層113,115を含む配線構造を形成する。さらに、基板100上に、1層以上の配線層113,115のうちの少なくとも1層の配線層110が配線パターンに加工された後に、基板100上にマイクロ波を照射して基板100のアニールを行う。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化した半導体集積回路において用いられるキャパシタを提供する。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

(もっと読む)

抵抗変化素子の駆動方法、不揮発性記憶装置、抵抗変化素子および多値記憶方法

【課題】多値の記憶状態を安定して読み書きできる抵抗変化素子の駆動法を提供する。

【解決手段】第1電極2を基準とする第2電極4の電位である電極間電圧を抵抗変化素子10に印加することによって第1電極2と第2電極4との間の抵抗値である電極間抵抗値を可逆的に変化させる抵抗変化素子10の駆動方法であって、Vα<Vβ<0およびVγ>0およびRL<RM<RHを満たすVα、Vβ、Vγ、RL、RM、RHについて、電極間電圧Vαの印加によって電極間抵抗値をRLにする書き込み過程と、書き込み過程の後、電極間電圧Vγの印加によって電極間抵抗値をRMにする第1の消去過程と、第1の消去過程の後、電極間電圧Vβの印加によって電極間抵抗値をRHにする第2の消去過程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】基板に電圧を印加して基板にダメージを及ぼすことなく、当該基板における、大型基板において特に顕在化する複雑な態様の反りの発生部位及び発生状態を容易且つ正確に特定する。そして、大型基板でも確実なチャッキングに供することを可能とする。

【解決手段】センサ部2は、搭載面1aの中央部分に設けられた第1のセンサ群11と、第1のセンサ群11を囲む第2のセンサ群12と、第2のセンサ群12を囲む第3のセンサ群13とを有する。第1のセンサ群11は、基板面の中央部分に対応して設けられた1つの静電容量センサ10aから、第2のセンサ群12は、第1のセンサ群11を同心状に囲む複数の静電容量センサ10aから、第3のセンサ群13は、第2のセンサ群12を同心状に囲み、搭載面1aの周縁の近くに設けられた複数の静電容量センサ10aを有する。

(もっと読む)

1 - 20 / 165

[ Back to top ]