Fターム[5F083KA01]の内容

Fターム[5F083KA01]の下位に属するFターム

Fターム[5F083KA01]に分類される特許

161 - 180 / 1,285

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】論理回路の動作特性に優れた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、多層配線層と、第1能動素子3a、容量素子19および周辺回路を有する記憶回路200と、第2能動素子3bを有する論理回路100と、記憶回路領域200に形成されており、能動素子3aと容量素子19とを電気的に接続する容量コンタクト13cと、論理回路領域100に形成されており、能動素子3bと第1配線8aとを電気的に接続する接続コンタクト13aと、を備え、第1配線8aは、容量素子19が埋め込まれた配線層のうち最下層の配線層の層間絶縁膜7aに位置しており、接続コンタクト13aは、容量コンタクト13cと同一層に設けられており、第1配線8aと接続コンタクト13aは、デュアルダマシン構造を有している。

(もっと読む)

記憶装置

【課題】誤書込みを防止することが可能な記憶装置を提供する。

【解決手段】複数のメモリセルが直列に接続されたNANDセルユニットと、NANDセルユニットの一方の端子に接続する第1の選択トランジスタと、NANDセルユニットの他方の端子に接続する第2の選択トランジスタと、第1の選択トランジスタと接続するソース線と、該ソース線と交差し、且つ第2の選択トランジスタと接続するビット線とを有し、第1の選択トランジスタ及び第2の選択トランジスタは、チャネル領域が酸化物半導体層で形成されたトランジスタである。

(もっと読む)

記憶素子、記憶装置、信号処理回路、記憶素子の駆動方法

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶素子を提供する。消費電力の低減可能な信号処理回路を提供する。

【解決手段】クロック信号に同期してデータを保持する記憶素子において、酸化物半導体層にチャネルが形成されるトランジスタ及び容量素子を用いることより、電源電圧の供給が停止した間もデータ保持ができる。ここで、電源電圧の供給を停止する前に、クロック信号のレベルを一定に保った状態で当該トランジスタをオフ状態とすることにより、データを正確に容量素子に保持させることができる。また、このような記憶素子を、CPU、メモリ、及び周辺制御装置のそれぞれに用いることによって、CPUを用いたシステム全体で、電源電圧の供給停止を可能とし、当該システム全体の消費電力を削減することができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み時間の短縮及び読み出し電圧の上昇の抑制を図る不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリ部と、制御部と、を備える。メモリ部は、積層構造体と、半導体ピラーと、記憶層と、内側絶縁膜と、外側絶縁膜と、メモリセルトランジスタと、を有する。制御部は、メモリセルトランジスタの各閾値を正または負の一方に設定する制御、及び各閾値のうち0ボルトから最も離れた第n閾値の分布の幅よりも、第n閾値と同じ符号の第m(mはnよりも小さい1以上の整数)閾値の分布の幅を狭く設定する制御を行う。

(もっと読む)

半導体装置

【課題】非接触でデータの送受信が可能な半導体装置は、鉄道乗車カードや電子マネーカ

ードなどの一部では普及しているが、さらなる普及のためには、安価な半導体装置を提供

することが急務の課題であった。上記の実情を鑑み、単純な構造のメモリを含む半導体装

置を提供して、安価な半導体装置及びその作製方法の提供を課題とする。

【解決手段】有機化合物を含む層を有するメモリとし、メモリ素子部に設けるTFTのソ

ース電極またはドレイン電極をエッチングにより加工し、メモリのビット線を構成する導

電層とする。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】ノイズによるデータ信号への影響を抑制する半導体記憶装置を提供する。

【解決手段】記憶回路を具備し、記憶回路は、それぞれが電界効果トランジスタであり、1個目の電界効果トランジスタ111a−1のソース及びドレインの一方にデジタルデータ信号が入力され、k個目(kは2以上n(nは2以上の自然数)以下の自然数)の電界効果トランジスタのソース及びドレインの一方がk−1個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続されるn個の電界効果トランジスタと、それぞれ一対の電極を有し、m個目(mはn以下の自然数)の容量素子の一対の電極の一方が、n個の電界効果トランジスタのうち、m個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続され、少なくとも2つの容量素子における容量値が異なるn個の容量素子112aー1〜112aーnとを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】デバイス特性に優れた半導体装置およびその製造方法を提供する。

【解決手段】実施の一形態の半導体装置は、第1および第2の領域を有する機能膜と、前記基板の前記第1の領域に設けられ、第1の幅を有する第1の溝と、前記基板の前記第2の領域に設けられ、第1の幅よりも広い第2の幅を有する第2の溝と、前記第1の溝を埋めるように高分子材料を前駆体として形成された第1の絶縁膜と、前記第1の幅を上回る直径を有し、前記第2の溝を埋める微粒子と、前記第2の溝内で前記微粒子間および前記微粒子と前記第2の溝との間隙を埋める前記高分子材料とを前駆体として形成された第2の絶縁膜とを持つ。

(もっと読む)

半導体記憶装置

【課題】高速動作が可能な半導体記憶装置を提供する。

【解決手段】実施形態によれば、基板、配線層、メモリ層、回路層及び第1、第2コンタクト配線を含む半導体記憶装置が提供される。配線層は、基板に平行な第1方向に沿う第1配線と、第2配線と、を含む。メモリ層は基板と配線層との間に設けられる。メモリ層は、第1配線と接続されたメモリセルを含む第1メモリセルアレイ部と、第1メモリセルアレイ部と第1方向に沿って並置され第1配線と接続されたメモリセルを含む第2メモリセルアレイ部と、を含む。回路層はメモリ層と基板との間に設けられ、回路部を含む。第1コンタクト配線は、第1メモリセルアレイ部と第2メモリセルアレイ部との間で、回路部の一端と第1配線とを接続する。第2コンタクト配線は、第1メモリセルアレイ部の第1コンタクト配線とは反対の側で、回路部の他端と第2配線とを接続する。

(もっと読む)

半導体記憶装置の製造方法

【課題】製造が容易なNAND型半導体記憶装置の製造方法を提供する。

【解決手段】製造方法は、基板101上に第1絶縁膜105及び第2絶縁膜106を交互に積層して積層体110を形成する工程と、第1絶縁膜105及び第2絶縁膜106の積層方向に延び、積層体110を貫通する貫通孔114を形成する工程と、貫通孔114の内面上に、MONOS116を構成するブロック絶縁膜、チャージトラップ膜及びトンネル誘電体膜の少なくとも一部を形成する工程と、トンネル誘電体膜上にチャネル半導体117を形成する工程と、積層体110にトレンチ121を形成する工程と、トレンチ121を介してエッチングを施すことにより、第2絶縁膜106を除去する工程と、第2絶縁膜106を除去した後の空間内に導電材料を埋め込む工程と、を備える。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは容量素子の容量を減らすと、データの読み出しエラーが発生しやすくなった。

【解決手段】1つの主ビット線MBL_mに複数個のセルを接続させる。各セルはサブビット線SBL_n_mと2乃至32個のメモリセル(MC_n_m_1、等)を有する。さらに各セルは選択トランジスタSTr_n_mと読み出しトランジスタRTr_n_mを有し、読み出しトランジスタRTr_n_mのゲートにはサブビット線SBL_n_mを接続する。サブビット線SBL_n_mの寄生容量は十分に小さいため、各メモリセルの容量素子の電荷情報を読み出しトランジスタRTr_n_mでエラーなく増幅でき、主ビット線MBL_mに出力できる。

(もっと読む)

半導体装置

【課題】半導体装置を高集積化する。

【解決手段】本実施形態の半導体装置は、絶縁体内に設けられ、半導体集積回路を含んでいる半導体基板70と、絶縁体の開口部POPを介してその上面が露出するパッド90と、パッド90下方において半導体基板70のキャパシタ領域91内に設けられる複数のキャパシタ1と、を具備し、キャパシタ1は、所定の被覆率を満たすように、パッド90下方のキャパシタ領域91内に設けられ、キャパシタ1の2つの電極にそれぞれ接続されるコンタクト18A,18Gは、開口部POPと上下に重ならない位置に設けられている。

(もっと読む)

SOI型トランジスタ

【課題】DRAMメモリアレイに用いられるセミコンダクタ・オン・インシュレータ型トランジスタを提供する。

【解決手段】SOI型のトランジスタは、半導体物質層60(SOI層)と、この半導体物質層60の内部を通って走るゲート線65a,65b,66cと、このゲート線65a,65b,66cに沿ってソース拡散領域70a、70b、70cよりも遠くまで延びるドレイン拡散領域64と、このドレイン拡散領域64よりも上方にあるソース拡散領域70a、70b、70cと、ドレイン拡散領域64まで延びるドレインコンタクト79と、ソース拡散領域まで延びるソースコンタクトと、を備え、これらドレインコンタクト79及びソースコンタクトは、ゲート線65a,65b,66cと平行に走る平面内にある。

(もっと読む)

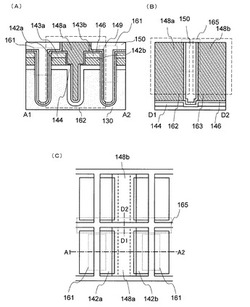

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】Y方向に延在するように半導体基板13に設けられ、底面18c及び対向する第1及び第2の側面18a,18bを有するゲート電極用溝18と、ゲート絶縁膜21を介して、ゲート電極用溝18の下部を埋め込むように配置されたゲート電極22と、ゲート電極用溝18を埋め込むように配置され、ゲート電極22の上面22aを覆う埋め込み絶縁膜24と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆うように、半導体基板13に設けられた第1の不純物拡散領域28と、少なくとも第2の側面18bに配置されたゲート絶縁膜21を覆うように、半導体基板13に設けられた第2の不純物拡散領域29と、を有する。

(もっと読む)

半導体記憶装置

【課題】CMOSプロセスで、ダイナミック型半導体記憶装置を形成し、ロジックとの混載に適したダイナミック型半導体記憶装置を実現する。

【解決手段】メモリセル(MC)のワード線(WL)を形成する導電線(3)とメモリセルセルプレート電極(CP)を形成する導電線(5)とを、異なる配線層に形成する。対をなすビット線に並行してメモリセルを接続し、2つのメモリセルで1ビットのデータを記憶する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みゲート型トランジスタの電流駆動能力の低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置100は、半導体基板1において素子分離領域5によって複数の活性領域50が区画されると共に、前記半導体基板1内に埋め込まれたワード線8を有する半導体装置100であって、前記ワード線8は、第一の溝部8a内にゲート絶縁膜7aを介して埋め込まれた導電層8bからなり、前記素子分離領域5は、前記第一の溝部8aよりも幅の狭い第二の溝部5aに前記ゲート絶縁膜7bを介して埋め込まれた前記導電層5bからなることを特徴とする。

(もっと読む)

記憶装置、集積回路装置、及び電子機器

【課題】マルチポートメモリーとして機能する場合に、クロストークノイズを大幅に低減して、誤動作を防止して回路動作の安定化を図る記憶装置等を提供する。

【解決手段】メモリーセルアレイ10を有する半導体記憶装置100は、第1の方向に並ぶメモリーセルを選択するための第1のワードラインと、第2の方向に並ぶメモリーセルを選択するための第2のワードラインと、第1のワードラインによって選択されたメモリーセルに接続される一対の第1のビットライン及び第1の相補ビットラインと、前記第2のワードラインによって選択されたメモリーセルに接続される第2のビットラインとを含み、第2のワードラインは、対応する一対の第1のビットライン及び第1の相補ビットラインに対し、上面から見て第1の方向又は該第1の方向の反対方向に隣接して、第2の方向に延びるように配置される。

(もっと読む)

半導体記憶装置

【課題】メモリセルの特性の劣化を抑制した半導体記憶装置を提供する。

【解決手段】メモリセルは、ダイオード層、可変抵抗層、及び電極層を備える。ダイオード層は、整流素子として機能する。可変抵抗層は、可変抵抗素子として機能する。電極層は、可変抵抗層とダイオード層との間に設けられ、可変抵抗層及びダイオード層に接するように形成されている。電極層は、窒化チタンにて構成された窒化チタン層を備える。ここで、窒化チタン層内の第1領域における窒素原子に対するチタン原子の割合を第1割合とし、窒化チタン層内であって且つ第1領域よりも可変抵抗層に近い第2領域における窒素原子に対するチタン原子の割合を第2割合とする。この場合、第2割合は第1割合よりも大きい。

(もっと読む)

半導体記憶装置の製造方法

【課題】立体構造を有する電極などの部材上に、組成の同じALD膜を形成することの可能な半導体記憶装置の製造方法を提供する。

【解決手段】半導体基板上に、下部電極、上部電極、および下部電極と上部電極に挟まれる容量絶縁膜からなるキャパシタを有する半導体記憶装置の製造方法において、前記下部電極の表面および前記層間絶縁膜の表面に、Alの前駆体とZrの前駆体の前記下部電極に対する各々の被覆特性が一致する条件で、前記Alの前駆体と前記Zrの前駆体を反応室内に供給する工程と、前記Alの前駆体と前記Zrの前駆体を反応室から真空排気する第1の真空排気工程と、酸化剤を反応室に供給する工程と、前記酸化剤を前記反応室から真空排気する第2の真空排気工程と、繰り返すALDフローシーケンスによりZrAlO膜を形成する工程を採用する。

(もっと読む)

161 - 180 / 1,285

[ Back to top ]