Fターム[5F083KA01]の内容

Fターム[5F083KA01]の下位に属するFターム

Fターム[5F083KA01]に分類される特許

81 - 100 / 1,285

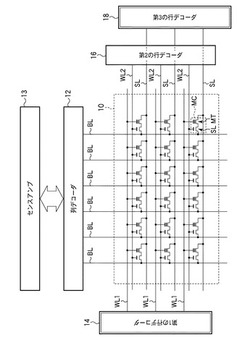

不揮発性半導体記憶装置

【課題】高速で動作し得る不揮発性半導体記憶装置を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタMTとを有するメモリセルMCがマトリクス状に配列されて成るメモリセルアレイ10と、ビット線BLの電位を制御する列デコーダ12と、第1のワード線WL1の電位を制御する電圧印加回路14と、第2のワード線WL2の電位を制御する第1の行デコーダ16と、ソース線SLの電位を制御する第2の行デコーダ18とを有し、列デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されており、第1の行デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されている。ビット線と第2のワード線とが高速で制御され得るため、メモリセルトランジスタに書き込まれた情報を高速で読み出すことができる。

(もっと読む)

セルダイオードを採用する相変移記憶素子及びその製造方法

【課題】セルダイオードを用いる相変移記憶素子及びその製造方法を提供すること。

【解決手段】相変移記憶素子は、第1導電型の半導体基板及び前記半導体基板上に配置された複数のワードラインを備える。前記ワードラインは、前記第1導電型と異なる第2導電型を有して実質的に平らな上部面を有する。前記ワードラインのそれぞれの上部面上に前記ワードラインの長さ方向に沿って一次元的に配列された第1半導体パターンを提供する。前記第1半導体パターンは、前記第1導電型または前記第2導電型を有する。前記第1半導体パターン上に前記第1導電型を有する第2半導体パターンが積層される。前記ワードライン間のギャップ領域、前記第1半導体パターン間のギャップ領域、及び前記第2半導体パターン間のギャップ領域は絶縁膜で埋められる。前記絶縁膜の上部に複数の相変移物質パターンが二次元的に配列される。前記相変移物質パターンは前記第2半導体パターンにそれぞれ電気的に接続される。

(もっと読む)

不揮発性半導体記憶装置

【課題】ビット線接続部の微細化を実現する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、p型の半導体基板101と、半導体基板101内に形成され、メモリセルのビット線とセンスアンプ部を接続するビット線接続トランジスタHTkが形成されるp型の第1のPウェル102と、第1のPウェル102を囲み、第1のPウェル102を半導体基板101から電気的に分離するn型の第1のNウェル103と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】埋込ワード線の高さにばらつきのない半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、複数の素子分離領域を形成すると共に、素子分離領域間に素子形成領域を形成する工程と、素子形成領域に交差する第1の方向に延在するゲート電極溝を形成する工程と、ゲート電極溝の内壁にゲート絶縁膜を形成する工程と、ゲート電極溝の内壁にゲート絶縁膜を介して第1導電膜を形成する工程と、ゲート電極溝内を埋め込むように第2導電膜を形成する工程と、第2導電膜上に平坦化膜を形成する工程と、第2導電膜が露出するように平坦化膜をエッチングして除去する第1のエッチング工程と、第2導電膜がゲート電極溝の下部に残留するように第2導電膜をエッチングする第2のエッチング工程と、第1導電膜が前記ゲート電極溝の下部に残留するように第1導電膜をエッチングする第3のエッチング工程と、を有することを特徴とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】データの劣化を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルは、半導体層、電荷蓄積層、及び導電層を備える。半導体層は、半導体基板に対して垂直方向に延び、メモリセルのボディとして機能する。電荷蓄積層は、半導体層の側面に設けられ、電荷を蓄積する。導電層は、半導体層と電荷蓄積層を挟むよう設けられ、メモリセルのゲートとして機能する。制御回路は、第1プログラム動作の後、第2プログラム動作を実行する。第1プログラム動作は、メモリセルのボディに第1電圧を印加し且つメモリセルのゲートに第1電圧よりも大きい第2電圧を印加することによりメモリセルの閾値電圧を正方向に移動させる動作である。第2プログラム動作は、メモリセルのボディをフローティングにし且つメモリセルのゲートに正の第3電圧を印加する動作である。

(もっと読む)

半導体装置およびその製造方法

【課題】第1の領域のゲート絶縁膜への酸化剤の進入を防止しつつ、第2の領域の複数の第1の配線間に設けられた酸化アルミニウム膜を選択的に除去する。

【解決手段】第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線を覆うように形成した第1の絶縁膜をマスクとして、第1の領域に第1のイオン注入を施す。その後、第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線間を埋設するように形成した、酸化アルミニウムを主体とする第2の絶縁膜をマスクとして、第1の領域に第2のイオン注入を施す。第2の絶縁膜を、第1の絶縁膜に対して選択的に除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】 対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和する。

【解決手段】 半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する半導体装置。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】制御ゲートの低抵抗化を図ることができる半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、シリコンを含む基板と、前記基板上に形成され、浮遊ゲートと、前記浮遊ゲート上に形成されたゲート間絶縁膜と、前記ゲート間絶縁膜上に形成された制御ゲートと、を有した複数のメモリセルと、を備えている。そして、前記制御ゲートは、前記制御ゲートの上層に形成されニッケルシリサイドを含む上層部と、前記上層部の下方に形成されポリシリコンを含む下層部と、前記上層部と前記下層部との間に形成されヒ素およびアンチモンの少なくともいずれかを偏析させた偏析部と、を有している。

(もっと読む)

マンガン酸化物、マンガン酸化物を備える強誘電体メモリ素子、および強誘電体メモリ装置

【課題】主成分として有害物質鉛元素を含まずに、強誘電性を示しかつ外部磁場によって分極の大きさを制御可能な新規なマンガン酸化物、およびそのメモリへの利用を提供する。

【解決手段】マンガン酸化物は、ペロブスカイト構造を有する、式(1)Sr1−xBaxMnO3(1≧x>0.4)・・・(1)で表されるマンガン酸化物である。単位格子1の対称中心には磁性イオンであるMnイオン3が存在する。単位格子1の対称中心をMnサイトとする。単位格子1が有する8個の頂点には、SrイオンおよびBaイオンのうちいずれか一方が存在している。単位格子1が有する頂点をSrサイト2とする。単位格子1が有する6面の面心には、Oイオン4が存在する。

(もっと読む)

不揮発性抵抗変化素子

【課題】デバイス特性の劣化やバラツキを低減でき、整流機能を有する不揮発性抵抗変化素子を提供する。

【解決手段】金属元素を含む上部電極1と、n型半導体を含む下部電極2と、上部電極1と下部電極2との間に配置され、上部電極1が含む金属元素から構成される導体部を有する抵抗変化層3とを備える。抵抗変化層3が有する導体部は下部電極2との間に離間を有している。

(もっと読む)

半導体装置の製造方法

【課題】エピタキシャル成長後に不純物を導入するためのイオン注入工程を省略する。また、エピタキシャル成長層の厚さがばらついた場合であっても、ピラー部にまで不純物が導入されることによるトランジスタ特性の変動を防止する。

【解決手段】基板の主面にシリコンピラーを形成した後、シリコンピラーの下の基板内に、シリコンピラーと逆導電型の第1の拡散層を形成する。シリコンピラーの側面にゲート絶縁膜を介してゲート電極を形成する。次に、シリコンピラーの上面上に不純物を含むシリコンをエピタキシャル成長させることで、シリコンピラーと逆導電型の第2の拡散層を形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高性能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1及び第2のメモリセルMCを有し、第2の方向に延びるフィン型積層構造Fin0〜Fin3と、フィン型積層構造Fin0〜Fin3の第2の方向の一端に接続され、第3の方向に延びる梁5とを備える。フィン型積層構造Fin0〜Fin3及び梁5は、それぞれ、第1の方向に積み重ねられる第1及び第2の半導体層2a,2bを備え、梁5は、第3の方向の一端に第1及び第2の半導体層2a,2bに対するコンタクト部を有し、かつ、梁5とフィン型積層構造Fin0〜Fin3の接続部からコンタクト部まで延びる低抵抗領域8を有する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】U字状メモリストリングを有する3次元不揮発性メモリ素子の消去速度を改善することができる不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】半導体基板上部に互いに並ぶように突出された第1及び第2垂直チャンネル膜と、前記第1垂直チャンネル膜に沿って積層されて階間絶縁膜を間に置いて隔離された複数のメモリセルゲートを含む第1ゲートグループと、前記第2垂直チャンネル膜に沿って積層されて階間絶縁膜を間に置いて隔離された複数のメモリセルゲートを含む第2ゲートグループと、前記第1及び第2垂直チャンネル膜を連結するパイプチャンネル膜と、前記パイプチャンネル膜から前記半導体基板に延長されて前記パイプチャンネル膜と前記半導体基板とを接続させるチャンネル膜延長部と、を含む。

(もっと読む)

半導体装置

【課題】酸化物半導体のようなバンドギャップが大きな半導体を用いたメモリ装置の保持特性を高める。

【解決手段】ビット線にビット線制御トランジスタを直列に挿入し、そのゲートの最低電位は十分な負の値となるようにする。ビット線制御トランジスタのゲートは電池等に接続するビット線制御回路に接続される。ビット線の最低電位はワード線の最低電位よりも高くなるようにする。外部からの電源が切れた際には、ビット線はビット線制御トランジスタによって遮断され、ビット線に蓄積された電荷が流出することが十分に抑制される。この際、セルトランジスタのゲートの電位は0Vであり、一方で、そのソースやドレイン(ビット線)の電位は、ゲートよりも十分に高いので、セルトランジスタは十分なオフ状態であり、データを保持できる。あるいは外部電源遮断時にワード線の電位を十分な負の電位とできるような回路を設けてもよい。

(もっと読む)

半導体装置の作製方法

【課題】高いオン特性を有する酸化物半導体を用いたトランジスタを提供する。高速応答及び高速駆動の可能なトランジスタを有する高性能の半導体装置を提供する。

【解決手段】チャネル形成領域を含む酸化物半導体膜を有するトランジスタの作製工程において、該酸化物半導体膜に、金属元素を含む膜と接した状態で加熱処理することにより導入された金属元素と、注入法により該金属元素を含む膜を通過して導入されたドーパントとを含む低抵抗領域を形成する。低抵抗領域はチャネル長方向においてチャネル形成領域を挟んで形成する。

(もっと読む)

半導体装置および半導体装置の制御方法

【課題】信頼性を確保しつつ、高速動作を実現することができる半導体装置を提供する。

【解決手段】抵抗変化素子10を有するメモリセル11と、メモリセル11に印加する電圧を制御する制御部80と、を備え、抵抗変化素子10は、第1の金属材料を含有する下部電極14と、第2の金属材料を含有する上部電極16と、酸素を含有する絶縁膜12と、を有しており、第1の金属材料は、第2の金属材料よりも規格化酸化物生成エネルギーが大きく、制御部80は、絶縁膜12の抵抗値を高抵抗化させる動作時および低抵抗化させる動作時において上部電極16に正電圧を印加し、絶縁膜12の抵抗値を読み出す動作時において下部電極14に正電圧を印加する。

(もっと読む)

半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供する

ことを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウ

ム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて

、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化

物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以

下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有

し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でス

パッタリングを行う。

(もっと読む)

半導体装置およびその製造方法

【課題】選択用トランジスタのゲート電極と記憶用トランジスタのゲート電極との間の耐圧を確保し、かつ閾値電圧の変動が抑制されたMONOS型メモリセルを提供する。

【解決手段】主表面SBSを有する半導体基板SUBと、主表面SBS上に形成された第1のゲート電極CGと、主表面SBS上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる第1の絶縁膜ONOとを備える半導体装置である。上記第2のゲート電極MGの最上面MGSは第1のゲート電極CGの最上面CGSより低くなっている。上記第2のゲート電極MGの最上面MGSは主表面SBSに沿うように形成されている。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

81 - 100 / 1,285

[ Back to top ]