Fターム[5F083KA01]の内容

Fターム[5F083KA01]の下位に属するFターム

Fターム[5F083KA01]に分類される特許

141 - 160 / 1,285

半導体装置および半導体装置の駆動方法

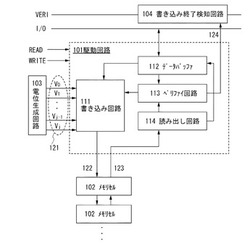

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリストリングと選択トランジスタとの間にダミーメモリトランジスタを接続された不揮発性半導体記憶装置における適正な動作を担保する。

【解決手段】素子分離絶縁膜は、第1領域においては第1の高さを有する一方、第2領域においては第1の高さよりも高い第2の高さを有する。ダミーメモリトランジスタのメモリストリング側の第1の端部に隣接する素子分離絶縁膜は前述の第1の領域に形成され、ダミーメモリトランジスタの選択トランジスタ側の第2の端部に隣接する素子分離絶縁膜は前述の第2の領域に形成されている。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】半導体記憶装置におけるデータ保持のためのリフレッシュ動作の回数を低減し、消費電力の小さい半導体記憶装置を提供する。また、三次元の形状を適用することで、集積度を高めても短チャネル効果の影響が低減され、かつ従来に比べてフォトリソグラフィ工程数の増加を抑えた半導体記憶装置を提供する。

【解決手段】溝部の設けられた絶縁膜103と、溝部を挟んで離間した一対の電極116と、溝部の側面および底面と接し、溝部の深さよりも厚さの薄い、一対の電極116と接する酸化物半導体膜106と、酸化物半導体膜106を覆うゲート絶縁膜112と、ゲート絶縁膜112を介して酸化物半導体膜106と重畳して設けられたゲート電極112と、を有するトランジスタ150と、キャパシタ160と、を有する半導体記憶装置である。

(もっと読む)

半導体記憶装置

【課題】1つの実施形態は、例えば、信号線の波形を観測するための検査用電極を容易に設けることができる半導体記憶装置を提供することを目的とする。

【解決手段】1つの実施形態によれば、メモリセルアレイと、複数の信号線と、複数の信号線引き出し部とを備えた半導体記憶装置が提供される。メモリセルアレイでは、複数のメモリセルが配列されている。複数の信号線は、複数のメモリセルに接続されている。複数の信号線引き出し部は、メモリセルアレイの周辺に配され、複数の信号線に接続されている。複数の信号線引き出し部のそれぞれは、プラグを電極として有する。プラグは、上面及び側面が保護膜で覆われている。

(もっと読む)

不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法

【課題】1つの実施形態は、例えば、メモリセルの特性を向上することに適した不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法を提供することを目的とする。

【解決手段】1つの実施形態によれば、第1のラインと第2のラインとメモリセルとを備えた不揮発性半導体記憶装置が提供される。第2のラインは、第1のラインに交差する。メモリセルは、第1のラインと第2のラインとが交差する位置に配されている。メモリセルは、抵抗変化層と上部電極層と下部電極層とダイオード層と第1の酸化膜と第2の酸化膜とを有する。上部電極層は、抵抗変化層の上に配されている。下部電極層は、抵抗変化層の下に配されている。ダイオード層は、上部電極層の上又は下部電極層の下に配されている。第1の酸化膜は、上部電極及び下部電極の少なくとも一方の電極層の側壁を覆う。第2の酸化膜は、ダイオード層の側壁を覆う。第1の酸化膜は、第2の酸化膜より厚い。

(もっと読む)

抵抗メモリ素子および関連する制御方法

【課題】電圧制御されたプログラム可能な抵抗層を有する抵抗メモリ素子とプログラミング方法を提供する。

【解決手段】参照面に平行な面に横たわり、参照面上の垂直な投影で上部電極投影を有する上部電極素子12と、参照面に平行な面に横たわり、参照面上の垂直な投影で下部電極投影を有する下部電極素子14と、上部電極素子12と下部電極素子14との間に挿入された可変性の抵抗率を有する活性層16を含む抵抗メモリ素子10において、上部電極投影と下部電極投影との間にオーバーラップ領域L3があり、オーバーラップ領域L3は少なくとも上部電極投影のコーナーおよび/または少なくとも下部電極投影のコーナーを含み、オーバーラップ領域L3の面積は、参照面上の、上部電極素子12と下部電極素子14の全投影面積の10%以下を構成する。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

不揮発性記憶素子および不揮発性記憶装置

【課題】電極と抵抗変化層の界面に小さな突起を形成することなく、低電圧での初期化が可能な不揮発性記憶素子を提供する。

【解決手段】下部電極105と上部電極107との間に介在され、両電極間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層116を備える。抵抗変化層116は、第1の抵抗変化層1161と第2の抵抗変化層1162との少なくとも2層から構成され、第1の抵抗変化層1161は第1の遷移金属酸化物116bから構成され、第2の抵抗変化層1162は、第2の遷移金属酸化物116aと第3の遷移金属酸化物116cとから構成され、第2の遷移金属酸化物116aの酸素不足度は第1の遷移金属酸化物116bの酸素不足度及び第3の遷移金属酸化物116cの酸素不足度のいずれよりも高く、第2の遷移金属酸化物116a及び第3の遷移金属酸化物116cは、第1の抵抗変化層1161と接している。

(もっと読む)

固体メモリ

【課題】固体メモリの記録層として、これまで広く用いられているGe−Sb−Te系合金に代わって、希少金属であるSbフリーでありながら、Ge−Sb−Te系合金を用いた固体メモリと遜色のない性能を有する固体メモリを提供する。

【解決手段】固体メモリ10は、物質の相変化に起因して電気特性が変化する記録層11を備えた固体メモリであって、記録層11が、ゲルマニウムとテルル4とから形成されている薄膜、および、銅とテルルとから形成されている薄膜5が積層されてなる超格子によって構成されている。

(もっと読む)

不揮発性半導体記憶装置及びフォーミング方法

【課題】フォーミング処理の時間を低減できる不揮発性半導体記憶装置を提供する。

【解決手段】複数の不揮発性メモリセルは、可変抵抗素子及び整流素子が直列接続されている。制御部は、第1のタイミングにおいて、Nを1以上の整数とするとき複数のワードラインからN本おきに第1のラインを多重選択して選択電位に設定するとともに、少なくとも多重選択されたワードラインに隣接する非選択のワードラインの電位を固定する。制御部は、第2のタイミングにおいて、上記の多重選択されたワードラインを浮遊状態にする。第2のタイミングは、第1のタイミングより後のタイミングである。制御部は、第3のタイミングにおいて、複数のビットラインから1本の第2のラインを選択してフォーミング電位に設定する。第3のタイミングは、第2のタイミングより後のタイミングである。

(もっと読む)

半導体メモリ素子及びその製造方法

【課題】垂直型トランジスタを形成する過程において、ゲートと接触する活性領域の面積を増加させてゲートの接触抵抗特性を改善し、チャネル幅を増加させる半導体メモリ素子及びその製造方法を提供する。

【解決手段】第1の方向に延長するように形成された下部ピラーと、下部ピラー上に第1の方向と垂直な第2の方向に突出するように形成された上部ピラー290と、下部ピラーの一側壁に配置された埋め込みビットライン接合領域265と、トレンチを一部埋め込む埋め込みビットライン280と、エッチング停止膜285a上に形成された少なくとも上部ピラーの外周側面の一部を露出するようにリセスされた第1の層間絶縁膜290と、第1の層間絶縁膜上に形成された第2の層間絶縁膜295と、側面の一部が露出した上部ピラーの外周側面を覆いつつ、埋め込みビットラインと相互交差するゲート320aとを備えるように形成される。

(もっと読む)

記憶素子および記憶装置

【課題】低電圧および低電流動作時における繰り返し特性が向上した記憶素子および記憶装置を提供する。

【解決手段】下部電極10、記憶層20および上部電極30をこの順に積層した記憶素子1において、記憶層20は、2.8mΩcm以上1Ωcm未満の抵抗率を有するイオン源層21と、抵抗変化層22とを有する。これにより、低電圧または低電流パルスを印加した際の記録状態から消去状態への抵抗変化層の抵抗値の回復が改善され、繰り返し特性が向上する。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】低いビットコストで積層化可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1メモリセルアレイ層10と、第1絶縁層31と、第2メモリセルアレイ層20とを有する。第1メモリセルアレイ層10は、複数の第1メモリセルMC1を具備する第1NANDセルユニットNU1を有する。第1メモリセルMC1は、第1半導体層11と、その上に形成された第1ゲート絶縁膜12と、第1浮遊ゲート13とを有する。第2メモリセルアレイ層20は、複数の第2メモリセルMC2を具備する第2NANDセルユニットNU2を有する。第2メモリセルMC2は、第2浮遊ゲート23と、第2ゲート絶縁膜22と、第2半導体層21とを有する。上下に連続する第1及び第2浮遊ゲート13,23の第1の方向の両側面に第1の方向と直交する第2の方向に延びる制御ゲート33が形成される。

(もっと読む)

半導体メモリ装置

【課題】DRAMに必要なキャパシタの容量を低減し、高度に集積化したDRAMを提供する。

【解決手段】分割ビット線型DRAMにおいて、サブビット線をワード線の下に形成し、ビット線をワード線の上に形成する。分割ビット方式でサブビット線の寄生容量が低減し、かつ、セルトランジスタのオフ抵抗を必要に応じて高いものとすることによって、キャパシタの容量を通常のDRAMの1/10以下とすることができる。このため、スタック型キャパシタであっても、その高さを従来のものの1/10以下とできるので、その上にビット線を設けることも容易となる。また、セルトランジスタの構造を特殊なものとすることでメモリセルあたりの面積を4F2とできる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルアレイに用いられる配線の抵抗を低減することができる半導体記憶装置の製造方法を提供する。

【解決手段】一の実施の形態に係る半導体記憶装置の製造方法は、第1配線層を積層する工程と、第1配線層の上方にメモリセル層を積層する工程と、メモリセル層の上方に、後の研磨工程を減速させるためのストッパ膜を積層する工程とを備える。また、製造方法は、ストッパ膜、メモリセル層、及び第1配線層をエッチングする工程と、ストッパ膜、メモリセル層、及び第1配線層を層間絶縁膜により埋め込んだ後、ストッパ膜に達するまで研磨する工程と、ストッパ膜及び層間絶縁膜に窒化処理を実行して、ストッパ膜及び層間絶縁膜の表面にそれぞれ調整膜及びブロック膜を形成する工程とを備える。そして、製造方法は、調整膜の上方に、エッチングされた第1配線層と交差して各交差部にメモリセルが配置されるように、第2配線層を形成する工程を備える。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体記憶装置

【課題】擬似的に記憶容量を増加させる。

【解決手段】ダミービット線領域において半導体基板に対して垂直方向に延びる一対の柱状部およびその連結部に沿って形成されるメモリストリングを構成する第1シリコンピラーと、シャント領域において半導体基板に対して垂直方向に延びる一対の柱状部およびその連結部に沿って形成されるメモリストリングを構成する第2シリコンピラーと、第1シリコンピラーおよび第2シリコンピラーの一対の柱状部の一方に接続され、メモリストリングの上方に形成されたソース線と、第1シリコンピラーの一対の柱状部の他方に接続され、ソース線と同レベルに形成された第1配線、および第2シリコンピラーの一対の柱状部の他方に接続され、ソース線と同レベルに形成された第2配線と、を具備し、第1配線はダミービット線に接続され、第1配線および第2配線は同レベルで接続されている。

(もっと読む)

不揮発性メモリ装置

【課題】一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供することによって、読出しマージン減少による信頼性の下落を防止できる不揮発性メモリ装置が提供される。

【解決手段】本発明の実施形態による不揮発性メモリ装置は、基板と直交する方向に積層された複数のメモリセルを含むメモリセルアレイと、ワードラインを通じて前記メモリセルアレイに連結された行選択回路と、前記ワードラインに提供される電圧を発生する電圧発生回路と、を含み、前記電圧発生回路は、目標電圧レベルまで段階的に増加させる方式に前記電圧を発生する。本発明の実施形態による不揮発性メモリ装置は、一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供できる。したがって、読出しマージン減少による信頼性の下落が防止され得る。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

141 - 160 / 1,285

[ Back to top ]