Fターム[5F083LA02]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | メモリセルユニット間レイアウト (635)

Fターム[5F083LA02]に分類される特許

61 - 80 / 635

半導体装置

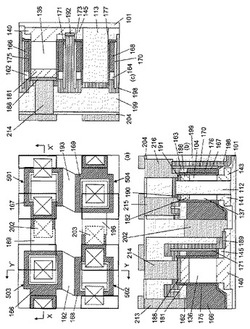

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

半導体メモリ装置およびその製造方法

【課題】消去、書き込みを繰り返してもON/OFF比を高く維持できる半導体メモリ装置を提供する。

【解決手段】本発明に係る半導体メモリ装置100は、基板10と、基板10の上に形成された炭化シリコン層20と、炭化シリコン層20の上に形成された金属酸化物層30と、金属酸化物層30と電気的に接続された第1電極40と、基板10と電気的に接続された第2電極50と、を含む。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートの閾値電圧の変動が抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、交互に積層された複数の電極層と複数の第1絶縁層とを有する第1積層体と、第1積層体を貫通する第1ホールの側壁に設けられたメモリ膜と、第1ホール内に設けられたメモリ膜の内側に設けられた第1チャネルボディ層と、第1積層体の上に設けられた層間絶縁膜と、層間絶縁膜の上に設けられた選択ゲート電極層と、選択ゲート電極層の上に設けられた第2絶縁層と、を有する第2の積層体と、第1ホールに連通し第2積層体および層間絶縁膜を貫通する第2ホールの側壁に設けられたゲート絶縁膜と、第2ホール内におけるゲート絶縁膜の内側に設けられ、第1チャネルボディ層とつながった第2チャネルボディ層と、を備える。選択ゲート電極層と第2絶縁層との界面における第2ホールの径は選択ゲート電極層と層間絶縁膜との界面における第2ホールの径よりも小さい。

(もっと読む)

半導体記憶装置

【課題】記憶素子の加工が容易であり、かつ、記憶素子が安定した特性を有するメモリを提供する。

【解決手段】本実施形態によるメモリは、半導体基板を備える。複数のアクティブエリア列は、半導体基板上に設けられ第1の方向に配列された複数のアクティブエリアをそれぞれが含む複数のアクティブエリア列であり、第1の方向に対して直交する第2の方向に隣接するアクティブエリアは互いに半ピッチずつずれて配置されている。複数のセルトランジスタは、アクティブエリアのそれぞれに対応して設けられている。複数の記憶素子は、複数のセルトランジスタの一端に電気的に接続されている。上部電極は、複数のアクティブエリア列のうち第2の方向に隣接する第1および第2のアクティブエリア列に対応する複数の記憶素子に交互に接続されている。ビット線は、第1および第2のアクティブエリア列に含まれる複数のセルトランジスタの他端に電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造のフラッシュメモリーの提供

【解決手段】

半導体基板1上にシリコン窒化膜2及びシリコン酸化膜3が選択的に設けられ、シリコン酸化膜3上には、選択的に横(水平)方向エピタキシャルSi層5が設けられ、Si層5の両側面には、それぞれ側面を接して横(水平)方向エピタキシャルSi層6が設けられた構造からなる半導体層が素子分離領域のシリコン窒化膜4により絶縁分離されている。Si層6の残りの周囲には第1のゲート酸化膜10を介して包囲型フローティングゲート電極11が設けられ、包囲型フローティングゲート電極11の周囲には第2のゲート酸化膜12を介して包囲型コントロールゲート電極13(ワード線)が設けられ、Si層5には概略ソースドレイン領域9が設けられている2重包囲型ゲート電極を有するMIS電界効果トランジスタより構成したフラッシュメモリー。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの制御性を向上した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、構造体と、複数の半導体層と、メモリ膜と、接続部材と、導電部材と、を備える。前記構造体は、メモリ領域と非メモリ領域とを有する基板の前記メモリ領域の上に設けられる。前記構造体は、前記基板の主面に対して垂直な第1軸に沿って積層され複数の電極膜を含む。前記半導体層は、前記構造体を前記第1軸に沿って貫通する。前記メモリ膜は、前記複数の電極膜と前記半導体層との間に設けられる。前記接続部材は、前記基板と前記半導体層との間に設けられる。前記接続部材は、隣り合う2つの前記半導体層のそれぞれの端部と接続される。前記導電部材は、前記基板と前記接続部材との間で、前記メモリ領域から前記非メモリ領域に延在して設けられる。前記導電部材は、前記非メモリ領域の上に設けられた凹部を有する。前記凹部内には、第1シリサイド部が設けられる。

(もっと読む)

補助電極構造を備えた立体型DRAM

【課題】補助電極構造を備えた立体型DRAMの提供。

【解決手段】本補助電極構造を備えた立体型DRAMは、基板(10)、該基板(10)上に形成された少なくとも一つのビット線(11)、該ビット線(11)上の成長領域(111)に形成された柱状体(20)、補助電極(40)、該基板(10)に平行で且つ該ビット線(11)に垂直なワード線(60)、該柱状体(20)に接続されたコンデンサ(70)を包含し、該ビット線(11)は該基板(10)にドーパントをドープし並びに拡散を実行して形成され、該補助電極(40)は該ビット線(11)の間隔領域(112)に設置され、並びに該柱状体(20)に隣接し、該ワード線(60)は該補助電極(40)と絶縁されて設置され、並びに該ビット線(11)と組み合わされて該コンデンサ(70)に電子データを入出力する。本発明は該補助電極(40)の設置により、該ビット線(11)の抵抗を制御できるようにすることで、該ビット線(11)の導電能力を向上する。

(もっと読む)

相変化メモリ

【課題】三次元構造を有する相変化メモリの熱ディスターブを抑制する。

【解決手段】三次元構造を有する相変化メモリにおいて、選択用MOSトランジスタのゲート絶縁膜として、高い熱伝導率を有する材料を使用し、相変化記録膜からSiチャネル層に伝達する熱を良好にゲート電極に拡散させる。これにより、記録ビットから発生する熱が非選択の隣接ビットに拡散し、隣接ビットのデータを消去する熱ディスターブを抑制する。高い熱伝導率を有するゲート絶縁膜材料としては、BN、Al2O3、AlN、TiO2、Si3N4、ZnOなどを挙げることができる。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

不揮発性半導体記憶装置

【課題】高い信頼性を有し且つ安価な不揮発性半導体記憶装置を提供する。

【解決手段】この不揮発性半導体記憶装置において、メモリストリングスは、基板に対して垂直方向に延びる一対の柱状部、及び前記一対の柱状部の下部を連結させるように形成された連結部を有する半導体層と、前記柱状部の側面を取り囲むように形成された電荷蓄積層と、前記柱状部の側面及び前記電荷蓄積層を含む第1の絶縁膜と、前記柱状部の側面及び前記第1の絶縁膜を覆うように形成された第1導電層と、前記連結部の周囲に形成される第2の絶縁膜と、前記連結部に前記ゲート絶縁膜を介して形成される第2導電層とを備える。

(もっと読む)

集積回路装置及びその製造方法

【課題】FinFETの特性が均一な集積回路装置及びその製造方法を提供する。

【解決手段】実施形態に係る集積回路装置は、半導体基板の上面に形成され、第1方向に延びる複数本のフィンと、前記フィン間に配置された素子分離絶縁膜と、前記第1方向に対して交差した第2方向に延び、前記素子分離絶縁膜上に設けられたゲート電極と、前記フィンを前記ゲート電極から絶縁する絶縁膜と、を備える。そして、連続して配列された複数本の前記フィンが配置された第1領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも下方の第1の位置に位置し、前記第1領域から見て前記第2方向に位置する第2領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも上方の第2の位置に位置する。また、前記第2領域においては、前記素子分離絶縁膜が前記フィンの側面の全体を覆っている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、コンタクトプラグが形成されるセル部と、前記コンタクトプラグが形成されない周辺回路部とを平坦化できる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に最上部が第1の絶縁膜からなる配線層を形成する工程と、

前記半導体基板と前記配線層とを被う第2の絶縁膜を形成する工程と、前記第2の絶縁膜の所定の領域をエッチングし、前記配線層と前記半導体基板とを露出させる開口部を形成する工程と、前記開口部内と前記第2の絶縁膜上とに導電膜を形成する工程と、前記第1の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有し、前記第2の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有する条件で、前記第2の絶縁膜と前記導電膜とを前記第1の絶縁膜が露出するようCMP法で除去し、コンタクトプラグを形成する工程を有する半導体装置の製造方法。

(もっと読む)

抵抗変化メモリ

【課題】隣接するセル間の電流のリークを防止することができる抵抗変化メモリを提供することを可能にする。

【解決手段】本実施形態による抵抗変化メモリは、第1配線と、前記第1配線と交差する第2配線と、前記第1配線と前記第2配線との交差領域に設けられ、前記第1配線に接続する第1電極と、前記第2配線に接続し、前記第1電極に対向する第2電極と、前記第1電極と前記第2電極との間に設けられた抵抗変化層と、前記第2電極の側部に設けられ、前記第2電極の側部との間に空隙を形成する第1絶縁層および第1半導体層のいずれか一方と、を備えている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】信頼性を向上させることができる半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、積層して設けられた複数のゲート電極と、前記ゲート電極の間に設けられた絶縁膜と、を有した積層体と、前記積層体を貫く半導体ピラーと、前記半導体ピラーと前記ゲート電極との間に空隙を介して設けられた電荷蓄積層と、前記電荷蓄積層と前記ゲート電極との間に設けられたブロック絶縁層と、を有したメモリセルを積層方向に複数備えている。そして、前記複数の各メモリセル毎に、前記電荷蓄積層と前記半導体ピラーとの間の距離を保つ支持部が設けられている。

(もっと読む)

半導体装置

【課題】抵抗変化型記憶素子を用いた半導体装置の耐タンパ性を向上させること。

【解決手段】半導体装置は、1ビットのセルデータを記憶するユニットセル(10)と、制御回路(100)とを備える。ユニットセル(10)は、n個(nは2以上の整数)の抵抗変化型記憶素子(31)を備える。それらn個の抵抗変化型記憶素子(31)のうち少なくとも1つが、セルデータが記録される有効素子(40)である。セルデータの読み出し時、制御回路(100)は、少なくとも有効素子(40)を選択し、有効素子(40)に記録されているデータをセルデータとして読み出す。

(もっと読む)

半導体装置

【課題】半導体層上での占有面積の増加を抑制しながらキャパシタ素子の容量を増大させることができる半導体装置を提供する。

【解決手段】この半導体装置は、素子分離溝2によって分離された複数の活性領域Aを有するn型半導体層3と、素子分離溝2の側壁2bを覆う側壁被覆部17を有する容量膜15と、容量膜15に積層された電極膜18とを含む。n型半導体層3、容量膜15および電極膜18によってキャパシタCが形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】正確に書き込み動作を行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】

複数の素子分離絶縁膜は、半導体層中に形成され、第1方向を長手方向とする。複数の素子形成領域は、素子分離絶縁膜により分離して形成される。素子形成領域にはメモリストリングが形成される。複数の素子形成領域群が素子形成領域により構成される。メモリセルアレイは、第1方向と直交する第2方向において、前記素子形成領域群の間隔が前記素子形成領域群の中の前記素子形成領域の間隔より大きくされている。制御回路は、前記メモリセルアレイに対する書き込み動作を、前記素子形成領域群ごとに実行する。

(もっと読む)

半導体装置の製造方法

【課題】埋込ワード線の高さにばらつきのない半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、複数の素子分離領域を形成すると共に、素子分離領域間に素子形成領域を形成する工程と、素子形成領域に交差する第1の方向に延在するゲート電極溝を形成する工程と、ゲート電極溝の内壁にゲート絶縁膜を形成する工程と、ゲート電極溝の内壁にゲート絶縁膜を介して第1導電膜を形成する工程と、ゲート電極溝内を埋め込むように第2導電膜を形成する工程と、第2導電膜上に平坦化膜を形成する工程と、第2導電膜が露出するように平坦化膜をエッチングして除去する第1のエッチング工程と、第2導電膜がゲート電極溝の下部に残留するように第2導電膜をエッチングする第2のエッチング工程と、第1導電膜が前記ゲート電極溝の下部に残留するように第1導電膜をエッチングする第3のエッチング工程と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】複数のサポート膜間における開口の位置ずれ発生を抑制できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に、第1の犠牲膜、第1のサポート膜、第2の犠牲膜及び第2のサポート膜を順次形成し、これらの膜を貫通するホールを形成し、ホールの内表面を覆い、かつ第2のサポート膜及び第1のサポート膜に接続される王冠型電極を形成し、王冠型電極と第2のサポート膜との接続を少なくとも一部分維持する第1のパターンで、第2のサポート膜に第1の開口を形成し、第1の開口を通じて第2の犠牲膜の一部又は全部を除去し、第1の開口を利用して第1のサポート膜に第2の開口を形成し、第2の開口を通じて第1の犠牲膜を全て除去する、ことを特徴とする。

(もっと読む)

不揮発性メモリセルおよび不揮発性メモリ

【課題】 スタティックノイズマージンを損なうことなく、揮発性記憶部および不揮発性記憶部間のストアとリコールを行える不揮発性メモリセルを提供する。

【解決手段】 不揮発性記憶部12は、揮発性記憶部11のノードV1とバイアス供給ノードNSとの間に直列に介挿されたNチャネルトランジスタTw1および抵抗変化型素子R1と、揮発性記憶部11のノードV2とバイアス供給ノードNSとの間に直列に介挿されたNチャネルトランジスタTw2および抵抗変化型素子R2を有する。ストア時、NチャネルトランジスタTw1およびTw2はONとされ、抵抗変化型素子R1およびR2は、ノードV1(V2)からバイアス供給ノードNSに向かう電流を通過させたときに高抵抗となり、逆方向の電流を通過させたときに低抵抗となる。リコール時は、揮発性記憶部11のフリップフロップに対する電源電圧を立ち上げる。

(もっと読む)

61 - 80 / 635

[ Back to top ]