Fターム[5F083LA02]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | メモリセルユニット間レイアウト (635)

Fターム[5F083LA02]に分類される特許

21 - 40 / 635

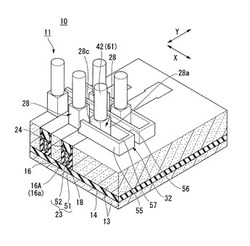

半導体装置及びその製造方法、並びにデータ処理システム

【課題】本発明は、第1の不純物拡散領域と第2の不純物拡散領域との間に位置するピラーを流れるドレイン電流が、隣接するピラーにリーク電流として流れることを防止可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板13に立設されたピラー28と、Y方向に延在するように半導体基板13に設けられ、Y方向と交差するX方向において対向するピラー28の第2の側壁を露出する第1の溝16と、ピラー28の第2の側壁の下部に設けられた第1の不純物拡散領域と、ピラー28の上端に設けられた第2の不純物拡散領域と、半導体基板13に内設され、第1の溝16の底16Aに配置された絶縁層14と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体記憶装置

【課題】動作の安定性を向上できる半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、複数のメモリセルと、複数のワード線と、複数のビット線と、複数の選択トランジスタと、配線層と、を備える。複数のメモリセルは、第1方向及び第1方向と直交する第2方向にそれぞれ配置される。複数のワード線は、それぞれ第1方向に延在して設けられる。複数のビット線は、それぞれ第2方向に延在し、第1方向及び第2方向と直交する第3方向に複数のワード線と離間して設けられる。複数の選択トランジスタは、複数のストリングにそれぞれ設けられる。配線層は、選択トランジスタのソースと同電位に設けられる。配線層は、第3方向にみて複数のワード線とそれぞれ重なる複数の第1重複部分を有する。配線層のパターンが繰り返される単位領域において、複数の第1重複部分のそれぞれの面積は同じである。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、ビットコンタクト用の溝部12を挟んで対向する一対の埋め込みゲート用の溝部8a,8bの底部に不純物が拡散された領域13a,13bと、ビットコンタクト用の溝部12に不純物が拡散された領域13cと、が結合されて設けられた第1の不純物拡散層13と、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置の製造方法

【課題】第1の領域において、第2の絶縁膜からゲート絶縁膜への酸化剤の侵入を防止する。第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去する。

【解決手段】半導体装置の製造方法では、基板の第1の領域には第1の積層体を形成し第2の領域には複数の第1の配線を形成する。第1の絶縁膜をマスクとして、第1の領域の主面に第1の不純物のイオン注入を施す。第1の積層体の側壁を覆いかつ複数の第1の配線間を埋設するように第2の絶縁膜を形成する。第2の絶縁膜をマスクとして、第1の領域の主面に第2の不純物のイオン注入を施す。第1のエッチングにより、第2の絶縁膜を第1の絶縁膜に対して選択的に除去した後、基板に熱処理を行う。

(もっと読む)

3次元不揮発性メモリ素子及びその製造方法

【課題】消去動作の際、充分な量の正孔を生成させて消去特性を確保することができる3次元不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】基板から突出されたチャンネル膜と、チャンネル膜に沿って積層された複数のメモリセルと、チャンネル膜の一側端と繋がれたソースラインと、チャンネル膜の他側端と繋がれたビットラインと、チャンネル膜の一側端とソースラインとの間に介在されて、Pタイプの不純物がドープされた第1ジャンクションと、チャンネル膜の他側端と前記ビットラインとの間に介在されて、Nタイプの不純物がドープされた第2ジャンクションと、を含む。

(もっと読む)

不揮発性メモリ装置、不揮発性メモリ装置のプログラム方法、不揮発性メモリ装置を含むメモリシステム

【課題】向上された信頼性を有する不揮発性メモリ装置のプログラム方法が提供される。

【解決手段】本発明のプログラム方法は、第1メモリセルトランジスターの閾値電圧がプログラム状態から移動する傾向を判別する段階と、判別結果に応答して、複数の検証電圧の中で第1検証電圧を選択する段階と、第1メモリセルトランジスターの閾値電圧が変化するように第1メモリセルトランジスターをプログラムする段階と、で構成される。プログラムする段階は第1メモリセルトランジスターの閾値電圧が十分に変化されたかを第1検証電圧を利用して検証する段階を含む。判別する段階は第1メモリセルトランジスターの閾値電圧の第1範囲からの変化を判別する段階を含む。

(もっと読む)

半導体装置およびその作製方法

【課題】ノーマリーオフの電気特性を有し、オン電流の高い、酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを用いた高速動作が可能な半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳して設けられたゲート電極と、少なくともゲート電極を覆って設けられた、開口部を有する層間絶縁膜と、層間絶縁膜上に設けられ、開口部を介して酸化物半導体膜と接する配線と、を有し、少なくとも酸化物半導体膜と配線とが接する領域の、下地絶縁膜および酸化物半導体膜の間に、絶縁膜および絶縁膜上に設けられたバッファ層を有する半導体装置である。

(もっと読む)

半導体装置

【課題】低電圧動作が可能なSRAMをそのセル面積の増加を抑えて実現する。

【解決手段】第1方向Sに並ぶP型ウェル領域20、N型ウェル領域30、P型ウェル領域40に、第2方向Tに隣接するメモリセル1aが形成される。各メモリセル1aは、P型ウェル領域20,40に形成されたトランスファトランジスタTf1,Tf2及びドライバトランジスタDr1,Dr2、N型ウェル領域30形成されたロードトランジスタLo1,Lo2を備える。SRAM1では、第2方向Tに隣接するメモリセル1aの、互いのトランスファトランジスタTf1のゲート電極がワード線WL1に、互いのトランスファトランジスタTf2のゲート電極がワード線WL2に、それぞれ電気的に接続される。ワード線WL1はP型ウェル領域20に、ワード線WL2はP型ウェル領域40に、それぞれ電気的に接続される。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。第n行のメモリブロックはサブビット線SBL_n_mと複数のメモリセルを有する。メモリセルはトランジスタと容量素子を直列に接続し、容量素子の電極の一をサブビット線SBL_n_mに接続する。さらに第n行のメモリブロックは書き込みトランジスタWTr_n_mと読み出しトランジスタRTr_n_mを有し、また、読み出しトランジスタRTr_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの電位変動を増幅回路AMP_n_mで増幅する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】熱工程による負担を減らし、メモリセル特性の向上を図る。

【解決手段】本実施形態による不揮発性半導体記憶装置の製造方法よれば、基板上30に、コントロールゲートCGとなる導電膜を形成する。前記導電膜の上面から下面まで貫通するホール40を形成する。前記ホールの内面上に、ブロック絶縁膜150を形成する。前記ブロック絶縁膜上に、電荷蓄積膜151を形成する。前記電荷蓄積膜上に、トンネル絶縁膜152を形成する。前記トンネル絶縁膜上に、半導体層SPを形成する。前記半導体層上に、前記ホールが埋め込まれないように酸素乖離の触媒作用を有する材料を含む膜153を形成する。前記ホールの内側から前記膜を介して、前記トンネル絶縁膜と前記半導体層との界面を酸化する。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】 可変抵抗素子への電圧印加極性が異なる2種類の書き込み動作後の各ベリファイ動作を夫々低消費電力且つ高速に実行可能な半導体記憶装置を提供する。

【解決手段】 書き込み回路22が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の電気抵抗を低抵抗化させるセット動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の電気抵抗を高抵抗化させるリセット動作を夫々実行可能に構成され、読み出し回路21が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第1読み出し動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第2読み出し動作を夫々実行可能に構成されている。

(もっと読む)

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。また信頼性の高い半導体装置を提供する。

【解決手段】チャネル形成領域と、ソース領域またはドレイン領域を有する島状半導体膜131と、ゲート絶縁膜と、ゲート電極103とを有する薄膜トランジスタと、層間絶縁膜と、層間絶縁膜中に形成され、ソース領域またはドレイン領域の一方に達する複数のコンタクトホールを含む第1のコンタクトホール142と、ソース領域またはドレイン領域の他方に達する第2のコンタクトホール141とを有し、第2のコンタクトホール141の径は、第1のコンタクトホール142に含まれる複数のコンタクトホール142のそれぞれの径より大きく、第1のコンタクトホールの底面積の合計と、第2のコンタクトホール141の底面積は等しい半導体装置に関する。

(もっと読む)

半導体装置の製造方法

【課題】

実施形態は、ゲート配線の抵抗が増大することを防止可能な半導体装置の製造方法を提供する。

【解決手段】

本実施形態の半導体装置の製造方法は、第1領域及び第2領域の半導体素子を形成するために、半導体基板、前記半導体基板上の第1絶縁膜、前記第1絶縁膜上の電荷蓄積層を積層し、所望のトレンチを形成する工程と、前記トレンチに素子分離膜を形成する工程と、前記素子分離膜及び前記電荷蓄積層上にストッパー膜30を形成する工程と、前記第2領域を第2絶縁膜で被膜し、前記第1領域の前記ストッパー膜30と前記素子分離膜をエッチバックする工程と、前記エッチバックされた素子分離膜、前記電荷蓄積層、第2領域の前記ストッパー膜30上に第3絶縁膜を介して配線を形成する工程とを備えることを特徴とする。

(もっと読む)

半導体装置

【課題】半導体チップに構成されるメモリコアにおける電源系を容易に分離可能な配線構造を実現しスループットの向上が可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体チップC1に複数のメモリコア(DRAMコア)が構成される。各メモリコアは、第1電源によって動作しパラレルデータを双方向に伝送するデータバスを駆動する第1回路領域と、第1電源と分離された第2電源によって動作しデータバスを伝送されるパラレルデータと外部端子を介して入出力されるシリアルデータとを双方向に変換する第2回路領域と含む。第1貫通電極群23は、第1回路領域に第1電源を供給する複数の貫通電極をY方向に並べて配置され、第2貫通電極群21は、第2回路領域に第2電源を供給する複数の貫通電極をY方向と交差するX方向に並べて配置される、それぞれの貫通電極群を経由して第1及び第2電源の配線群が互いに分離した配置で形成される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法とデータ書き換え方法

【課題】データ保持時間を、マスクROMと同様の無限大とすることができる、長期にわたりデータを保持できる信頼性の高いEEPROMを提供する。

【解決手段】不揮発性半導体記憶装置は、所定のセンスレベルに対して熱平衡状態しきい値電圧が正方向である第1の不揮発性半導体記憶素子100に正のデータを記憶し、熱平衡状態しきい値電圧が負方向である第2の不揮発性半導体記憶素子200に負のデータを記憶することでデータ保持時間を無限大にする。

(もっと読む)

半導体不揮発性メモリ及びデータ書き込み方法

【課題】データ書き込み時における書き込み回数を減らし、且つ読み出し精度を高めることが可能な半導体不揮発性メモリ及びデータ書き込み方法を提供する。

【解決手段】書き込むべきデータの値に対応した量の電荷を電荷蓄積部に注入することによって書き込みを行うデータ書き込み手段を有し、データ書き込み手段によるデータの書き込みに先立ち、電荷蓄積部各々から読み出し電流を送出させ、読み出し電流が最大読み出し電流閾値よりも大となる電荷蓄積部に、この読み出し電流が最大読み出し電流閾値を下回るまで電荷を注入する初期化書き込みを行う。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】非選択メモリセルに流れる逆方向電流を低減させた不揮発性半導体記憶装置を提供することを目的とする。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、複数のメモリセルを有するメモリセルアレイと、選択第1配線に選択第1配線電圧を供給し、非選択第1配線に非選択第1配線電圧を供給する第1配線制御回路と、アクセス対象となるメモリセルに接続された第2配線である選択第2配線に選択第2配線電圧を供給し、その他の第2配線である非選択第2配線に非選択第2配線電圧を供給する第2配線制御回路とを備え、メモリセルは、第1ダイオードのアノード側に第2配線が接続され、第1ダイオードのカソード側に第1配線が接続され、メモリセルアレイは、第2配線制御回路及びメモリセル間の第2配線に挿入され、第2配線制御回路側をアノード、メモリセル側をカソードとする第2ダイオードを有することを特徴とする。

(もっと読む)

21 - 40 / 635

[ Back to top ]