Fターム[5F083LA02]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | メモリセルユニット間レイアウト (635)

Fターム[5F083LA02]に分類される特許

121 - 140 / 635

可変抵抗素子のフォーミング処理方法および不揮発性半導体記憶装置

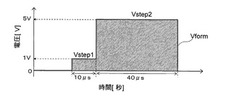

【課題】 パルスフォーミングと同程度の短時間で、スイッチング動作時の書き換え電流がDCフォーミングで達成される書き換え電流程度に抑えることのできる可変抵抗素子のフォーミング処理方法を提供する。

【解決手段】

可変抵抗素子に電圧パルスを印加して、製造直後の初期高抵抗状態にある可変抵抗素子をスイッチング動作が可能な可変抵抗状態に変化させるフォーミング処理が、可変抵抗素子が低抵抗化する閾値電圧より低い電圧振幅の第1パルスを可変抵抗素子の両電極間に印加する第1ステップと、第1ステップの後に、当該第1パルスと同極性であって閾値電圧以上の電圧振幅の第2パルスを可変抵抗素子の両電極間に印加する第2ステップとを含んでなる。

(もっと読む)

不揮発性記憶素子及びその製造方法並びに不揮発性記憶装置

【課題】不揮発性記憶素子の初期化電圧のばらつきの発生を抑えつつ、従来に比べて初期化電圧の低減を図ることができる抵抗変化型の不揮発性記憶素子を提供する。

【解決手段】第1の層間絶縁層102、下部電極105、上部電極107及び抵抗変化領域106を備え、抵抗変化領域106は積層された第1の抵抗変化領域106bと第2の抵抗変化領域106aを有し、第1の抵抗変化領域106bは第1の遷移金属酸化物で構成され、第2の抵抗変化領域106aは第2の遷移金属酸化物で構成され、第2の遷移金属酸化物の酸素不足度は第1の遷移金属酸化物の酸素不足度より小さく、抵抗変化領域106の上面は上部電極107と接し、抵抗変化領域106の底面は下部電極105及び第1の層間絶縁層102と接し、抵抗変化領域106の底面と下部電極105の接する面の面積は抵抗変化領域106の上面と上部電極107の接する面の面積より小さい。

(もっと読む)

半導体記憶装置

【課題】不揮発性の記憶装置を有するCAMとする際に、メモリセルの低消費電力化を図ることのできる半導体記憶装置を提供することを課題の一とする。また、データの書き込みを繰り返し行う際の劣化をなくすことができる半導体記憶装置を提供することを課題の一とする。また、メモリセルの高密度化が可能な不揮発性の記憶装置を提供する。

【解決手段】酸化物半導体を半導体層に有する第1のトランジスタ及び当該第1のトランジスタをオフ状態とすることで書き込んだデータに対応する電位を保持できる容量素子を有するメモリ回路と、書き込んだ電位を参照するための参照回路を有し、参照回路を構成する第2のトランジスタの導通状態を検出することで、整合するデータのアドレスを取得し、高速な検索機能を可能にした半導体記憶装置である。

(もっと読む)

半導体記憶装置

【課題】ジュール熱を利用して情報を記憶する相変化メモリを採用した半導体記憶装置において、誤ライト動作を起こす可能性を抑制する。

【解決手段】本発明に係る半導体記憶装置は、積層体内のいずれかの半導体層に第1の電流を印加して積層体内の複数の半導体層の側面に配置されている抵抗変化材料層を一括して結晶化した後、第1の電流を印加した半導体層以外の半導体層に第2の電流を印加する。

(もっと読む)

ダイオードストラッピングを備えた熱アシストフラッシュメモリ

【課題】フラッシュメモリの動作速度及び耐久性を向上させる技術の提供。

【解決手段】メモリが、行及び列を含むメモリセルのアレイを有している。該メモリは、アレイ内の単数又は複数のワード線上の第1の離隔位置のセットに第1のバイアス電圧を印加するとともに、単数又は複数のワード線上の第2の離隔位置のセットに第1のバイアス電圧とは異なる第2のバイアス電圧を印加する、ワード線に結合された回路部を有し、第1の離隔位置のセットにおける位置は、第2の離隔位置のセットの位置の間に介在しており、それにより、第1の離隔位置のセットにおける位置と第2の離隔位置のセットにおける位置との間に、単数又は複数のワード線の加熱をもたらす電流の流れが誘導される。

(もっと読む)

熱アシスト誘電体電荷トラップメモリ

【課題】

誘電体電荷トラップメモリの動作速度及び/又は耐久性を向上させる技術を提供する。

【解決手段】

メモリデバイスは、ワードライン及びビットラインを含む誘電体電荷トラップ構造メモリセルのアレイを含む。該アレイに、読み出し、プログラム及び消去の動作を制御するように構成された制御回路が結合される。コントローラは、該アレイのメモリセル内の誘電体電荷トラップ構造を熱アニールする支援回路を備えるように構成される。熱アニールのための熱を誘起するために、ワードラインドライバ及び前記ワードライン終端回路を用いて、ワードラインに電流を誘起することができる。熱アニールは、サイクルダメージからの回復のために、通常動作とインターリーブされて適用されることが可能である。また、熱アニールは、消去のようなミッション機能中に適用されることもでき、それにより該機能の性能を向上させ得る。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】メモリセルが3次元的に積層された不揮発性半導体記憶装置を工程数の増大を抑制しながら製造可能な不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】半導体基板101上にスペーサ膜104とチャネル半導体膜103とを交互に複数層積層させた積層構造を形成し、積層構造に第1の方向に延在するトレンチを形成する。ついで、トレンチからチャネル半導体膜103を第2の方向にリセスして空隙を形成し、空隙内のチャネル半導体膜103上にトンネル誘電体膜108を形成し、フローティングゲート電極膜109を埋め込む。その後、第1の方向に隣接するメモリセル間でフローティングゲート電極膜109が分離され、チャネル半導体膜103が分離されないように、積層構造を第1の方向に所定の間隔で分割する。また、第2の方向に隣接するメモリセル間でチャネル半導体膜103が分離されるように、積層構造を第2の方向に所定の間隔で分割する。

(もっと読む)

半導体装置

【課題】微細化が可能であるメモリセル構造を備える半導体装置を提供する。

【解決手段】ワード線と、ビット線と、電源ノードと、ビット線と電源ノードとの間にPN結合を成す第1及び第2の領域並びに第2の領域とPN結合を成す第3の領域を少なくとも有するメモリ素子と、メモリ素子の第2の領域とは独立して設けられてメモリ素子の第2の領域と電気的に接続された第1の電極及び前記ワード線に接続された第2の電極を有するキャパシタと、を備える。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供する。また、不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】トレンチを有する絶縁層に接して、ソース領域またはドレイン領域として機能する領域の膜厚が、チャネル形成領域として機能する領域の膜厚よりも厚い酸化物半導体層を形成する。該酸化物半導体層を用いたトランジスタは、ソース抵抗またはドレイン抵抗を低減することができると共に、しきい値のバラツキ、電気特性の劣化、ノーマリーオン化を抑制することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル抵抗を減少させてオン電流を増加させることが可能で、各トランジスタを独立して安定して動作させることの可能な半導体装置を提供する。

【解決手段】ゲート電極用溝18の底部18cから突き出すように形成されたフィン部15と、ゲート電極用溝18及びフィン部15の表面を覆うゲート絶縁膜21と、ゲート電極用溝18の下部に埋め込まれ、ゲート絶縁膜21を介してフィン部15を跨ぐように形成されたゲート電極22と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆う第1の不純物拡散領域28と、第2の側面18bに配置されたゲート絶縁膜21の下端部以外の部分を覆う第2の不純物拡散領域29とを備え、ゲート電極用溝18の深さが半導体基板13の表層13aから150〜200nmであり、ゲート電極用溝18の底部18cからフィン部15の上部15aまでの高さが10〜40nmである。

(もっと読む)

半導体装置

【課題】先端プロセスでは、MOSのゲートトンネルリーク電流が増大し、低リーク電流での待機が必要となる半導体装置では問題となる。

【解決手段】電源線とソース線との電位差である複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路を具備する。負荷型P型MOS及び駆動型N型MOSのゲート絶縁膜厚は、4nm以下である。電源電圧制御回路は、動作状態では前記電源電圧を第1電圧とし、待機状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御して、オフ状態での負荷型P型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、駆動型N型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を動作状態に対し待機状態の方を小さくする。

(もっと読む)

半導体集積回路装置

【課題】本発明は、従来のSRAMメモリセルでは、Pウエル領域の基板へのコンタクトをとるために、拡散層の形を鍵状に曲げる必要があった。このため、対称性が悪く微細化が困難であるという問題があった。

【解決手段】SRAMセルを構成するインバータが形成されたPウエル領域PW1、PW2が2つに分割されてNウエル領域NW1の両側に配置され、トランジスタを形成する拡散層に曲がりがなく、配置方向が、ウエル境界線やビット線に平行に走るように形成される。アレイの途中には、基板への電源を供給するための領域が、メモリセル32ローあるいは、64ロー毎に、ワード線と平行に形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みビットライン型不揮発メモリの微細化に適した製造方法を提供し、かつコンタクトの位置ずれに起因するビットライン間ショートを生じ難い構造を提供する。

【解決手段】導電体膜が埋め込まれたシャロートレンチ溝内にビットライン拡散層を設けてSONOS構造セルとする。これにより、ビットライン拡散層の半導体基板主面上での面積を大きくせずにビットライン拡散層の抵抗を低くすることができ、セル面積を増大させることなく安定した電気的特性の半導体記憶装置が得られる。また、Si3N4のサイドウォールを設けてイオン注入することでビットラインを形成する。これにより、メモリセルの微細化が可能となる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】隣接するメモリセルゲート電極間に空隙を形成することで結合容量を抑制し、複数のコンタクト同士の短絡を防止しメモリの信頼性を向上する。

【解決手段】半導体記憶装置は、複数の選択ゲート電極間に形成され、選択ゲート電極に近接した側の側面と当該選択ゲート電極との第2間隔が第1間隔より広い層間絶縁膜11と、複数のメモリセルゲート電極間に空隙AGを備えるよう当該空隙AGの上部を被覆し、複数の選択ゲート電極間においては当該選択ゲート電極の側面および層間絶縁膜11の側面に沿って形成され、その上部に窪部Rを備えて形成されたエアギャップ形成膜12と、複数のメモリセルゲート電極上のエアギャップ形成膜12上に形成され、複数の選択ゲート電極間ではエアギャップ形成膜12の窪部Rの内側に埋込まれたリフィル膜13と、複数の素子領域に接触するように層間絶縁膜11に形成された複数のコンタクトCBa,CBbを備える。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

データ保持装置及びこれを用いた論理演算回路

【課題】マスクパターンの疎密に起因する強誘電体素子の特性ばらつきを適切に低減することが可能なデータ保持装置及び、これを用いた論理演算回路の提供。

【解決手段】データ保持装置において、不揮発性記憶部に含まれる複数の強誘電体素子X(素子幅m)は、各々よりも素子幅の小さいダミー素子Y(素子幅n、ただしn<m)によって包囲されている。これによってマスクパターンの疎密に起因するエッチングのローディング効果を抑制する事が可能となる。

(もっと読む)

半導体装置

【課題】金属酸化物中の酸素欠損を低減し、電気的特性の安定した半導体装置を提供することを目的の一とする。

【解決手段】ゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の金属酸化物膜と、第1の金属酸化物膜に接して設けられたソース電極及びドレイン電極と、ソース電極及びドレイン電極上に設けられたパッシベーション膜と、を有し、パッシベーション膜は、第1の絶縁膜と、第2の金属酸化物膜と、第2の絶縁膜とが順に積層された半導体装置である。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリを提供する。

【解決手段】ビット線と、ソース線と、複数の不揮発性メモリが直列に接続されたNAND型セルと、選択トランジスタと、を有し、不揮発性メモリは、第1の絶縁膜を介した半導体上の電荷蓄積層と、第2の絶縁膜を介した電荷蓄積層上の制御ゲートと、を有し、NAND型セルの一方の端子は、選択トランジスタを介して、ビット線に接続され、NAND型セルの他方の端子は、ソース線に接続されたNAND型不揮発性メモリであって、第1の絶縁膜は、半導体に酸素雰囲気で高密度プラズマ処理を行った後、窒素雰囲気で高密度プラズマ処理を行うことで形成されるNAND型不揮発性メモリ。

(もっと読む)

121 - 140 / 635

[ Back to top ]