Fターム[5F083LA02]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | メモリセルユニット間レイアウト (635)

Fターム[5F083LA02]に分類される特許

41 - 60 / 635

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】制御ゲート電極および浮遊ゲート電極を備えた構成において、制御ゲート電極を構成する多結晶シリコンの空乏化を抑制できるようにした不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された複数の浮遊ゲート電極と、複数の浮遊ゲート電極上に形成された電極間絶縁膜と、電極間絶縁膜上に形成されたワード線と、を備える。ワード線は、不純物がドープされた多結晶シリコンを含む下層および上層を分断し且つ複数の浮遊ゲート電極間に一部が位置する分断層を介在して形成され、ワード線は、その下層の高さが上層の高さよりも低い。

(もっと読む)

メモリ用シフトレジスタ

【課題】大容量なメモリ用シフトレジスタを提供する。

【解決手段】メモリ用シフトレジスタは、基板101と、基板101上に形成され、基板101の主面に垂直な軸Lの周りを回転する螺旋形状を有するチャネル層111とを備える。さらに、メモリ用シフトレジスタは、基板101上に形成され、軸Lに平行な方向に延びており、チャネル層111内の電荷を転送するために使用される3本以上の制御電極1121,1122,1123を備える。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

(もっと読む)

半導体記憶装置

【課題】メモリセルを高抵抗状態及び低抵抗状態に容易に遷移可能な状態とする半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、メモリセルアレイ、及び制御回路を有する。メモリセルアレイにおいては、可変抵抗素子を含むメモリセルが複数の第1配線及び複数の第2配線の交差部に配置される。制御回路は、セットパルス印加動作、及びキュアパルス印加動作を実行する。セットパルス印加動作は、可変抵抗素子を高抵抗状態から低抵抗状態に遷移させるため、可変抵抗素子にセットパルスを印加する。キュアパルス印加動作は、セットパルス印加動作により可変抵抗素子の抵抗値が所定値以下に下がらなければ、可変抵抗素子にキュアパルスを印加する。キュアパルスは、セットパルスの極性と逆の極性を有し、且つセットパルスよりも大きい。

(もっと読む)

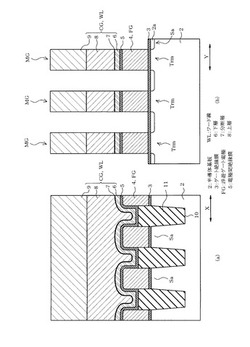

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】不純物添加シリコン層に添加された不純物が不純物無添加シリコン層に拡散するのを抑制する。

【解決手段】セレクトゲート電極SG1上にはワード線WL1が積層され、最上層のワード線WL1上にはセレクトゲート電極SG2がロウごとに形成されることで、NANDセルNC1が構成され、セレクトゲート電極SG1、SG2およびワード線WL1は、不純物添加シリコン層2と層間絶縁膜とを拡散防止層3を介して交互に積層することで構成し、ワード線WL1は、拡散防止層3にて挟まれた不純物添加シリコン層2にて構成する。

(もっと読む)

半導体記憶装置及びデータ読み出し方法

【課題】レイアウト面積の増大を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置1は、2つのメモリセルアレイ10U,10Dと、それら2つのメモリセルアレイ10U,10Dで共有されるセンスアンプ30と、メモリセルアレイ10U,10Dからのデータ読み出しを制御する制御回路50とを有している。メモリセルアレイ10Uは、m本のワード線WL0U〜WLmUと、n本のビット線BL0U〜BL15Uと、これらワード線WL0U〜WLmUとビット線BL0U〜BL15Uの交差点に設けられたメモリセルMCと、ビット線BL0U〜BL15Uとダミーワード線DWLUとの交差点に設けられたダミーセルDMCとを有している。制御回路50は、一方のメモリセルアレイからデータを読み出す場合に、他方のメモリセルアレイのダミーワード線を活性化してダミーセルによりセンスアンプ30のリファレンスレベルを生成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】非選択メモリセルに流れる逆方向電流を低減させた不揮発性半導体記憶装置を提供することを目的とする。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、複数のメモリセルを有するメモリセルアレイと、選択第1配線に選択第1配線電圧を供給し、非選択第1配線に非選択第1配線電圧を供給する第1配線制御回路と、アクセス対象となるメモリセルに接続された第2配線である選択第2配線に選択第2配線電圧を供給し、その他の第2配線である非選択第2配線に非選択第2配線電圧を供給する第2配線制御回路とを備え、メモリセルは、第1ダイオードのアノード側に第2配線が接続され、第1ダイオードのカソード側に第1配線が接続され、メモリセルアレイは、第2配線制御回路及びメモリセル間の第2配線に挿入され、第2配線制御回路側をアノード、メモリセル側をカソードとする第2ダイオードを有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】複数の埋め込みゲート型トランジスタが形成されたメモリセル領域と周辺回路領域を有する半導体装置の製造において、前記埋め込みゲート型トランジスタの半導体層とコンタクトプラグとの接触抵抗及び前記埋め込みゲート型トランジスタ毎の電流駆動特性のばらつきの増加を防ぐ。

【解決手段】半導体基板上に第1の半導体層と、前記第1の半導体層の下面と接する前記第1の半導体層よりも低い不純物濃度である第2の半導体層とを形成する工程と、前記第1の半導体層及び前記第2の半導体層から成る活性領域を少なくとも2つの領域に分ける溝内にゲート絶縁膜を介してゲート電極を形成する工程と、前記半導体基板の主面を覆う層間絶縁膜を形成する工程と、前記層間絶縁膜を貫通して前記第1の半導体層の上面の一部を露出させるコンタクトホールに導電膜を埋め込んでコンタクトプラグを形成する工程を有する半導体装置の製造方法。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】チャネル移動度を向上させた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20上に設けられたメモリトランジスタ40と選択トランジスタ50を有する。メモリトランジスタ40は、導電層41a〜41d、メモリゲート絶縁層43、柱状半導体層44、及び酸化層45を有する。導電層41は、メモリトランジスタ40のゲートとして機能する。メモリゲート絶縁層43は、導電層の側面に接する。半導体層44は、導電層と共にメモリゲート絶縁層43を一方の側面で挟み、半導体基板20に対して垂直方向に延び、メモリトランジスタ40のボディとして機能する。酸化層45は、半導体層44の他方の側面に接する。半導体層44は、シリコンゲルマニウムにて構成される。酸化層45は、酸化シリコンにて構成される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化されても、コントロールゲートとフローティングゲートとの間のカップリング容量比を増大させることができる半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。第1の絶縁膜は、半導体基板上に形成されている。フローティングゲートは、第1の絶縁膜上に設けられた第1のフローティングゲート部分、第1のフローティングゲート部分上に設けられた中間絶縁膜、および、中間絶縁膜上に設けられた第2のフローティングゲート部分を含み、電荷を蓄積可能に構成されている。第2の絶縁膜は、フローティングゲートの上面および側面に設けられている。コントロールゲートは、第2の絶縁膜を介してフローティングゲートの上面および側面に対向し、フローティングゲートの電圧を制御する。フローティングゲートの側面において中間絶縁膜が第1および第2のフローティングゲート部分に対して窪んでいる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】隣接セルの書き込み閾値の変動を抑制すると共に、制御ゲート電極膜とシリコン基板との間のリーク電流を低減して消去特性を向上させる。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板における素子分離絶縁膜により区画された活性領域上にゲート絶縁膜を介して形成された電荷蓄積層と、前記素子分離絶縁膜の上面、前記電荷蓄積層の側面及び前記電荷蓄積層の上面に形成された電極間絶縁膜と、前記電極間絶縁膜上に形成された制御電極層とを備える。前記電極間絶縁膜は、第1のシリコン酸化膜、第1のシリコン窒化膜、第2のシリコン酸化膜および第2のシリコン窒化膜を積層形成した積層構造を有する。そして、前記電極間絶縁膜は、前記第2のシリコン酸化膜のうちの前記素子分離絶縁膜の上面上の部分の膜厚が前記電荷蓄積層の上面上の部分の膜厚より薄くなるように構成した。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高電界リークを低減して、書き込み特性を向上させる。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板における素子分離絶縁膜により区画された活性領域上にゲート絶縁膜を介して形成された電荷蓄積層と、前記素子分離絶縁膜の上面、前記電荷蓄積層の側面及び前記電荷蓄積層の上面に形成された電極間絶縁膜と、前記電極間絶縁膜上に形成された制御電極層とを備える。そして、前記電極間絶縁膜は、シリコン窒化膜もしくは高誘電率膜を2層のシリコン酸化膜で挟んだ積層構造または高誘電率膜とシリコン酸化膜の積層構造及び前記積層構造と前記制御電極層の間に形成された第2のシリコン窒化膜を有し、前記第2のシリコン窒化膜のうちの前記電荷蓄積層の上面上の部分を消失させた。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ガードリング周辺のメモリセル領域から周辺回路領域へのエッチング液の染み込みを防止する。

【解決手段】半導体装置の製造方法は、メモリセル領域及び周辺回路領域が画定された半導体基板上に第1の層間絶縁膜を形成し、第1の層間絶縁膜の一部を除去してメモリセル領域の周囲にガードリング溝を形成し、ガードリング溝を金属導電材で埋めてガードリングとし、ガードリングを覆うように第1の層間絶縁膜上にサポート膜を形成し、メモリセル領域のサポート膜に開口を形成し、開口を通してウエットエッチングを行うことで、周辺回路領域の第1の層間絶縁膜を残したまま、メモリセル領域の第1の層間絶縁膜を除去する。

(もっと読む)

半導体記憶装置

【課題】4個のトランジスタと2個のMTJ素子からなり、電源を印加しないでも不揮発性メモリとして動作するSRAMからなる半導体記憶装置を提供する。

【解決手段】第1及び第2のインバータ2,4と第1及び第2の転送用MOSFET3,5とを含むメモリセル1からなるSRAMにおいて、第1及び第2のインバータ2,4はスピン注入型のMTJ素子6,8と駆動用MOSFET7,9とからなり、これらのインバータ2,4からフリップフロップ回路が構成され、第1及び第2のインバータ2,4の出力端子は、それぞれ第1及び第2の転送用MOSFET3,5を介してビットライン及びビットラインバーに接続され、第1及び第2の転送用MOSFET3,5のゲートは、同一のワードラインに接続される。従来のSRAMに比較してメモリセルの面積が小さく、高速で低消費電力の不揮発性メモリが得られる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルアレイと周辺回路との間のアレイ端パターンにおける耐圧を向上させる。

【解決手段】浮遊ゲートは半導体基板上の第1の絶縁膜上に設けられる。ゲート間絶縁膜は浮遊ゲート上に、制御ゲートはゲート間絶縁膜上に設けられる。メモリセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含む。周辺回路はメモリセルアレイの周辺に設けられる。第1のダミーセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含み、メモリセルアレイの端に設けられる。第2のダミーセルは、第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられる。第1のダミーセルにおいて、ゲート間絶縁膜および制御ゲートは浮遊ゲートの上面および2つの側面に設けられる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】読み出し速度の向上を図ることができる半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、交互に積層して設けられた複数の電極膜及び層間絶縁膜を有した積層体と、前記積層体を積層方向に貫く半導体ピラーと、前記半導体ピラーと前記電極膜との間に設けられた電荷蓄積膜と、前記半導体ピラーの側面に設けられた添加部と、を備えている。そして、前記半導体ピラーは、ゲルマニウムを含む半導体材料を用いて形成され、前記添加部は、酸化アルミニウムを用いて形成されている。

(もっと読む)

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離絶縁膜の形成時に、浮遊ゲート電極膜の基板に対面する部分の幅寸法が細くなってしまうことを防止する。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成され、浮遊ゲート電極膜、電極間絶縁膜および制御ゲート電極膜が積層されたゲート電極とを備えた。そして、前記浮遊ゲート電極膜を、窒素を含む下層シリコン層と窒素を実質的に含まない上層シリコン層とを有する多結晶シリコン層で構成し、前記下層シリコン層のゲート幅方向の寸法を、前記上層シリコン層のゲート幅方向の寸法よりも大きく構成した。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体記憶装置の製造方法

【課題】スループットの向上を図る。

【解決手段】半導体記憶装置の製造方法は、基板上に、不純物濃度が第1濃度である第1シリコン層35、不純物濃度が第1濃度より低い第2濃度である第1犠牲層、不純物濃度が第1濃度である第2シリコン層35、および不純物濃度が第2濃度である第2犠牲層が順に積層された積層体を形成する工程と、積層体上に、第1絶縁膜を形成する工程と、積層体および第1絶縁膜内に、溝22を形成する工程と、溝内に、不純物濃度が第1濃度より低く、第2濃度より高い第3濃度である第3犠牲層90を埋め込む工程と、ウェットエッチングにより、溝内の第3犠牲層を上面から後退させて除去することで、第1犠牲層および第2犠牲層の端面を後退させる工程と、第1シリコン層および第2シリコン層の端面を第1犠牲層および第2犠牲層の端面に沿ってエッチングする工程とを具備する。

(もっと読む)

41 - 60 / 635

[ Back to top ]