Fターム[5F083LA03]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | センスアンプ (769)

Fターム[5F083LA03]に分類される特許

161 - 180 / 769

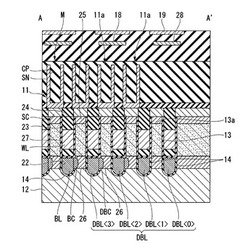

半導体装置

【課題】リーク電流が発生しにくく、低消費電力化に好適な半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体基板12内に埋め込まれてX方向に並列して延在する複数のビット線BLと、X方向と交差するY方向に延在するワード線と、ビット線BLと前記第2配線との交点に設けられたメモリセルMと、複数のビット線BLのうち最外列のビット線BLの外側に設けられ、X方向に延在してビット線BLと並走するダミービット線DBLとを含み、ダミービット線DBLが、半導体基板12に供給される電位と同じ電位が供給されるダミービット線(第1ダミー配線)DBL<0>、DBL<1>、DBL<2>を含むことを特徴とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、メモリセルアレイを有する半導体装置において、直列に接続された第1乃至第mのメモリセルに含まれる各ノードに生じる寄生容量の値を同等の値とすることで、安定して動作可能な半導体装置とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ソース線と、ビット線と、信号線と、ワード線と、ソース線とビット線との間に、並列に接続されたメモリセル1100と、ソース線及びビット線とスイッチング素子を介して電気的に接続された第1の駆動回路1111と、ソース線とスイッチング素子を介して電気的に接続された第2の駆動回路1112と、信号線と電気的に接続された第3の駆動回路1113と、ワード線と電気的に接続された第4の駆動回路1114と、を有し、メモリセルは、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、容量素子と、を有し、第2のトランジスタは、酸化物半導体材料を含む。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタと第2のトランジスタを有し、第1のトランジスタと第2のトランジスタとは少なくとも一部が重畳する第1のメモリセルと、第3のトランジスタと第4のトランジスタを有し、第3のトランジスタと第4のトランジスタとは少なくとも一部が重畳する第2のメモリセルと、駆動回路と、を有し、第2のメモリセルは、第1のメモリセル上に設けられ、第1のトランジスタは、第1の半導体材料を含んで構成され、第2のトランジスタ、第3のトランジスタ、および第4のトランジスタ、は、第2の半導体材料を含んで構成される半導体装置である。

(もっと読む)

チャージポンプ回路、不揮発性メモリ、データ処理装置、及びマイクロコンピュータ応用システム

【課題】複数の容量を互いに直列接続して一つの昇圧容量を形成した場合の中間ノードの帯電に起因するデバイス破壊を回避するとともに、当該中間ノードのリークパスを介して流れるリーク電流に起因するポンプ効率の低下を回避する。

【解決手段】チャージポンプ回路(1307)は、第1静電容量(Ca)とそれに直列接続された第2静電容量(Cb)とを含む昇圧容量(C(x−1),Cx)と、容量ドライバ(DRV(x−1),DRVx)と、保護回路(D1,D2)とを含む。上記保護回路は、上記昇圧電圧が形成されない状態においては導通状態とされて、上記第1静電容量と上記第2静電容量との直列接続ノードの蓄積電荷を放電し、上記昇圧電圧が形成される状態においては非導通状態を維持する。これにより、昇圧容量の耐圧緩和を図り、また、ポンプ効率の低下を回避する。

(もっと読む)

不揮発性記憶装置

【課題】電源投入後、高速なセットアップが可能な不揮発性記憶装置を提供する。

【解決手段】不揮発性記憶装置は、データを不揮発的に記憶するメモリセルを有する第1および第2のメモリモジュール16−1、16−2と、第1および第2のメモリモジュールとそれぞれ接続されて、前記第1および第2のメモリモジュールを駆動するための外部電源を供給する第1および第2の外部電源線VL11、VL12とを備え、第1の外部電源線の電源容量C1は、前記第2の外部電源線の電源容量C2よりも小さい。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】安定した動作を実行可能な不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、複数のメモリストリング、選択トランジスタ、及びキャリア選択素子を備える。メモリストリングは、直列接続されたメモリトランジスタを含む。選択トランジスタは、メモリストリングの一端に一端を接続されている。キャリア選択素子は、選択トランジスタの他端に一端を接続されている。キャリア選択素子は、メモリトランジスタのボディを流れる多数キャリアを決定する。キャリア選択素子は、第3半導体層、金属層、第2ゲート絶縁層、及び第3導電層を備える。第3半導体層は、基板に対して垂直方向に延びる。金属層は、第3半導体層の上面から延びる。第3導電層は、第2ゲート絶縁層を介して、第3半導体層及び金属層を取り囲む。

(もっと読む)

抵抗変化型半導体メモリ

【課題】セル面積の縮小及び動作特性の向上に優れたレイアウトを提案する。

【解決手段】実施形態によれば、抵抗変化型半導体メモリは、第1方向に並ぶ第1乃至第4メモリセルを備える。第1乃至第4メモリセルの各々は、第1ソース/ドレインが第1方向に延びる第1ビット線BLA1に接続され、ゲートが第2方向に延びるワード線WL1, WL2, WL3, WL4に接続されるセルトランジスタT11, T12, T13, T14と、一端がセルトランジスタT11, T12, T13, T14の第2ソース/ドレインに接続され、他端が第2方向に延びる第2ビット線BLB1, BLB2, BLB3, BLB4に接続される抵抗性記憶素子M11, M12, M13, M14とを有する。第1及び第2メモリセル内の第1ソース/ドレインは、共有化され、第3及び第4メモリセル内の第1ソース/ドレインは、共有化される。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、ゲート絶縁層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置

【課題】相変化材料を用いたメモリセルを含む半導体装置において、書込み速度を律速しているセット動作を高速化することができる技術を提供する。

【解決手段】相変化材料に印加するセットパルス電圧を2段とし、相変化材料の温度を1段目の電圧で核生成の最も早くなる温度とし、2段目のパルスでは結晶成長の最も早くなる温度とし、相変化材料を溶かさずに固相成長させる手段を用いる。また、相変化材料に印加される2段パルス電圧は、ドレイン電流ばらつきが低減できるワード線に印加される2段の電圧により制御する手段を用いる。

(もっと読む)

相変化メモリコーディング

【課題】取り付け工程に係る半田付け及び高温環境での熱事象を通じても、データを保持することができる相変化メモリデバイスの提供。

【解決手段】一部のセルとメモリに第一抵抗状態、及び他部のセルとメモリに第二抵抗状態を誘導することにより、データセットを表わすために、プレコーディング(pre−coded)することができる。前記データセットがコーディングされ、基板に取り付けられた後に、前記第一及び前記第二抵抗状態を感知することにより、前記データセットを読み取り、前記第一抵抗状態を第三抵抗状態に変化させ、前記第二抵抗状態を第四抵抗状態に変化させる。半田接合と他の熱サイクルプロセスの後、前記第一及び前記第二抵抗状態は、感知マージン(sensing margin)を維持する。より高速とより低い電力を使用すると、前記第三及び前記第四抵抗状態は、転移(transition)を引き起こす能力がある。

(もっと読む)

半導体記憶装置及びその回路の電位測定方法

【課題】大規模な半導体記憶装置における不良トランジスタの検出と、不良トランジスタの特性の測定とを高速で行うことができる、半導体記憶装置を提供する。

【解決手段】メモリ素子が縦横にマトリックス状に配列されたメモリセルアレイと、接地ノードあるいは電源ノードに接続する枝配線を有する半導体記憶装置において、電源ノードあるいは接地ノードに接続する少なくとも1つの枝配線の複数箇所に電圧測定点を接続したモニター用スイッチを有し、クロック信号に同期して前記モニター用スイッチのゲートを順に開くスイッチ選択信号発生回路を有し、前記スイッチ選択信号発生回路で選択されてゲートが開かれたモニター用スイッチを介して前記電圧測定点の電位を測定する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の長時間にわたる保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと、第2のトランジスタと、を含む複数のメモリセルと、増幅回路と、スイッチ素子と、を含む読み出し回路と、リフレッシュ制御回路と、を有し、第1のチャネル形成領域と第2のチャネル形成領域は、異なる材料を主成分として構成され、第1のゲート電極と、第2のソース電極および第2のドレイン電極の一方は電気的に接続され、第2のソース電極および第2のドレイン電極の他方と、増幅回路の入力端子の一は電気的に接続され、増幅回路の出力端子は、スイッチ素子を介して第2のソース電極および第2のドレイン電極の他方と接続され、スイッチ素子の導通状態または非導通状態は、リフレッシュ制御回路によって制御される半導体装置である。

(もっと読む)

半導体記憶装置の製造方法及び半導体記憶装置

【課題】メモリセルアレイの保持内容に起因するリーク電流による誤読み出しを抑制可能な半導体記憶装置を製造する。

【解決手段】接地電位制御要否判定部3が、設計対象のメモリセルアレイの保持内容から、メモリセルのトランジスタの接地電位の制御の要否を判定し、接地電位の制御が必要と判定された場合、接地電位制御回路生成部4が、読み出し動作時に非選択となるトランジスタの接地電位を引き上げる接地電位制御回路を生成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】動作速度を向上させる。

【解決手段】不揮発性半導体記憶装置は、複数の第1の配線、第1の配線に交差する複数の第2の配線、並びに第1及び第2の配線の各交差部に配置された電気的書き換え可能な抵抗値をデータとして不揮発に記憶する可変抵抗素子からなる複数のメモリセルを有するメモリセルアレイを有する。電圧印加手段は、メモリセルに対するデータの書き込み又はフォーミング時に、第1の配線及び第2の配線を介してメモリセルに所定の電圧を印加する。検出手段は、メモリセルに対する所定の電圧の印加時にメモリセルの抵抗状態の変化を検出して検出情報を出力する。出力手段は、検出手段から出力された検出情報の少なくとも一部を外部に出力する。

(もっと読む)

プロセス評価用半導体集積回路

【課題】 微妙なプロセスコントロールのための判断材料となる情報を短時間のうちに採取することができるプロセス評価用半導体集積回路を提供する。

【解決手段】 プロセス評価用半導体集積回路としてのSRAMは、メモリセルに電源電圧を供給する給電系統と、メモリセル以外の回路に電源電圧を供給する給電系統とが分離されており、メモリセルに供給する電源電圧を他の回路に対する電源電圧と独立に制御可能な構成となっている。メモリセルに対する電源電圧を段階的に下げつつ、各メモリセルに対するアクセスを試み、動作不良を検出することにより、メモリセル間のトランジスタの電気的特性の微妙な変化を判定することができる。

(もっと読む)

不揮発性記憶装置及びその駆動方法

【課題】動作の制御性を向上した不揮発性記憶装置及びその駆動方法を提供する。

【解決手段】実施形態によれば、メモリ部MUと、制御部CUと、を備えた不揮発性記憶装置が提供される。メモリ部は、第1配線WR1と、第2配線WR2と、第1配線と第2配線との交差部に設けられ、第1配線と第2配線とを介して印加される電圧及び通電される電流の少なくともいずれかによって抵抗が変化する抵抗変化層VRを含むメモリセルMCと、を有する。制御部は、第1配線と第2配線とに接続され、抵抗変化層に電圧及び電流の少なくともいずれかを供給する。制御部は、抵抗変化層を、第1抵抗値を有する第1状態から、第1抵抗値よりも低い第2抵抗値を有する第2状態に変化させるセット動作において、第1配線にセット動作電圧を印加する際に、第1配線の電位の変化に基づいて第1配線に供給される電流の上限値を増やす。

(もっと読む)

半導体装置

【課題】集積度の高い相変化メモリを実現する。

【解決手段】本発明による半導体装置は、複数のワード線と、複数のワード線と直交する複数のビット線との交点に配置された複数のメモリセル群を有する。複数のメモリセル群は、直列接続された第一乃至第二のメモリセルを有する。第一乃至第二のメモリセルの各々は、並列接続される選択トランジスタと抵抗性記憶素子とを有する。第一のメモリセルにおける選択トランジスタのゲート電極は、第一のゲート線に接続され、第二のメモリセルにおける選択トランジスタのゲート電極は、第二のゲート線に接続される。そして、複数のワード線を駆動する第一の回路ブロック(ワードドライバ群WDBK)は、第一乃至第二のゲート線を駆動する第二の回路ブロック(相変化型チェインセル制御回路PCCCTL)と、複数のメモリセル群(メモリセルアレーMA)との間に配置される。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面に第1の絶縁膜を形成し、第1の絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて第1の絶縁膜にエッチング処理を行うことにより、第2の絶縁膜を形成し、第2の絶縁膜を覆うように第1の導電膜を形成し、第1の導電膜および第2の絶縁膜に研磨処理を行うことにより、等しい厚さの第3の絶縁膜、ソース電極およびドレイン電極を形成し、第3の絶縁膜、ソース電極およびドレイン電極上に酸化物半導体膜を形成し、酸化物半導体膜上にゲート絶縁膜を形成し、ゲート絶縁膜上の第3の絶縁膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

161 - 180 / 769

[ Back to top ]