Fターム[5F083LA03]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | センスアンプ (769)

Fターム[5F083LA03]に分類される特許

141 - 160 / 769

半導体メモリ

【課題】ビット線間の寄生容量による影響を低減することにより、高精度のデータの読出しを可能にする半導体メモリを提供する。

【解決手段】1つの主ビット線に互いに異なるタイミングでオン駆動するセレクタ素子及び当該セレクタ素子のそれぞれに接続された副ビット線を介して当該副ビット線のそれぞれにメモリセルが接続され、当該主ビット線に並置されるとともに固定電位に接続された固定電位線が設けられていること。

(もっと読む)

半導体装置

【課題】半導体装置の省スペース化を実現する。

【解決手段】半導体基板5に、センスアンプが備えられた周辺回路領域Sとメモリセル領域Mとが区画形成され、メモリセル領域Mにおいて、半導体基板5の一面に形成されたトレンチ溝内に、ゲート絶縁膜を介しゲート電極を含む埋込ワード線9とその上に位置する埋込絶縁膜とが埋め込まれ、前記トレンチ溝に隣接する半導体基板5一面の表面領域に不純物拡散層が形成され、前記不純物拡散層が形成された領域上にはビット配線15が形成されており、ビット配線15が周辺回路領域Sまで延長され、周辺回路領域Sにおいてビット配線15が前記センスアンプを構成するMOSトランジスタのゲート電極Gとされていることを特徴とする半導体装置を採用する。

(もっと読む)

強誘電体メモリおよびその制御方法

【課題】セルデータ読み出しのシグナルマージンを向上させることができる強誘電体メモリおよびその制御方法を実現する。

【解決手段】本発明の実施形態における強誘電体メモリは、セルキャパシタとセルトランジスタとが並列接続された複数のメモリセルと、隣り合う2つのメモリセルにおいてセルキャパシタの下部電極同士または上部電極同士が接続されるよう複数のメモリセルが直列に接続されて、その一端がビット線(/BL、BL)に接続され、他端がプレート線(/PL0、PL0)に接続されたセルブロック(MB0、MB1)と、下部電極がプレート線(/PL0、PL0)に電気的に接続される場合と、上部電極がプレート線(/PL0、PL0)に電気的に接続される場合とでセルキャパシタの電極間にかかる電界が同じ方向に印加されるようにプレート線(/PL0、PL0)およびビット線(/BL、BL)を制御する制御回路11および12を有する。

(もっと読む)

不揮発性メモリー装置の製造方法

【課題】不揮発性メモリー装置の製造方法であって、特に半導体パターン厚さの均一性が向上される3次元半導体装置の製造方法、及び当該製造方法によって製造された3次元半導体装置を提供する。

【解決手段】この製造方法は、基板10の上に複数の第1の膜(鋳型膜)120及び複数の第2の膜(犠牲膜)が交互に積層された積層膜構造体を形成する段階、積層膜構造体を貫通する開口部、及び開口部周囲にアンダーカット領域を形成する段階、アンダーカット領域に局所的に配置される絶縁スペーサー155を形成する段階、絶縁スペーサー155が形成された開口部内に半導体パターン165を形成する段階を含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】本実施形態は、データ書き込みの高速化をはかり得る不揮発性半導体記憶装置を提供する。

【解決手段】実施形態の不揮発性半導体記憶装置によれば、半導体基板上に積層された複数のワード線に、電荷蓄積層を有する複数のメモリセルがそれぞれ接続され、且つ、隣接するメモリセル間で電荷蓄積層が連続しているセル構造のメモリセルアレイと、前記メモリセルアレイのn番目(nは自然数)のワード線に接続されたメモリセル群にデータを書き込む際に、(n−1)番目及び(n+1)番目のワード線に接続されたメモリセル群に同一の書き込み電圧を同時に印加するよう制御する制御回路と、を具備したことを特徴とする。

(もっと読む)

不揮発性半導体記憶装置

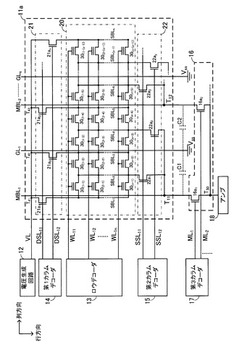

【課題】電源線等への電圧供給源であるポンプの面積を削減でき、電源線等に電圧を転送するスイッチ回路のストレスを緩和できる不揮発性半導体記憶装置を提供する。

【解決手段】第1領域と第2領域との間に配置されたセルアレイ11と、第1領域に配置された第1,第2ローデコーダ12−0と、第1領域に配置され、第1ローデコーダに電圧を伝送する第1電源線VRDEC_T<0>、第2ローデコーダに電圧を伝送する第2電源線VRDEC_B<0>と、第1,第2電源線に電圧を供給するロー系周辺回路17と、第1電源線と回路17との間を接続または遮断状態に切り換える第1スイッチ回路SWV_T<0>と、第2電源線と回路17との間を接続または遮断状態に切り換える第2スイッチ回路SWV_B<0>とを備える。書き込み動作時に、第1スイッチ回路は第1電源線と回路17との間を接続状態にし、第2スイッチ回路は第2電源線と回路17との間を遮断状態にする。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み可能回数が多く、信頼性の高い不揮発性半導体記憶装置を提供する。

【解決手段】複数の第1の配線、複数の第1の配線に交差する複数の第2の配線、並びに複数の第1及び第2の配線の各交差部に配置された電気的書き換え可能な抵抗値をデータとして不揮発に記憶する可変抵抗素子を含む複数のメモリセル、を有するメモリセルアレイと、複数の第1の配線の少なくとも一端に接続され、第1の配線を選択する第1のデコーダと、複数の第2の配線の両端に接続されて第1のデコーダが選択した第1の配線と第2の配線の両端との距離に応じていずれか一方が第2の配線を選択する少なくとも一対の第2のデコーダと、第1のデコーダ及び第2のデコーダによって選択された第1の配線及び第2の配線間に所定の電圧を印加する電圧印加回路とを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルに与えられる影響を緩和し、正確にデータを書き込むことのできる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリセルアレイと制御部とを備える。制御部は、選択メモリセルに書き込みパルス電圧を印加するとともに、非選択メモリセルに中間電圧を印加する書き込み動作、書き込みベリファイ動作、及び書き込みパルス電圧を上昇させるステップアップ動作を繰り返す制御を司る。制御部は、第1期間では、中間電圧を一定の値に保ち、第2期間では、中間電圧を所定のステップアップ値だけ上昇させるようにステップアップ動作を制御する。制御部は、第1期間では、書き込みパルス電圧を第1のステップアップ値で上昇させる動作を含み、第2期間では、書き込みパルス電圧を第1のステップアップ値より小さい第2のステップアップ値で上昇させる動作を含むようにステップアップ動作を制御する。

(もっと読む)

半導体記憶装置

【課題】消去回数の増加を抑制し、書き込み速度の向上及びメモリセルの劣化を防止することが可能な半導体記憶装置を提供すること。

【解決手段】読み出しレベルに応じてデータを保持可能なセルMCが形成されたセルアレイ1と、前記セルMCに書き込まれた回数N(N:0以上の整数)をカウントし、その回数に応じて書込電圧Vpgm及び読出電圧Vcgrを前記セルに転送する制御部9と、前記書込電圧を用いてデータを書み込み、前記読出電圧を発生し、データを読み出す電圧発生回路とを具備し、書込要求があると、前記読出電圧を発生させ、前記データを読み出し、読み出された閾値電圧より高い閾値電圧に遷移させる前記書き込み電圧を前記電圧発生回路に発生させ、前記セルへの前記回数N回目(≧2)の書き込み要求が規定値に達していると、前記制御部は前記セルが保持する前記データを消去させる。

(もっと読む)

不揮発性半導体記憶装置およびその制御方法

【課題】高速で高信頼動作できるようにした不揮発性半導体記憶装置およびその制御方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセル、および、前記第1のメモリセルに対し第1方向に隣接して配置された第2のメモリセルを備えたセル群と、書込回路とを備え、第1および第2のメモリセルの一方をデータ記憶保持に、他方を一方の閾値調整に用い、書込回路が、セル群の前記第1のメモリセルにデータを書込むときには、セル群の第2のメモリセルに電圧を印加し、セル群の第1のメモリセルの閾値電圧を所望の第1閾値電圧より高く調整する。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択的に消去動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】制御回路は、選択メモリブロック内の選択セルユニットに対して第1メモリトランジスタに蓄積された電荷を放出する消去動作を実行する一方、選択メモリブロック内の非選択セルユニットに対して消去動作を禁止するように構成されている。制御回路は、消去動作時、選択セルユニットに含まれる第1メモリトランジスタのボディの電圧を第1電圧まで上げ、非選択セルユニットに含まれる第1メモリトランジスタのボディの電圧を第1電圧よりも低い第2電圧に設定すると共に、選択セルユニット及び非選択セルユニットに含まれる第1メモリトランジスタのゲートに第2電圧以下の第3電圧を印加する。

(もっと読む)

半導体集積回路装置

【課題】相変化メモリの信頼性を向上させる。

【解決手段】例えば、ワード線WL0とビット線BL0の交点に設けられたメモリセル内の相変化素子に対して、この相変化素子をreset動作によってアモルファス状態にする場合、ビット線BL0の立ち上がり時間trb/立ち下がり時間tfbを、ワード線WL0の立ち上がり時間trw/立ち下がり時間tfwより長くなるように構成する。この際に、reset動作で必要な相変化素子の急冷は、ワード線WL0の立ち下がり時間tfwを用いて行う。このような構成および動作を用いることで、ビット線BL0とワード線WL1の交点に設けられた非選択メモリセル内の相変化素子に対するディスターブ電流IBL01が低減する。

(もっと読む)

半導体記憶装置

【課題】低電源電圧下においても、安定かつ高速に動作する半導体記憶装置を実現する。

【解決手段】メモリセル列ごとにアレイ電源線(ARVD)およびダウン電源線(DWVD)を配置する。ダウン電源線は、読出し時に接地に結合され、書込み時にフローティング状態とされる。書込み時、選択列のアレイ電源線への電源電圧の供給を停止するとともに該アレイ電源線を対応のダウン電源線に接続する。電源系統を複雑化することなく、低電源電圧下においても安定にデータの書込/読出を行うことのできる半導体記憶装置を実現することができる。

(もっと読む)

半導体記憶装置

【課題】微細化を図りつつ、書き込みおよび読み出し不良を抑制する。

【解決手段】メモリセルストリングで構成されるセルアレイとセルアレイの下部に配置される複数の電圧発生回路と電圧発生回路を制御する制御回路とを具備し、複数のメモリセルストリングは、一対の柱状部および一対の柱状部の下端を連結させるように形成された連結部を有する半導体層と柱状部と直交した複数のコントロールゲートと柱状部と複数のコントロールゲートとの各交差部に形成された複数のメモリセルトランジスタとを含み、制御回路は、書き込みおよび読み出し動作時に、複数の電圧発生回路のうち、複数のメモリセルストリングのうちの書き込みおよび読み出し対象のメモリストリングにノイズを与える電圧発生回路を駆動させず、複数のメモリセルストリングのうちの書き込みおよび読み出し対象のメモリストリングにノイズを与えない電圧発生回路を駆動させる。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼できる非常に小型の記憶素子を含む、3次元集積回路メモリ用の構造を低い製造コストで提供すること。

【解決手段】3次元メモリデバイスは、絶縁材料によって分離され、復号化回路を介してセンスアンプに結合可能なストリングとして配置された複数の隆起した形状スタック含む。ダイオードは、ストリングのストリング選択端部又は共通ソース選択端部のどちらか一方においてビット線構造に接続される。導電材料の帯片は、隆起した形状のスタックのサイドに側面を有する。ワード線として配列された複数の導電線は、行デコーダに結合することができ、複数の隆起した形状のスタックの上で直交して延びる。記憶素子は、スタック上の電導性帯片の側面と導電線との間の交点における界面領域の多層アレイに設けられる。

(もっと読む)

複合メモリ

【課題】 製造コストの上昇を招くことなくNANDフラッシュメモリにDRAMを混載することができ、且つチップ面積の増大を招くことなくシステム性能の向上をはかる。

【解決手段】 半導体基板10上に、NANDセルユニットからなる第1のメモリセルアレイとDRAMセルからなる第2のメモリセルアレイとを搭載した複合メモリであって、NANDセルユニットは、第1のゲート14と第2のゲート16を積層した2層ゲート構成の不揮発性メモリセル100と不揮発性メモリセル100の第1及び第2のゲート14,16間を接続した選択トランジスタ200で構成され、DRAMセルは、選択トランジスタ200と同じ構成のセルトランジスタ300と、不揮発性メモリセル100又は選択トランジスタ200と同じ構成のMOSキャパシタ400で構成されている。

(もっと読む)

半導体装置のレイアウト方法及びその半導体装置

【課題】トランジスタのしきい電圧の変化を減らすことにより、半導体装置の信頼性を向上させることができる半導体装置のレイアウト方法及びその半導体装置を提供する。

【解決手段】半導体基板内に形成された少なくとも1つの第1電極と第2電極を有する複数個のトランジスタのアクチブ領域を配置する段階と、前記複数個のトランジスタのアクチブ領域のそれぞれの少なくとも1つの第1電極と第2電極との間に位置し、前記半導体基板上に所定の幅と長さを有する1つ以上の実質的に同一間隔に分離された前記複数個のトランジスタのゲートを配置する段階と、前記複数個のトランジスタの間に、所定の幅と長さを有し、前記半導体基板上に前記複数個のトランジスタの分離されたゲートの間隔と実質的に同一間隔に配置された複数個のダミーゲートを配置する段階とを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】メモリセル間の短絡を防止した上で、活性領域上にシリコン膜が十分に形成された半導体装置を提供する。

【解決手段】半導体基板2の表層に埋め込み形成された素子分離膜8によって、活性領域7が区画された半導体装置1であって、前記活性領域7の側面17が露出するように、前記素子分離膜8の上面の一部が除去されて設けられた凹部と、前記凹部を埋め込みつつ、前記活性領域7の上面7d及び前記側面17と接するように設けられたシリコン膜10と、を有することを特徴とする。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】専有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、該記憶ゲートを絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1及び第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された読み出し信号線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

141 - 160 / 769

[ Back to top ]