Fターム[5F083MA03]の内容

半導体メモリ (164,393) | コンタクト (12,929) | コンタクトの形状 (5,658) | セルフアラインコンタクト (383) | ゲート側壁絶縁膜を利用 (268)

Fターム[5F083MA03]に分類される特許

1 - 20 / 268

半導体装置

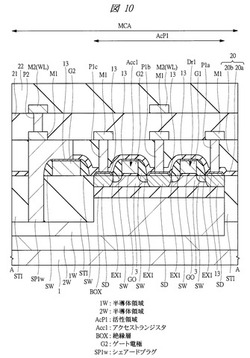

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

【解決手段】SRAMを構成するアクセストランジスタAcc1が配置される活性領域AcP1の下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wの底部および側部が、n型の半導体領域2Wと接するように配置し、p型の半導体領域1Wをn型の半導体領域2Wでpn分離し、アクセストランジスタAcc1のゲート電極G2とp型の半導体領域1Wを接続する。そして、この接続は、アクセストランジスタAcc1のゲート電極G2の上部からp型の半導体領域1Wの上部まで延在する一体の導電性膜であるシェアードプラグSP1wによりなされる。これにより、アクセストランジスタAcc1がオン状態の場合において、バックゲートであるp型の半導体領域1Wの電位が同時に高くなり、トランジスタのオン電流を大きくできる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置の製造方法

【課題】第1の領域において、第2の絶縁膜からゲート絶縁膜への酸化剤の侵入を防止する。第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去する。

【解決手段】半導体装置の製造方法では、基板の第1の領域には第1の積層体を形成し第2の領域には複数の第1の配線を形成する。第1の絶縁膜をマスクとして、第1の領域の主面に第1の不純物のイオン注入を施す。第1の積層体の側壁を覆いかつ複数の第1の配線間を埋設するように第2の絶縁膜を形成する。第2の絶縁膜をマスクとして、第1の領域の主面に第2の不純物のイオン注入を施す。第1のエッチングにより、第2の絶縁膜を第1の絶縁膜に対して選択的に除去した後、基板に熱処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】記憶素子の実効面積の減少を抑制する半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法は、基板上に第1導電プラグを形成する工程と、基板上に第1導電プラグの上面を覆う可変抵抗膜を形成する工程と、基板上に第1導電プラグの上面を覆う第1絶縁膜を形成する工程と、第1絶縁膜のうち第1導電プラグ上の部分を除去して、第1絶縁膜に孔部を形成する工程と、第1絶縁膜の上面から孔部内にわたって第1導電膜を形成して孔部内を埋め込むことで、孔部内で可変抵抗膜に接触し、かつ、可変抵抗膜を介して第1導電プラグに電気的に接続するように第1導電膜を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ上の絶縁膜とキャパシタの形成されていない領域上の絶縁膜と平坦化する際に、キャパシタ上の絶縁膜を一部エッチング除去した後平坦化すると、両者の境界部に残る絶縁膜隆起部が剥がれてくぼみ等の欠陥が発生する。

【解決手段】境界部に残す絶縁膜の隆起部立ち上がり点から水平方向の距離をLr、エッチング量をHdとしたとき、アスペクト比Hd/Lrを0.6以下、好ましくは0.25以下とする。通常、Hdはキャパシタの形成されていない領域上の絶縁膜表面高さまでとし、Lrはキャパシタ高さの少なくとも4倍とする。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

導電性側壁スペーサを有する不揮発性メモリ装置及びその製造方法

【課題】従来の窒化膜側壁を電荷トラップ媒体に利用する場合の信頼性劣化を改善した不揮発性メモリ装置を提供する。

【解決手段】半導体基板21上のゲート絶縁膜22Aと、該ゲート絶縁膜上に順に積層して形成された第1電極膜23、第2電極膜24、及びハードマスク膜25を有するゲート100と、該ゲートの第1電極膜23及び第2電極膜24の両側壁に形成された一対の再酸化側壁スペーサ27と、該再酸化側壁スペーサ及びゲート100のハードマスク膜25の両側壁上に形成された一対の側壁スペーサ28Aと、一対の側壁スペーサ28A上に形成された、電荷を捕獲及び放出する一対の導電性側壁スペーサ29Bと、半導体基板21内に形成された一対のLDD領域26と、半導体基板21内に形成されたソース/ドレイン領域30とを備え、導電性側壁スペーサ29Bが、ゲート100及び側壁スペーサ28Aよりも低い高さを有する。

(もっと読む)

半導体装置

【課題】半導体層上での占有面積の増加を抑制しながらキャパシタ素子の容量を増大させることができる半導体装置を提供する。

【解決手段】この半導体装置は、素子分離溝2によって分離された複数の活性領域Aを有するn型半導体層3と、素子分離溝2の側壁2bを覆う側壁被覆部17を有する容量膜15と、容量膜15に積層された電極膜18とを含む。n型半導体層3、容量膜15および電極膜18によってキャパシタCが形成されている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、犠牲絶縁膜に形成された孔に導電膜を形成し、その後、犠牲絶縁膜を除去後に、導電膜への炭素成分に起因する残渣の付着を抑制することで、半導体装置の歩留まりを向上可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】炭素成分を含まない原料を用いた成膜方法により、半導体基板の表面に犠牲絶縁膜を形成する工程と、犠牲絶縁膜を貫通する孔を形成する工程と、犠牲絶縁膜のうち、前記孔の側壁部分を覆う導体膜を形成する工程と、犠牲絶縁膜を除去する工程と、を有する。

(もっと読む)

半導体装置

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

【解決手段】SRAMを構成するドライバトランジスタ(Dr1)が配置される活性領域(Ac)の下部に、絶縁層(BOX)を介して、素子分離領域(STI)により囲まれたn型のバックゲート領域(nBG)を設け、ドライバトランジスタ(Dr1)のゲート電極(G)と接続する。また、n型のバックゲート領域(nBG)の下部に配置され、少なくともその一部が、素子分離領域(STI)より深い位置に延在するp型ウエル領域(Pwell)を設け、接地電位(VSS)に固定する。かかる構成によれば、トランジスタの閾値電位(Vth)をトランジスタがオン状態の時には高く、逆に、オフ状態の時には低くなるように制御し、また、p型ウエル領域(Pwell)とn型のバックゲート領域(nBG)との間のPN接合も順バイアスさせないよう制御することができる。

(もっと読む)

半導体装置の製造方法

【課題】金属酸化膜の表面に形成される導電膜の基板面内における厚さばらつきを低減して、半導体装置の歩留まりを向上させることが可能であり、かつ導電膜の成長速度を向上させて、半導体装置の生産性を向上させることの可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に、金属酸化膜を含む誘電体膜5を形成する工程と、誘電体膜5において、表面5aに非晶質の金属酸化膜が露出した状態で、誘電体膜5の表面5aに導電膜6を形成する工程と、を含む。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域における上記プラグと、活性領域の外部における上記プラグとの双方を有する、微細化された半導体装置において、枠付け絶縁膜を確実に形成し、かつ導電性などの機能を最適化することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に形成される活性領域と、平面視における活性領域の周辺に形成されるゲート接続領域と、活性領域上に形成される複数の第1のトランジスタTGに挟まれる領域に形成される、第1のトランジスタTGと第1のトランジスタTGよりも上側の層とを電気的に接続するための第1の接続層CTと、ゲート接続領域上に形成される第2のトランジスタTGと、第2のトランジスタTGよりも上側の層とを電気的に接続するための第2の接続層とを備えている。上記第1の接続層CTには第1の導電部PP1aと第2の導電部PP2aとを含み、第2の接続層SNCには第3の導電部PP2bを含む。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲートトランジスタのゲート電極間の間隔の縮小を実現する不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板に、複数の第1の素子領域と、素子分離領域と、第2の素子領域を形成する。第1の素子領域上に、メモリセルゲート電極、2本の選択ゲート電極を形成し、第2の素子領域に周辺ゲート電極を形成する。第1の絶縁膜を形成し、周辺ゲート電極の側壁部上が開口される第1のレジストパターンを形成し、第1のエッチング処理を行い、側壁絶縁膜を形成する。第2のレジストパターンを形成し、第2のエッチング処理を行い、選択ゲート電極側壁部の第1の絶縁膜を除去する。第2の絶縁膜を堆積し、第3の絶縁膜を堆積する。2本の選択ゲート電極間上が開口される第3のレジストパターンを形成し、第3のエッチングおよび第4のエッチング処理を行い、コンタクトホールを形成する。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリの製造プロセスにおけるPEP数を削減する。

【解決手段】実施形態に係わる抵抗変化メモリは、第1の方向及びこれに直交する第2の方向にそれぞれ交互に配置される複数の抵抗変化素子MTJ及び複数のビアV0と、複数の抵抗変化素子MTJの側壁上に配置される複数の側壁絶縁層PLとを備える。複数の抵抗変化素子MTJは、一定ピッチで格子状に配置され、複数の側壁絶縁層PLの側壁に垂直な方向の厚さは、複数の側壁絶縁層PLが互いに部分的に接触し、複数の側壁絶縁層PL間に複数のホールが形成される値に設定される。複数のビアV0は、これら複数のホール内に配置される。

(もっと読む)

半導体装置の製造方法

【課題】非晶質炭素膜を用いて形成する電極のアスペクト比を増大させる。

【解決手段】半導体装置の製造方法は、半導体基板上に第1非晶質炭素膜を形成し、周辺回路領域の第1非晶質炭素膜を除去してメモリセル領域の第1非晶質炭素膜を第2非晶質炭素膜とし、第2非晶質炭素膜を覆う第1シリコン酸化膜を基板全面に形成し、第2非晶質炭素膜上の第1シリコン酸化膜を除去して周辺回路領域の第1シリコン酸化膜を第2シリコン酸化膜とし、第2非晶質炭素膜と第2シリコン酸化膜を覆う第1絶縁膜を形成し、第1絶縁膜に第1開口を形成し、第1開口を埋め込む第2絶縁膜を形成し、第2絶縁膜に第2開口を形成し、第2開口と第1開口が重なる位置に露出する第2非晶質炭素膜にホールを形成し、ホール内に下部電極を形成し、第2絶縁膜を除去して第1開口内に第2非晶質炭素膜を露出させ、露出した第2非晶質炭素膜を全て除去する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】メモリ・ロジック混載型の半導体装置の高性能化を可能にする技術を提供する。

【解決手段】ストッパ膜17は、ストッパ膜13及び層間絶縁膜14から成る絶縁層上に形成されている。コンタクトプラグ16,65,66のそれぞれは、その上面がストッパ膜17から露出するように、ソース・ドレイン領域9,59とそれぞれ電気的に接続されてストッパ膜13、層間絶縁膜14及びストッパ膜17に設けられている。絶縁層20は、ストッパ膜17及びコンタクトプラグ16,65,66の上に設けられている。キャパシタ82の下部電極は、メモリ形成領域において、コンタクトプラグ66の上面とストッパ膜17の上面とに接触するように絶縁層20内に設けられている。

(もっと読む)

半導体装置

【課題】ワード線の負荷を増大させることなく、ワード線に生じるノイズを低減する。

【解決手段】少なくとも一のスイッチング素子を有する複数の記憶素子がマトリクス状に配置され、前記記憶素子のそれぞれにはワード線とビット線がそれぞれ接続され、前記ワード線には少数キャリアが実質的に存在しないトランジスタのゲート(またはソース及びドレイン)が接続され、前記少数キャリアが実質的に存在しないトランジスタのソース及びドレイン(またはゲート)の電位が制御されることで前記少数キャリアが実質的に存在しないトランジスタの容量値の制御を行う半導体装置とする。前記少数キャリアが実質的に存在しないトランジスタは、ワイドギャップ半導体により設けられていればよい。

(もっと読む)

1 - 20 / 268

[ Back to top ]