Fターム[5F083MA04]の内容

Fターム[5F083MA04]に分類される特許

61 - 80 / 205

半導体記憶装置及びその製造方法

【課題】誘電体膜のクラック発生が抑制され、リーク電流特性に優れたキャパシタを有する半導体記憶装置を提供する。

【解決手段】半導体記憶装置の製造方法は、半導体基板上に窒化チタン膜を有する立体構造の下部電極を形成した後、下部電極の表面に誘電体膜を形成する。誘電体膜の表面に、誘電体膜が結晶成長しない温度で第一の上部電極を形成した後、誘電体膜が結晶成長する温度で熱処理し、誘電体膜の少なくとも一部を多結晶状態に変換する。この後、第一の上部電極表面に第二の上部電極を形成する。

(もっと読む)

半導体装置

【課題】コンタクトパッドを含む所定領域内に形成できる配線数を増加させることができ、設計レイアウトの自由度を向上させることができるパターンレイアウトを有する半導体装置を提供する。

【解決手段】第1方向に所定ピッチでラインとスペースが交互に配列された第1配線パターンと、第1配線パターンのライン間に配置され、所定ピッチの3倍の幅を有するコンタクトパッド30Bとを有する。第1配線パターンのラインとコンタクトパッドとの間隔は所定ピッチであり、所定ピッチは100nm以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリは、半導体基板1上に絶縁膜3を介して形成された制御ゲート電極CGと、半導体基板1上に電荷蓄積部を有する絶縁膜5を介して形成されたメモリゲート電極MGとを有しており、メモリゲート電極MGは、制御ゲート電極CGの側面22上に絶縁膜5を介してサイドウォールスペーサ状に形成されている。制御ゲート電極CGは、メモリゲート電極MGに絶縁膜5を介して隣接する側とは反対側の側面21の下部21aが突出し、また、メモリゲート電極MGに絶縁膜5を介して隣接する側の側面22の下部22aが後退している。メモリゲート電極MGは、制御ゲート電極CGに絶縁膜5を介して隣接する側の側面23の下部23aが突出している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極側に位置する側壁部において、面方位が(100)の第1の斜面と、第1の斜面と交差する面方位が(100)の第2の斜面と、を有する。上記構成によれば、基板の表面(110)面と(100)面とのなす角は45°となり、比較的鋭角に第1斜面が形成されるため、効果的にpチャネル型のMISFETのチャネル領域に圧縮歪みを印加することができる。

(もっと読む)

抵抗変化型メモリ

【課題】 メモリの動作特性の向上を図る。

【解決手段】実施形態の抵抗変化型メモリは、ビット線BLとワード線WLと、第1エミッタ21と、第1ベース23と、第1コレクタ22とを有する、第1駆動型の第1バイポーラトランジスタ2と、第2エミッタ31と、第2ベース33と、第2コレクタ32とを有する第2駆動型の第2バイポーラトランジスタ3と、第1及び第2端子を有する抵抗変化型メモリ素子1と、を具備し、メモリ素子1の第1端子は第1及び第2エミッタ21,31に接続され、メモリ素子1の第2端子は、ビット線BLに接続され、第1及び第2ベース23,33はワード線WLに接続される。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリセルと低電圧動作トランジスタや高電圧動作トランジスタを集積化し、異種トランジスタを混載する半導体装置の製造法を提供する。

【解決手段】半導体装置の製造方法は、(a)トンネル絶縁膜、Fゲート電極膜、電極間絶縁膜を堆積したFゲート電極構造を形成し(b)ゲート絶縁膜を形成し(c)導電膜、エッチストッパ膜を堆積し(d)エッチストッパ膜、導電膜をエッチングした積層ゲート電極構造を形成し(e)積層ゲート電極構造の側壁上に第1絶縁膜を形成し(f)積層ゲート電極側壁上に第1サイドウォールスペーサ層を形成し(g)エッチストッパ層を除去し(h)他の領域の導電層から、ゲート電極構造を形成し(i)積層ゲート電極構造、ゲート電極構造側壁上に第2サイドウォールスペーサを形成し(j)希弗酸水溶液で半導体基板表面を露出し(k)半導体基板表面にシリサイド層を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】トランジスタの電流駆動能力の低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置10は、半導体基板1の表層に第一の方向に延在するように形成された複数の活性領域1aと、前記活性領域1aの表層から深さ方向に形成されたn型不純物拡散層15と、前記複数の活性領域1aを横切り第二の方向に延在するように形成された複数の埋め込みゲート用の溝部13a,bと、ゲート絶縁膜25a,bを介して前記活性領域1a上を跨ぐように前記埋め込みゲート用の溝部13a,bに埋め込まれたゲート電極31およびダミーゲート電極32とを構成すると共に、前記半導体基板1の面上において前記第二の方向に延在する複数のワード配線層と、を具備し、前記ダミーゲート電極32の上面32cが、前記n型不純物拡散層15と前記活性領域1aとの界面よりも下方に位置していることを特徴とする。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】ワード線とコンタクトプラグとの短絡や、ワード線とビット配線との短絡を防ぐことが可能な半導体装置を提供する。

【解決手段】本発明の半導体装置100は、半導体基板50と、前記半導体基板50の表層に、形成された複数の活性領域Kと、前記活性領域Kの表層から深さ方向に形成された不純物拡散層22,24と、前記複数の活性領域Kを横切るように形成された複数の溝部7に、セルゲート絶縁膜7Aを介して前記半導体基板50の上面50aよりも下方に位置するように埋め込まれたワード9線と、前記ワード線9上を埋め込むように形成された窒化シリコンからなる埋込絶縁膜11と、前記不純物拡散層22,24に接続するビット配線と容量コンタクトプラグと、を具備し、前記ビット配線15と容量コンタクトプラグ19の少なくとも一方が、前記埋込絶縁膜11上の一部に重なるように配置されていることを特徴とする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】半導体記憶装置におけるトランジスタの特性向上と、キャパシタのリーク電流特性の両方を改善し、高信頼、高歩留のデバイスを提供する。

【解決手段】窒化チタンからなる下部電極102上に酸化ジルコニウムを主成分とする誘電体膜103を有するキャパシタにおいて、微結晶状態の酸化ジルコニウムを主成分とする誘電体膜を成膜し、2次的な結晶粒成長を伴わない条件でチタン化合物を主成分とする第一の保護膜110を形成し、その後、上部電極111を形成することで、上部電極形成時に伴う熱処理を行っても、またトランジスタの界面準位を低減する水素アニールを行っても、リーク電流の増大を抑制できる。

(もっと読む)

半導体装置及びその製造方法

【課題】立体構造キャパシタを備えた半導体装置であって、上下部電極に金属若しくは金属化合物を用いるMIM構造で、容量絶縁膜に高誘電体膜を用いるキャパシタにおいて、高誘電率でリーク電流が抑制された信頼性の高いキャパシタを備える半導体装置を提供する。

【解決手段】TiN下部電極102上に酸化ジルコニウム誘電体膜113を形成し、誘電体膜上にTiNを含む上部電極117を形成する際、誘電体膜をALD法で形成し、上部電極を形成する前に誘電体膜形成時のALD法の成膜温度を70℃以上超える温度を付加することなく、第一の保護膜116を成膜する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造工程を増加させることなく絶縁破壊耐性に優れた信頼性に懸念のない、小さな占有面積で所期の容量を確保する容量密度の高いパスコンを備えた半導体装置を実現する。

【解決手段】パスコンについて、第1の容量絶縁膜が、記憶素子のトンネル絶縁膜と共に第1の絶縁膜23で形成され、下部電極である第1の電極26が、記憶素子の浮遊ゲート電極25と共にドープト・アモルファスシリコン膜24(結晶化されたもの)で形成され、第2の容量絶縁膜が、周辺回路の5Vのトランジスタのゲート絶縁膜と共に第2の絶縁膜33で形成され、上部電極である第2の電極37が、記憶素子の制御ゲート電極36及び周辺回路のトランジスタのゲート電極41と共に多結晶シリコン膜34で形成される。

(もっと読む)

半導体記憶装置

【課題】低電源電圧下においても、安定かつ高速に動作する半導体記憶装置を実現する。

【解決手段】メモリセル列ごとにアレイ電源線(ARVD)およびダウン電源線(DWVD)を配置する。ダウン電源線は、読出し時に接地に結合され、書込み時にフローティング状態とされる。書込み時、選択列のアレイ電源線への電源電圧の供給を停止するとともに該アレイ電源線を対応のダウン電源線に接続する。電源系統を複雑化することなく、低電源電圧下においても安定にデータの書込/読出を行うことのできる半導体記憶装置を実現することができる。

(もっと読む)

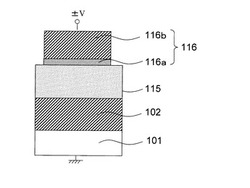

キャパシタの製造方法および半導体装置の製造方法

【課題】高温相の結晶構造の容量絶縁膜を電極上に直接形成可能なキャパシタの製造方法を提供する。

【解決手段】本発明のキャパシタCapの製造方法は、第一の電極3を形成する工程と、成膜温度が低い順に、非晶質相、低温相の結晶構造、高温相の結晶構造を形成し得る金属酸化物の形成工程であって、前記第一の電極3上に、前記低温相の結晶構造の成膜温度よりも低い第一の温度で前記非晶質相からなる前記金属酸化物を形成する工程と、前記第一の温度から、前記高温相の結晶構造の成膜温度である第二の温度まで、10℃/秒以上の昇温速度で昇温し、前記第二の温度で前記金属酸化物をアニールすることにより、前記金属酸化物に前記高温相の結晶構造を析出させて容量絶縁膜4とする工程と、前記容量絶縁膜4上に第二の電極5を形成する工程を採用する。

(もっと読む)

半導体集積回路装置

【課題】相変化メモリの信頼性を向上させる。

【解決手段】例えば、ワード線WL0とビット線BL0の交点に設けられたメモリセル内の相変化素子に対して、この相変化素子をreset動作によってアモルファス状態にする場合、ビット線BL0の立ち上がり時間trb/立ち下がり時間tfbを、ワード線WL0の立ち上がり時間trw/立ち下がり時間tfwより長くなるように構成する。この際に、reset動作で必要な相変化素子の急冷は、ワード線WL0の立ち下がり時間tfwを用いて行う。このような構成および動作を用いることで、ビット線BL0とワード線WL1の交点に設けられた非選択メモリセル内の相変化素子に対するディスターブ電流IBL01が低減する。

(もっと読む)

複合メモリ

【課題】 製造コストの上昇を招くことなくNANDフラッシュメモリにDRAMを混載することができ、且つチップ面積の増大を招くことなくシステム性能の向上をはかる。

【解決手段】 半導体基板10上に、NANDセルユニットからなる第1のメモリセルアレイとDRAMセルからなる第2のメモリセルアレイとを搭載した複合メモリであって、NANDセルユニットは、第1のゲート14と第2のゲート16を積層した2層ゲート構成の不揮発性メモリセル100と不揮発性メモリセル100の第1及び第2のゲート14,16間を接続した選択トランジスタ200で構成され、DRAMセルは、選択トランジスタ200と同じ構成のセルトランジスタ300と、不揮発性メモリセル100又は選択トランジスタ200と同じ構成のMOSキャパシタ400で構成されている。

(もっと読む)

半導体記憶装置、及び半導体記憶装置の製造方法

【課題】半導体記憶装置の面積を縮小する技術を提供する。

【解決手段】高抵抗付加型ラッチ回路(12)と、その高抵抗付加型ラッチ回路(12)に保持されるデータの読み出しと書込みとを制御する選択回路(13)とを具備する半導体記憶装置(11)を構成する。その高抵抗付加型ラッチ回路(12)は、第1駆動トランジスタ(22)と、第2駆動トランジスタ(24)と、第1抵抗(121)と、第2抵抗(123)とを備えることが好ましい。また、その選択回路(13)は、第1選択トランジスタ(31)と、第2選択トランジスタ(32)とを備えることが好ましい。ここにおいて、その第1抵抗(121)と第2抵抗(123)とは、サイドウォール状の導電性材料(21)(23)で形成されるものである。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の小型化を図ること。

【解決手段】第1の領域IにフラッシュメモリセルFLを形成する工程と、第2の領域IIにキャパシタQの第1の電極11aを形成する工程と、第2の絶縁膜14として第1の酸化シリコン膜14a、窒化シリコン膜14b、及び第2の酸化シリコン膜14cをこの順に形成する工程と、第1の電極11aの一部領域CRにおける窒化シリコン膜14bと第2の酸化シリコン膜14cとを除去する工程と、第3の領域IIIHにおける第1の絶縁膜10と第2の絶縁膜14とをウエットエッチングする工程と、キャパシタQの第2の電極30aを形成する工程と、一部領域CRにおける第1の酸化シリコン膜14aをエッチングして除去する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、メモリセルアレイを有する半導体装置において、直列に接続された第1乃至第mのメモリセルに含まれる各ノードに生じる寄生容量の値を同等の値とすることで、安定して動作可能な半導体装置とする。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】半導体記憶装置を微細化した場合であっても、十分にカップリング比を高くする。

【解決手段】半導体記憶装置は、マトリクス状に配置されたメモリセルと複数のワード線16とを有する。メモリセル13は、行方向に複数個直列接続される。ワード線16は、複数のメモリセル13の制御ゲートを行方向と直交する列方向にそれぞれ接続する。メモリセル13の行方向の間隔は、第1の間隔と第1の間隔より広い第2の間隔とが交互に繰り返されている。

(もっと読む)

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

61 - 80 / 205

[ Back to top ]