Fターム[5F083MA16]の内容

Fターム[5F083MA16]に分類される特許

201 - 220 / 1,403

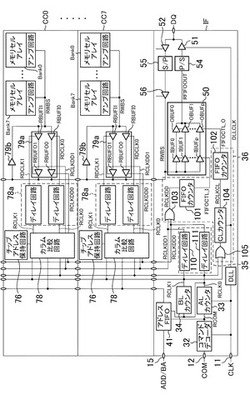

半導体装置

【課題】積層型の半導体装置においてリードデータの有効幅(ウィンドウ幅)を十分に確保する。

【解決手段】積層された複数のコアチップCC0〜CC7と、コアチップを制御するインターフェースチップIFとを備える。コアチップのそれぞれは、メモリセルアレイ70と、データ用の貫通電極TSV1と、メモリセルアレイ70から読み出されたリードデータをデータ用の貫通電極TSV1に出力する出力回路RBUFOとを備える。コアチップにそれぞれ設けられたデータ用の貫通電極TSV1は互いに共通接続され、コアチップにそれぞれ設けられた出力回路RBUFOはインターフェースチップIFより供給されるリードクロック信号RCLKDDに応答して活性化される。これにより、各コアチップの動作速度にばらつきが存在する場合であってもデータバス上でリードデータの競合が生じることがない。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグ形成時に位置ずれが発生しても水分や不純物が溜まる窪みが発生することがなく、微細化しても長期間にわたる信頼性を確保できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1の絶縁膜121の上に形成された強誘電体キャパシタ131と、強誘電体キャパシタ131を覆う第2の絶縁膜311及びエッチングストッパ膜312と、エッチングストッパ膜312の上面からトランジスタTの不純物領域に到達する第1のコンタクトホール内に導電体材料を充填して形成された第1のプラグ313と、エッチングストッパ膜の上に形成された第3の絶縁膜314と、第3の絶縁膜314の上面から第1のプラグに到達する第2のコンタクトホール内に導電体材料を充填して形成された第2のプラグ315とを有する。

(もっと読む)

キャパシタの形成とともに不揮発性メモリのゲートスタックをパターニングするための方法

【課題】キャパシタのエッチングはNVMセルのエッチングの終点検出に有用になるようにキャパシタおよびNVMセルを集積するように形成する。

【解決手段】NVM領域およびキャパシタ領域上に2つの導電体層を用いるように達成される。第1導電体層は後のパターニングステップの準備にパターニングされ、これが、NVM領域およびキャパシタ領域の両方に第1導電体層および第2導電体層の両方をパターニングするステップを含む。後のエッチングが、同一マスクを用いて両方の導電体層をエッチングされることによって制御ゲート上に浮遊ゲートの重要な配列を提供する。この後のエッチングの間、キャパシタ領域に第1導電体材料をエッチングされることが、NVM領域における第1導電体層のエッチングの終点検出を補助する。

(もっと読む)

側壁構造化スイッチャブル抵抗器セル

【課題】抵抗を大きくして感知されやすくするとともに、リセット電流を小さくし、製造中の損傷も抑制できる抵抗率スイッチング素子を提供する。

【解決手段】第1の伝導性電極28を形成するステップと、第1の伝導性電極28の上に絶縁構造13を形成するステップと、絶縁構造の側壁上に抵抗率スイッチング素子14を形成するステップと、抵抗率スイッチング素子14の上に第2の伝導性電極26を形成するステップと、第1の伝導性電極28および第2の伝導性電極26の間に抵抗率スイッチング素子14と直列にステアリング素子を形成するステップと、を含み、第1の伝導性電極28から第2の伝導性電極26への第1の方向における抵抗率スイッチング素子14の高さTは第1の方向に垂直な第2の方向における抵抗率スイッチング素子14の厚さIより大きい。

(もっと読む)

半導体装置の製造方法

【課題】 セレクトゲート部におけるゲート閾値電圧が安定した半導体装置の製造方法を提供する。

【解決手段】 実施形態に係る半導体装置の製造方法では、メモリセル部及びセレクトゲート部が形成される。半導体基板上にトンネル絶縁膜が形成され、前記トンネル絶縁膜上に電荷蓄積層が形成される。前記電荷蓄積層、前記トンネル絶縁膜、及び前記半導体基板のエッチングにより素子分離溝部が形成され、前記電荷蓄積層の側面に接するように前記素子分離溝部に素子分離絶縁膜が埋め込まれる。前記電荷蓄積層及び前記素子分離絶縁膜上に電極間絶縁膜が形成され、前記セレクトゲート部において、前記電極間絶縁膜がエッチングされる。前記電極間絶縁膜を覆い、前記電荷蓄積層に接続するシリコン膜が形成され、前記シリコン膜上に金属膜が形成される。熱処理により、前記セレクトゲート部において、前記トンネル絶縁膜に接する前記電荷蓄積層がシリサイド化される。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、接合リーク電流を低減可能で、かつトランジスタの信頼性を向上させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート電極61よりも上方に配置されたゲート絶縁膜21、及びゲート電極61の上面61aを覆う水素含有絶縁膜62と、水素含有絶縁膜62を介して、ゲート電極用溝17の上部17Bを埋め込むフッ素含有絶縁膜63と、を備え、ゲート絶縁膜21と接触する第1及び第2の不純物拡散領域65,66の面に、半導体基板13に含まれるシリコンと水素含有絶縁膜62に含まれる水素とが結合したSi−H結合、及び半導体基板13に含まれるシリコンとフッ素含有絶縁膜63に含まれるフッ素とが結合したSi−F結合を有する。

(もっと読む)

記憶装置及び電子機器

【課題】メモリセル毎に選択動作を行う。

【解決手段】装置は、第1のメモリセルと、第1のメモリセルと同じ行に設けられた第2のメモリセルと、を具備し、前記第1及び第2のメモリセルのそれぞれは、第1のゲート及び第2のゲートを有し、オン状態又はオフ状態になることにより、メモリセルにおける少なくともデータの書き込み及びデータの保持を制御する電界効果トランジスタを備え、前記第1のメモリセル及び前記第2のメモリセルが備える前記電界効果トランジスタの前記第1のゲートのそれぞれに電気的に接続される行選択線と、前記第1のメモリセルが備える前記電界効果トランジスタの前記第2のゲートに電気的に接続される第1の列選択線と、前記第2のメモリセルが備える前記電界効果トランジスタの前記第2のゲートに電気的に接続される第2の列選択線と、をさらに具備する。

(もっと読む)

抵抗変化型不揮発性記憶装置

【課題】メモリセルのトランジスタのサイズを最適化可能とした抵抗変化型不揮発性記憶装置を提供する。

【解決手段】下部電極309aと上部電極309cと両電極間に与えられる極性の異なる電気的信号に基づいて高抵抗状態と低抵抗状態とを可逆的に変化する抵抗変化層309bとからなる抵抗変化素子309と、半導体基板301と2つのN型拡散層領域302a、302bとからなるトランジスタ317とを直列に接続してなるメモリセル300を備え、抵抗変化層309bは酸素不足型の遷移金属の酸化物層からなり、下部電極309aと上部電極309cは、異なる元素からなる材料によって構成され、下部電極309aの標準電極電位V1と上部電極309cの標準電極電位V2と前記遷移金属の標準電極電位VtとがVt<V2かつV1<V2なる関係を満足し、下部電極309aとN型拡散層領域302bとが接続されている。

(もっと読む)

フィン型不揮発性メモリ素子

【課題】不揮発性メモリ素子は小型化や低消費電力化の要求がある。不揮発性メモリ素子をフィン型とすれば小型化できるが、バルク領域に正しく電位を印加できないので正しく情報の書き込みと消去とができなかった。

【解決手段】本発明のフィン型不揮発性メモリ素子は、不揮発性メモリ素子のゲート電極とは別に、バルク領域に直接電位を印加するバルク電極を設けた。これにより、バルク領域の電位を自由に印加できるようになり、正しく情報が書き込み及び消去できるようになる。また、バルク電位を自由に可変できるので、書き込みや消去にかかる電圧を低下させることもでき、低消費電力化を行える。

(もっと読む)

相変化メモリ装置

【課題】本発明は、相変化記録層に対する加熱を効率良く行うことができ、書き込み電流の低減を可能とする相変化メモリ装置を提供する。

【解決手段】ヒータプラグと、前記ヒータプラグと接して設けられた相変化記録層とを含んで構成される記憶素子を備え、前記ヒータプラグ及び前記相変化記録層のうち少なくとも一方の内部に空隙が設けられていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体集積回路内の抵抗素子の抵抗値のばらつきを抑制した半導体装置を提供する。

【解決手段】半導体装置は基板を備える。第1の絶縁膜は基板上に設けられる。第1の抵抗部は第1の絶縁膜上に設けられる。境界膜は第1の抵抗部上に設けられる。第2の抵抗部は境界膜上に設けられる。第2の絶縁膜は、第2の抵抗部上に設けられている。第1の導電部および第2の導電部は、第2の絶縁膜上に設けられ、互いに絶縁されている。第1の導電部は、第2の絶縁膜および第2の抵抗部を貫通して境界膜の表面に接触する第1のコネクト部を含む。第2の導電部は、第2の絶縁膜および第2の抵抗部を貫通して境界膜の表面に接触する第2のコネクト部を含む。第1の抵抗部は、一端において第1のコネクト部を介して第1の導電部に電気的に接続され、かつ、他端において第2のコネクト部を介して第2の導電部に電気的に接続された抵抗素子である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】安定した性能と高い生産性とを実現する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、メモリセルアレイ部と、第1平面内においてメモリセルアレイ部と並置されたコンタクト部と、を備えた不揮発性半導体記憶装置が提供される。メモリセルアレイ部は、積層体、半導体層、メモリ膜を含む。積層体は、第1平面に対して垂直な第1軸に沿って積層された複数の電極膜とそれらの間の電極間絶縁膜とを含む。半導体層は電極膜の側面に対向する。メモリ膜は電極膜と半導体層との間に設けられ電荷保持層を含む。コンタクト部は、コンタクト部絶縁層と複数のコンタクト電極とを含む。コンタクト部絶縁層は、コンタクト部絶縁膜と粒子とを含む。コンタクト電極はコンタクト部絶縁層を第1軸に沿って貫通する。コンタクト電極は電極膜に接続される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造工程数の削減が可能な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1、第2積層体、第1、第2半導体ピラー、第1、第2メモリ膜、接続部及び分断部を備えた不揮発性半導体記憶装置が提供される。第1、第2積層体は、第1軸に沿って積層された複数の第1、第2電極膜と、第1、第2電極膜間に設けられた第1、第2電極間絶縁膜と、をそれぞれ含む。第1、第2半導体ピラーは第1、第2積層体を第1軸に沿って貫通する。第2積層体は、第1積層体と並置される。接続部は第1、第2半導体ピラーを接続する。第1メモリ膜は、第1、第2電極膜と、第1、第2半導体ピラーとの間に設けられる。分断部は、第1、第2半導体ピラー間で第1、第2電極膜を分断し、接続部に接し、第1メモリ膜に用いられる材料を含む積層膜を含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】所定のレイアウト面積内において複数の抵抗値が得られる抵抗素子を有する不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板13上に配置された絶縁膜14と、絶縁膜14上に配置された導電層12と、導電層12上に配置された絶縁膜16と、絶縁膜16上に配置され、開口部を介して導電層12に接続された導電層11Aと、導電層11Aに接続されたコンタクト24Aと、絶縁膜16上に配置され、開口部を介して導電層12に接続された導電層11Bと、導電層11Bに接続されたコンタクト24Bと、絶縁膜16上に配置され、開口部を介して導電層12に接続された導電層11Cと、導電層11Cに接続されたコンタクト24Cとを備える。導電層12はフローティングゲート層と同じ材料から形成され、導電層11A、11B、11Cはコントロールゲート層と同じ材料から形成されている。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置の面積を削減する。

【解決手段】複数のメモリセル(NMC,DMC)のうち周辺回路領域(PC)に隣接するメモリセル(DMC)と半導体基板(100)との間には、そのメモリセル(DMC)の下部電極(M13)から半導体基板(100)に向けて延伸するコンタクトプラグが形成されていない。第1のコンタクトプラグ(C101)は、半導体基板(100)の平面視において第1のコンタクトプラグの端面の少なくとも一部がメモリセルアレイ(MARY)の周縁よりも内側に配置されるように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】微細なパターンを含む半導体装置の信頼性を向上する。

【解決手段】本実施形態の半導体装置は、素子形成領域100内の半導体素子と、素子形成領域100内から引き出し領域150内に延在する複数の配線WLと、引き出し領域150内の配線WLに接続されるコンタクト部39と、を具備し、配線WLは、n番(nは1以上の整数)の側壁膜のパターンに対応する(n+1)番目の側壁膜のパターンに基づいて形成され、配線WLの配線幅WW又は素子形成領域150内の配線間隔WDに対応する第1の寸法は、リソグラフィの解像度の限界寸法より小さく、露光波長がλ、レンズの開口数がNA、プロセスパラメータがk1で示される場合、第1の寸法は、(k1/2n)×(λ/NA)以下であり、引き出し領域内で互いに隣接する配線WLの間隔WC2に対応する第2の寸法は第1の寸法より大きい。

(もっと読む)

抵抗変化型不揮発性半導体記憶装置

【課題】相変化材料配線、抵抗変化材料配線の書き込み電流(Set、Reset電流)、読み出し電流を大幅に低減し、より微細化を可能にし、メモリセルサイズを縮小することを可能にする抵抗変化型不揮発性半導体記憶装置を提供すること。

【解決手段】カルコゲナイド配線GSTと、両端の各々に接続した抵抗配線と、前記抵抗配線のそれぞれの他端を、ソース、ドレインに接続したセルトランジスタとからメモリセルMCを構成し、前記メモリセルを複数直列接続し、一端を、ソースに接続し、ドレインをビット線に接続した選択トランジスタと、前記複数直列接続の他端をソース線に接続し、前記メモリセルのゲートをワード線に接続し、前記選択トランジスタのゲートとブロック選択線に接続したものからセルストリングを構成し、前記セルストリングを複数配設してメモリセルアレイを構成することを特徴とする相変化メモリ。

(もっと読む)

集積回路とその方法

【課題】標準/低温処理技術と適合しキャパシタンスの密度を向上させる多層構造で使用されるCMPと適合性を有するキャパシタ構造を提供する。

【解決手段】キャパシタ構造体は、集積回路の誘電体層の開口101内に形成される。下部電極層102は、開口101の側面表面の少なくとも一部の上にのびるが、誘電体層405の上部表面までにはのびていない。誘電体材料層405が、この下部電極102の上と、集積回路誘電体層203の上部表面の上に配置される。最後に上部電極層406が、この誘電体材料層405の上に形成される。上部電極層406と下部電極層102のオーバーラップは存在せず、平面化プロセスの間発生することのある短絡の問題を回避できる。

(もっと読む)

半導体装置及びその作製方法

【課題】しきい値電圧の制御が困難な酸化物半導体を活性層に用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】一対の第1の領域、一対の第2の領域及び第3の領域を有する酸化物半導体膜と、酸化物半導体膜と接して設けられる一対の電極と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を介し、一対の電極の間に設けられたゲート電極と、を有し、一対の第1の領域は一対の電極と重畳し、第3の領域はゲート電極と重畳し、一対の第2の領域は一対の第1の領域及び第3の領域の間に形成され、一対の第2の領域及び第3の領域には窒素、リン、または砒素のいずれかの元素が含まれており、該元素の濃度は、第3の領域より一対の第2の領域のほうが高い構成とする。

(もっと読む)

記憶装置

【課題】アモルファスシリコンを記憶部に用いる記憶装置の動作電圧を低減し、かつ、それを低温プロセスで形成する。

【解決手段】実施形態に係わる記憶装置は、結晶化されたSixGe1−x (0≦x<1)層を含む第1の電極EL1と、金属元素を含む第2の電極EL2と、第1及び第2の電極EL1,EL2間に配置され、アモルファスSi層を含む可変抵抗部VRと、アモルファスSi層内の金属元素を含むフィラメントの長さを制御する制御回路とを備える。

(もっと読む)

201 - 220 / 1,403

[ Back to top ]