Fターム[5F083NA01]の内容

Fターム[5F083NA01]に分類される特許

181 - 200 / 3,470

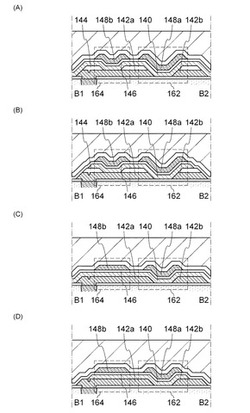

半導体装置

【課題】電力供給がない状況で記憶保持が可能で、書き込み回数に制限が無い、新たな半導体装置を提供する。

【解決手段】チャネル領域と第1のゲート絶縁層と第1のゲート電極と第1のソース及びドレイン電極とを有する第1のトランジスタと、酸化物半導体層140と第2のソース電極142a及び第2のドレイン電極142bと第2のゲート絶縁層146と第2のゲート電極148aとを有する第2のトランジスタ162と、第2のソース電極142aまたは第2のドレイン電極142bの一方と第2のゲート絶縁層146と第2のゲート絶縁層146上に第2のソース電極142a又は第2のドレイン電極142bの一方と重なるように設けられた第3の電極148bとを有する容量素子164と、を有し、第1のゲート電極と第2のソース電極142a又は第2のドレイン電極142bの一方とは接続され、第3の電極148bは酸化物半導体層140と重なる領域を有する。

(もっと読む)

半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供する

ことを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウ

ム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて

、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化

物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以

下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有

し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でス

パッタリングを行う。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリの製造プロセスにおけるPEP数を削減する。

【解決手段】実施形態に係わる抵抗変化メモリは、第1の方向及びこれに直交する第2の方向にそれぞれ交互に配置される複数の抵抗変化素子MTJ及び複数のビアV0と、複数の抵抗変化素子MTJの側壁上に配置される複数の側壁絶縁層PLとを備える。複数の抵抗変化素子MTJは、一定ピッチで格子状に配置され、複数の側壁絶縁層PLの側壁に垂直な方向の厚さは、複数の側壁絶縁層PLが互いに部分的に接触し、複数の側壁絶縁層PL間に複数のホールが形成される値に設定される。複数のビアV0は、これら複数のホール内に配置される。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

半導体装置の製造方法

【課題】W膜で発生していたウィスカを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板上にシリコン膜を形成する工程S108と、前記シリコン膜上にタングステン膜を形成する工程S109と、ゲート領域に前記タングステン膜と前記シリコン膜とが存在するように、前記タングステン膜と前記シリコン膜とを貫通する開口部を形成する工程S110と、前記開口部を形成した後に、前記シリコン膜よりも前記タングステン膜がより多く窒化されるように窒化処理を行う工程S114と、窒化処理の後、少なくとも前記タングステン膜上にシリコン酸化膜を形成する工程S118と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】非晶質炭素膜を用いて形成する電極のアスペクト比を増大させる。

【解決手段】半導体装置の製造方法は、半導体基板上に第1非晶質炭素膜を形成し、周辺回路領域の第1非晶質炭素膜を除去してメモリセル領域の第1非晶質炭素膜を第2非晶質炭素膜とし、第2非晶質炭素膜を覆う第1シリコン酸化膜を基板全面に形成し、第2非晶質炭素膜上の第1シリコン酸化膜を除去して周辺回路領域の第1シリコン酸化膜を第2シリコン酸化膜とし、第2非晶質炭素膜と第2シリコン酸化膜を覆う第1絶縁膜を形成し、第1絶縁膜に第1開口を形成し、第1開口を埋め込む第2絶縁膜を形成し、第2絶縁膜に第2開口を形成し、第2開口と第1開口が重なる位置に露出する第2非晶質炭素膜にホールを形成し、ホール内に下部電極を形成し、第2絶縁膜を除去して第1開口内に第2非晶質炭素膜を露出させ、露出した第2非晶質炭素膜を全て除去する。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

半導体装置

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】第1のトランジスタ及び第2のトランジスタを有するメモリセルを有し、第1のトランジスタは第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタは酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される不揮発性メモリによって解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】選択用トランジスタのゲート電極と記憶用トランジスタのゲート電極との間の耐圧を確保し、かつ閾値電圧の変動が抑制されたMONOS型メモリセルを提供する。

【解決手段】主表面SBSを有する半導体基板SUBと、主表面SBS上に形成された第1のゲート電極CGと、主表面SBS上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる第1の絶縁膜ONOとを備える半導体装置である。上記第2のゲート電極MGの最上面MGSは第1のゲート電極CGの最上面CGSより低くなっている。上記第2のゲート電極MGの最上面MGSは主表面SBSに沿うように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の占有面積を実質的に減少させる。

【解決手段】半導体装置は、第1の方向及びそれと交差する第2の方向に沿って半導体基板上に配列形成された複数の第1の接続領域と、複数の第1の接続領域を第1の方向に沿った列ごとに電気的に接続する複数の配線とを含む。複数の配線は、第2の方向に隣り合う2つの配線が互いに異なる配線層に配置され、かつ平面視において一部が重なってハニカム状に見えるように屈曲させてある。

(もっと読む)

半導体集積回路

【課題】記憶装置の消費電力を低減すること、記憶装置の面積を低減すること、記憶装置を構成するトランジスタの数を低減する。

【解決手段】第1の出力信号及び第2の出力信号の電位を比較する比較器と、第1の酸化物半導体トランジスタ及び第1のシリコントランジスタを有する第1のメモリ部と、第2の酸化物半導体トランジスタ及び第2のシリコントランジスタを有する第2のメモリ部と、当該第1の出力信号及び当該第2の出力信号の電位を確定する出力電位確定器とを有し、当該第1の酸化物半導体トランジスタのソース又はドレインの一方は、当該第1のシリコントランジスタのゲートに電気的に接続されており、当該第2の酸化物半導体トランジスタのソース又はドレインの一方は、当該第2のシリコントランジスタのゲートに電気的に接続されている記憶装置に関する。

(もっと読む)

記憶装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な記憶装置、及び該記憶装置を有する半導体装置を提供する。

【解決手段】第1の入力端子、及び第1の入力端子の入力信号の反転信号が入力される第2の入力端子、並びに第1の信号が出力される第1の出力端子、及び第1の信号の反転信号が出力される第2の出力端子、を有するレベルシフタと、第1の信号が入力される第3の入力端子、及び第1の信号の反転信号が入力される第4の入力端子、並びに第3の出力端子を有する第1のバッファと、第1の信号の反転信号が入力される第5の入力端子、及び第1の信号が入力される第6の入力端子、並びに第4の出力端子を有する第2のバッファと、を有し、第1のバッファの第3の出力端子から出力される信号が、レベルシフタの第1の入力端子に入力され、第2のバッファの第4の出力端子から出力される信号が、レベルシフタの第2の入力端子に入力される。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

半導体装置及びその製造方法

【課題】第2の部分の寄生容量を低下させることにより、半導体装置の特性を向上させる。

【解決手段】MISトランジスタは、半導体基板上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられ、第1の幅W1を有する第1の部分と第2の幅W2を有する第2の部分とを有するゲート電極を有する。第2の部分の側壁上には、酸化シリコン膜が設けられている。第2の部分に接するゲート絶縁膜は、第1の部分に接するゲート絶縁膜よりも厚くなっている。

(もっと読む)

セルの配置構造、半導体集積回路、及び回路素子セルの配置方法

【課題】セルベース設計において複数の記憶素子セルが配置される構成において、効率的に且つ確実に複数ビットのソフトエラーの発生を抑制することが可能なセルの配置構造を提供する。

【解決手段】回路素子セルの配置構造は、第1の方向に延展するセル配置列上に並べられた複数の記憶素子セルと、複数の記憶素子セルの各々の領域において第1の方向に垂直な第2の方向に並べられた第1のNウェル及び第1のPウェルと、複数の記憶素子セルのうち少なくとも2つの互いに隣接する記憶素子セルの間に設けられ、セル配置列の幅に亘る長さを各々が有する第2のNウェル及び第2のPウェルとを含み、第1のNウェルと第2のNウェルとは一体であり、第1のPウェルと第2のPウェルとは一体である。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性半導体装置の高集積化を図ることのできる技術を提供する。

【解決手段】スイッチ用nMIS(Qs)のスイッチゲート電極SGと、スイッチ用nMIS(Qs)にワード線に対して交差する方向に沿って隣接するメモリ用nMIS(Qm)のメモリゲート電極MGとの間に、スイッチ用nMIS(Qs)のソース/ドレイン領域SDHとして機能し、同時にメモリ用nMIS(Qm)のドレイン領域Dとして機能する半導体領域を形成し、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)側のソース/ドレイン領域SDHを構成する半導体領域の形状と、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)と反対側(ビット線側)のソース/ドレイン領域SDLを構成する半導体領域の形状とを非対称とする。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】STIの形成によるウェル拡散層の不純物濃度の変化を抑制し、かつ、ウェル拡散層のドーズロスを抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。メモリセル領域には、複数のメモリセルが半導体基板上に形成されている。周辺回路領域には、複数のメモリ素子を制御する複数の半導体素子が形成されている。素子分離領域は、複数のメモリセル間を分離し、あるいは、複数の半導体素子間を分離する。周辺回路領域において半導体素子が形成されているアクティブエリアの不純物濃度は、半導体基板の表面に対して水平方向に素子分離領域の側面からアクティブエリアの内部へ向かって低下している。

(もっと読む)

半導体装置の製造方法

【課題】DHF処理後に実施されるHPM処理またはAPM処理を、良好に行うことができる半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、槽内に水を導入して、槽内から希フッ酸を排出する工程と、槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、槽内に、H2O2と、上記水よりも温度の高い温水とを導入する工程とを有する。

(もっと読む)

記憶素子及び記憶装置

【課題】電力の供給が停止した後もデータを保持することができる、新たな構成の記憶素子を提供することを目的の一とする。

【解決手段】記憶素子は、ラッチ回路と、第1の選択回路と、第2の選択回路と、第1の不揮発性記憶回路と、第2の不揮発性記憶回路と、を有する。また、第1の不揮発性記憶回路及び第2の不揮発性記憶回路は、それぞれトランジスタ及び容量素子を有する。第1及び第2の不揮発性記憶回路のそれぞれが有するトランジスタは、チャネルが酸化物半導体膜に形成されるトランジスタである。当該トランジスタは、オフ電流が極めて低いため、トランジスタと容量素子の接続点であるノードにデータが入力された後、トランジスタがオフ状態となり、電源電圧の供給が停止しても、長期間にわたりデータを保持することができる。

(もっと読む)

181 - 200 / 3,470

[ Back to top ]