Fターム[5F083PR05]の内容

Fターム[5F083PR05]に分類される特許

141 - 160 / 1,312

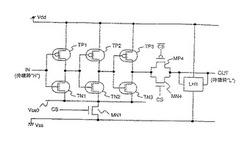

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体装置

【課題】実施形態によれば、他の特性を損ねずにセル間の電荷の移動を抑制することができる半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、積層体と、第1の絶縁膜と、電荷蓄積膜と、第2の絶縁膜と、チャネルボディとを備えている。積層体は、基板上にそれぞれ交互に積層された複数の電極層と複数の絶縁層とを有する。第1の絶縁膜は積層体を貫通して形成されたホールの側壁に設けられている。電荷蓄積膜はホール内における第1の絶縁膜の内側に設けられている。電荷蓄積膜は、電極層に対向する部分で電極層に向かって突出し、他の部分よりも膜厚が厚い凸部を有する。第2の絶縁膜は電荷蓄積膜の内側に設けられている。チャネルボディは第2の絶縁膜の内側に設けられている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量コンタクトプラグと半導体基板の活性領域との間の重ねマージンを十分に確保して、低抵抗且つ接続信頼性の高い半導体装置を提供する。

【解決手段】埋め込みゲート電極19A及びキャップ絶縁膜20Aと、活性領域1Aの上面に設けられたビットコンタクト27A及びビット線27と、半導体基板1上に設けられた絶縁層32,40と、第1容量コンタクトプラグ39Aと、を備え、第1容量コンタクトプラグ39Aは、柱状部39aとこの柱状部39aの下方に設けられた板状部39bとを有し、板状部39bの底面と、素子分離領域及びキャップ絶縁膜20Aによって区画された活性領域1Aの表面1a,1cとが全面で接触するように設けられていることを特徴とする半導体装置を選択する。

(もっと読む)

記憶装置およびその製造方法

【課題】メモリセルの構造を最適化することにより、更なる微細化を可能にする記憶装置を提供する。

【解決手段】複数の第1の電極配線と、第1の電極配線と交差する複数の第2の電極配線と、1本の第2の電極配線と、互いに隣接する2本の第1の電極配線との間に形成される1個のビアプラグであって、前記第1の電極配線に対向する底面の、第1の電極配線の伸長方向に垂直な方向の最大径が、第1の電極配線幅の2倍と第1の電極配線間の幅を加えた長さよりも小さいビアプラグと、ビアプラグと2本の第1の電極配線の一方との間に形成される第1の記憶素子と、ビアプラグと2本の第1の電極配線の他方との間に形成される第2の記憶素子とを有する記憶装置。

(もっと読む)

半導体メモリ素子及びその製造方法

【課題】垂直型トランジスタを形成する過程において、ゲートと接触する活性領域の面積を増加させてゲートの接触抵抗特性を改善し、チャネル幅を増加させる半導体メモリ素子及びその製造方法を提供する。

【解決手段】第1の方向に延長するように形成された下部ピラーと、下部ピラー上に第1の方向と垂直な第2の方向に突出するように形成された上部ピラー290と、下部ピラーの一側壁に配置された埋め込みビットライン接合領域265と、トレンチを一部埋め込む埋め込みビットライン280と、エッチング停止膜285a上に形成された少なくとも上部ピラーの外周側面の一部を露出するようにリセスされた第1の層間絶縁膜290と、第1の層間絶縁膜上に形成された第2の層間絶縁膜295と、側面の一部が露出した上部ピラーの外周側面を覆いつつ、埋め込みビットラインと相互交差するゲート320aとを備えるように形成される。

(もっと読む)

プリント不揮発性メモリ

【課題】低コストで高スループットなプリント技術を使用した不揮発性メモリセルを提供する。

【解決手段】同一水平レベルにおいて所定の距離で離間している第1及び第2の半導体アイランドであって、第1の半導体アイランド2が制御ゲートを構成し、第2の半導体アイランド3がソース端子及びドレイン端子を構成する、当該第1及び第2の半導体アイランドと、第1の半導体アイランド2の少なくとも一部の上のゲート誘電体層4と、第2半導体アイランドの少なくとも一部の上のトンネリング誘電体層5と、ゲート誘電体層4とトンネリング誘電体層5の少なくとも一部の上のフローティングゲート7と、制御ゲート2並びにソース端子及びドレイン端子に電気的に接触する金属層と、を備える。一つの効果的な実施形態では、不揮発性メモリセルを、「全プリント」加工技術を使用して製造することができる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】浮遊ゲートと制御ゲートとの間におけるリークを抑制することができる不揮発性半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコンを含む基板と、前記基板上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた浮遊ゲートと、前記浮遊ゲート上に設けられたリーク抑制部と、前記リーク抑制部上に設けられたゲート間絶縁膜と、前記ゲート間絶縁膜上に設けられた制御ゲートと、を備える。前記リーク抑制部の誘電率は、前記ゲート間絶縁膜の誘電率よりも高くなっている。

(もっと読む)

半導体記憶装置の製造方法

【課題】高集積化を図ることができる半導体記憶装置の製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、基板上に第1膜と第2膜とを交互に積層して第1積層体を形成する工程と、前記第1積層体上に第3膜と第4膜とを交互に積層して第2積層体を形成する工程と、前記第1膜のエッチング速度よりも前記第3膜のエッチング速度の方が低くなる条件でエッチングを施すことにより、前記第2積層体及び前記第1積層体を貫く貫通ホールを形成する工程と、前記貫通ホールの内面上に電荷蓄積膜を形成する工程と、前記貫通ホール内に半導体部材を形成する工程と、を備える。そして、前記第1膜と前記第2膜とを相互に異なる材料によって形成し、前記第3膜と前記第4膜とを相互に異なる材料によって形成し、前記第1膜と前記第3膜とを相互に異なる材料によって形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】活性領域とビット線コンタクトとの間の接触面積が大きく、コンタクト抵抗の低下が図られた半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、基板1に形成された第1の方向に延在する第1の溝4と、第1の溝4の下部を埋めこんで形成された第2の絶縁層6と、基板1に形成された第1の方向に直交する第2の方向に延在する複数の第2の溝と、第2の溝の下部を埋めこんで第2の溝内に形成されたワード線と、第1の溝4と第2の溝とによって基板1内に区画して形成され、基板1に垂直に立設すると共に、上部に拡散領域23aを有する半導体ピラー1dと、第1の方向に並ぶ所定数ごとの半導体ピラー1dにその上部の側面を介して拡散領域23aに接続するビット線コンタクト22aと、ビット線コンタクト22aに接続するビット線26と、を備える。

(もっと読む)

半導体記憶装置

【課題】動作速度が高い半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、一方向に沿って相互に平行に配列された複数枚のゲート電極膜と、前記一方向に延び、前記複数枚のゲート電極膜を貫通する半導体部材と、前記ゲート電極膜と前記半導体部材との間に設けられた電荷蓄積膜と、を備える。前記ゲート電極膜における前記半導体部材に対向した端部には、前記一方向に沿って突出した凸部が設けられており、前記ゲート電極膜間の空間の一部は気体層となっている。

(もっと読む)

不揮発性抵抗変化素子

【課題】電極との間で金属の出し入れが行われることで可逆的に抵抗が変化される抵抗変化層の絶縁性の劣化を抑制する。

【解決手段】抵抗変化層2は半導体元素を有し、第2電極4の金属元素が出し入れされることで可逆的に抵抗変化が可能で、誘電体層3は、第2電極4と抵抗変化層2との間に挿入され、抵抗変化層2よりも第2電極4の金属元素の拡散係数が小さい。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置、およびその作製方法を提供することである。

【解決手段】基板上に下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、第1の加熱処理を行って第2の酸化物半導体膜を形成した後、選択的にエッチングして、第3の酸化物半導体膜を形成し、第1の絶縁膜および第3の酸化物半導体膜上に絶縁膜を形成し、第3の酸化物半導体膜の表面が露出するように絶縁膜の表面を研磨して、少なくとも第3の酸化物半導体膜の側面に接するサイドウォール絶縁膜を形成した後、サイドウォール絶縁膜および第3の酸化物半導体膜上にソース電極およびドレイン電極を形成し、ゲート絶縁膜およびゲート電極を形成する。

(もっと読む)

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

半導体装置の製造方法

【課題】側壁マスクプロセスにより同時に異なる幅を持つパターンを形成する。

【解決手段】実施形態に係わる半導体装置の製造方法は、被加工材12上に第1及び第2の芯材を形成する工程と、第1及び第2の芯材の上面及び側面を覆う第1及び第2の層16a,16bを有する被覆材を形成する工程と、第1の芯材を覆う第2の層16bを除去する工程と、被覆材をエッチングすることにより、第1の芯材の側面に第1の層16aを有する第1の側壁マスクを形成し、第2の芯材の側面に第1及び第2の層16a,16bを有する第2の側壁マスクを形成する工程と、第1及び第2の芯材を除去する工程と、第1及び第2の側壁マスクをマスクとして被加工材12をエッチングすることにより、異なる幅を持つ第1及び第2のパターンを同時に形成する工程とを備える。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

電界効果トランジスタを備える半導体素子及びその製造方法

【課題】電界効果トランジスタを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成され、第1活性領域の上面及び向き合う側面を経て伸張する第1ゲート電極を有する第1導電型の第1FET素子と、前記第1FET素子上に形成された層間絶縁膜と、前記層間絶縁膜上に形成され、第2活性領域の上面及び向き合う側面を経て伸張する第2ゲート電極を有する第2導電型の第2FET素子と、を備える。

(もっと読む)

記憶素子、記憶装置、信号処理回路、記憶素子の駆動方法

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶素子を提供する。消費電力の低減可能な信号処理回路を提供する。

【解決手段】クロック信号に同期してデータを保持する記憶素子において、酸化物半導体層にチャネルが形成されるトランジスタ及び容量素子を用いることより、電源電圧の供給が停止した間もデータ保持ができる。ここで、電源電圧の供給を停止する前に、クロック信号のレベルを一定に保った状態で当該トランジスタをオフ状態とすることにより、データを正確に容量素子に保持させることができる。また、このような記憶素子を、CPU、メモリ、及び周辺制御装置のそれぞれに用いることによって、CPUを用いたシステム全体で、電源電圧の供給停止を可能とし、当該システム全体の消費電力を削減することができる。

(もっと読む)

圧電素子、液体吐出ヘッド、超音波モータおよび塵埃除去装置

【課題】圧電定数を向上させた圧電素子、前記圧電素子を用いた液体吐出ヘッド、超音波モータおよび塵埃除去装置を提供する。

【解決手段】一対の電極401,402と、一対の電極401,402に接して設けられた圧電材料403を少なくとも有する圧電素子410であって、圧電材料403はチタン酸バリウムを主成分とする結晶粒404、409の集合体405からなり、集合体405の結晶粒の中の少なくとも電極401と接している結晶粒404が、粒内に転位層407を有する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、半導体装置の歩留まりを向上可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】アンモニア水を用いた湿式エッチングにより、エッチングマスク形成用溝の側面を洗浄することで、下部電極及びエッチングマスクの母材となる下部電極形成用金属膜を成膜する前に、異方性ドライエッチング時にエッチングマスク形成用溝の側面に付着したポリマーを除去し、次いで、エッチングマスク形成用溝に、下部電極形成用金属膜を成膜することでエッチングマスクを形成し、その後、湿式エッチングにより、エッチングマスクをマスクとして、メモリセル領域に形成された第4の層間絶縁膜を選択的に除去する。

(もっと読む)

141 - 160 / 1,312

[ Back to top ]