Fターム[5F083PR05]の内容

Fターム[5F083PR05]に分類される特許

201 - 220 / 1,312

半導体記憶装置およびその製造方法

【課題】隣接セルとの容量を抑制することが可能な半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態の半導体記憶装置は、第1の方向および前記第1の方向と直交する第2の方向に配置される複数のメモリセルトランジスタを備える。前記メモリセルトランジスタのそれぞれは、半導体基板上に形成される第1の絶縁膜と、前記第1の絶縁膜上に形成される浮遊ゲート電極と、前記浮遊ゲート電極上に形成される第2の絶縁膜と、前記第2の絶縁膜上に形成される制御ゲート電極と、を有する。前記第1および第2の方向に隣接する2つの前記メモリセルトランジスタの前記浮遊ゲート電極は、前記隣接する方向の側面に括れた領域を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセル領域の周辺に金属電極を有するアンチフューズを製造歩留り良く形成する。

【解決手段】MOSトランジスタを備えたメモリセルを有するメモリセル領域と、アンチフューズを備えた周辺回路領域とを有する半導体装置において、メモリセルを構成するコンタクトプラグ又はビット配線と同層に形成される周辺回路のコンタクトプラグ又は配線を用いて、アンチフューズの電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域となるSOI構造を有する半導体線条突出部の形状のばらつきを抑制し、トランジスタ特性のばらつきを減少することができる半導体装置を提供する。

【解決手段】半導体基板1の素子分離用の溝に埋込み絶縁膜が埋め込まれてなる素子分離領域2と、素子分離領域2によって区画されてなり、素子分離用の溝を区画する側壁面と半導体基板の1一面とを有し、かつ側壁面には埋込み絶縁膜に向けて突出した半導体線条突出部1aが素子分離用の溝に沿って設けられてなる活性領域Tと、半導体線条突出部1aを残して活性領域Tを分断するように設けられたゲート電極用のゲート溝3と、ゲート溝3の内面に形成されたゲート絶縁膜4と、ゲート溝3に埋め込まれたゲート電極5と、ゲート電極5のゲート長方向両側の活性領域Tにそれぞれ形成され、半導体線条突出部1aによって連結される不純物拡散領域7と、を具備してなることを特徴とする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 セル部のブロック絶縁膜の誘電率を低下させることなく、セル部のブロック絶縁膜を分断するセル間における絶縁膜中の欠陥を低減し、電荷保持特性の劣化を抑制する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】 実施形態の不揮発性半導体記憶装置においては、半導体基板上にトンネル絶縁膜、前記トンネル絶縁膜上に電荷蓄積層、前記電荷蓄積層上にブロック絶縁膜が設けられる。前記半導体基板に設けられた素子分離溝部に埋め込まれ、底面が前記半導体基板と前記トンネル絶縁膜の接する面の高さよりも低く、かつ上面が前記電荷蓄積層および前記ブロック絶縁膜の接する面の高さよりも低い第1の素子分離絶縁膜が設けられる。前記第1の素子分離絶縁膜上に形成され、前記ブロック絶縁膜の側面と接して前記ブロック絶縁膜上面まで突出し、かつSi濃度が前記ブロック絶縁膜よりも高い第2の素子分離絶縁膜が設けられる。

(もっと読む)

半導体装置の製造方法

【課題】マスクの新規な作製技術を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、第1の膜を形成する工程と、第1の膜上方に、第1マスク膜を形成する工程と、第1マスク膜をパターニングする工程と、パターニングされた第1マスク膜の側部にプラズマ処理を行って、側部を変質層に変換する工程と、プラズマ処理の後、第1マスク膜の上部及び側部を覆う第2マスク膜を形成する工程と、第2マスク膜をエッチングして、側部に形成された第2マスク膜を残存させつつ、第1マスク膜上部に形成された第2マスク膜を除去する工程と、第2マスク膜のエッチングの後、変質層を除去する工程と、変質層を除去した後、残った部分の第1マスク膜、及び第2マスク膜をマスクとして、第1の膜をエッチングする工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、微細化された埋め込みビット線を容易に形成可能であると共に、埋め込みビット線の抵抗値を低くすることで高性能化を実現可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板13の主面13aに形成された第1の溝15と、第1の溝15の底面15a、及び第1の溝15の底部15Aに位置するピラー26の側壁面26a,26bに設けられ、側壁面26aを露出する第1の開口部16A、及び側壁面26bを露出する第2の開口部16Bを有した絶縁膜16と、第1の開口部16Aから露出された側壁面26aに形成された半導体基板と反対導電型の下部不純物拡散領域18と、絶縁膜16を介して、第1の溝15の底部15Aに設けられ、第1及び第2の開口部16A,16Bを埋め込むと共に、下部不純物拡散領域18及び側壁面26bと接触し、かつ金属膜よりなる埋め込みビット線21と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】メモリセル領域と周辺回路領域の双方におけるMOSトランジスタの最適化が可能な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、サイドウォールを側壁に有するゲート電極を含むMOSトランジスタを、半導体基板1上のメモリセル領域及び周辺回路領域に備えた半導体装置の製造方法であって、前記サイドウォールを形成した後に、選択エピタキシャル成長法により、前記半導体基板1上面にシリコン層10を形成する工程を備え、前記シリコン層10を形成した後に、少なくとも前記周辺回路領域をマスク20bで覆い、エッチングにより、前記メモリセル領域内のMOSトランジスタTr1のサイドウォール9cを薄化する工程を採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】相変化記録素子のまわりを伝導率の低い真空の空隙部で覆うことで、さらに高い発熱効率を得ることができ、書き換え電流を低減することができる半導体装置を提供する。

【解決手段】半導体基板と、半導体基板の上に形成されたスイッチング素子を含む素子層と、素子層上において、スイッチング素子に接続されたヒータ電極11、ヒータ電極11の熱によって相転移する相変化記録材料層12及び上部電極13が順次積層されてなる相変化記録素子10と、相変化記録素子10の上に積層された層間絶縁膜21bと、素子層と層間絶縁膜21bの間にあってヒータ電極11または相変化記録材料層12のいずれか一方又は両方の周囲に形成された真空の空隙部15と、を具備してなる。

(もっと読む)

半導体装置の製造方法

【課題】微細な配線を高アスペクト比かつ高密度で形成できる、半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜に隣り合う第1配線溝と第2配線溝を形成し、第1配線溝内に第1配線とその上の空間および第2配線溝内に第2配線とその上の空間を設け、等方性エッチングを行って、第1配線溝の幅が拡大されてなる第1マスク溝と第2配線溝の幅が拡大されてなる第2マスク溝を形成し、第1マスク溝及び第2マスク溝にマスク用絶縁材料を充填して、第1マスク溝内の第1マスク絶縁膜と第2マスク溝内の第2マスク絶縁膜を形成し、第1マスク絶縁膜及び第2マスク絶縁膜をマスクとして利用する異方性エッチングを行って、第1配線と第2配線との間を通過し上記層間絶縁膜を貫通するホールを、第1マスク絶縁膜と第2マスク絶縁膜に対して自己整合的に形成し、このホールに導電材料を充填してプラグを形成する、半導体装置の製造方法。

(もっと読む)

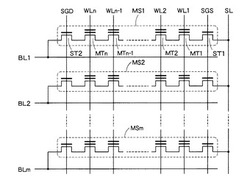

半導体装置、及び半導体装置の駆動方法

【課題】データの書込みにおいて、電源電位を増やすことなく電圧を低減することで低消費電力化が実現された半導体装置を提供する。さらにデータの書込みにおいて、電源電位を増やすことなく選択トランジスタにおけるしきい値落ちの問題が抑制された半導体装置を提供する。

【解決手段】nチャネル型の選択トランジスタのゲートに電気的に接続するワード線に直列にダイオード電気的に接続されたトランジスタを電気的に接続し、さらに当該選択トランジスタのソース又はドレインの一方に電気的に接続するビット線と、ワード線との間に容量素子を設ける、またはビット線とワード線との線間容量を利用する。さらに書込みにおいて、ワード選択のタイミングをビット選択のタイミングよりも早くする。

(もっと読む)

不揮発性半導体記憶装置

【課題】ゲート電極間絶縁膜のリーク電流を抑制し、電気的信頼性を向上した不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板上に行列状に形成された複数のメモリ素子と、同一列方向のメモリ素子に選択的に接続される複数のビット線と、同一行方向のメモリ素子に接続される複数のワード線とを具備し、各メモリ素子は、半導体基板上に順次形成された第1のゲート絶縁膜、電荷蓄積層、第2のゲート絶縁膜、制御電極と、電荷蓄積層の対向する側面に沿って、前記シリコン基板上面に形成された1対の不純物注入層とを具備し、ビット線に垂直な方向に沿った断面における電荷蓄積層の上部コーナー部が曲面を有し、上部コーナー部が前記第1のゲート絶縁膜の上方にある。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】本発明の実施形態は、歩留まりを向上させることができる不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施形態によれば、第1方向にそれぞれ複数の電極間絶縁膜及び電極膜が交互に積層された積層体と、前記積層体を前記第1方向に貫通する半導体ピラーと、前記電極膜のそれぞれと前記半導体ピラーとの間に設けられ、前記第1方向に延びた記憶層と、前記記憶層と前記半導体ピラーとの間に設けられ、前記第1方向に延びた第1絶縁膜と、前記電極膜のそれぞれと前記記憶層との間に設けられ、前記第1方向に延びた第2絶縁膜と、を備え、前記第2絶縁膜は、前記電極膜同士の間に突出したことを特徴とする不揮発性半導体記憶装置が提供される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ソース線と、ビット線と、信号線と、ワード線と、ソース線とビット線との間に、並列に接続されたメモリセル1100と、ソース線及びビット線とスイッチング素子を介して電気的に接続された第1の駆動回路1111と、ソース線とスイッチング素子を介して電気的に接続された第2の駆動回路1112と、信号線と電気的に接続された第3の駆動回路1113と、ワード線と電気的に接続された第4の駆動回路1114と、を有し、メモリセルは、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、容量素子と、を有し、第2のトランジスタは、酸化物半導体材料を含む。

(もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【課題】自己整列リセス・ゲート構造及び形成方法の提供。

【解決手段】最初に,絶縁用のフィールド酸化物領域20を半導体基板10内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】フローティングゲートとコントロールゲートとが積層されたスタック構造のゲート電極を有する半導体装置に関し、隣接メモリセル間やメモリセルとビット線との間における短絡不良を防止しうる半導体装置及びその製造方法を提供する。

【解決手段】トンネルゲート絶縁膜22上に、第1の幅を有する導電膜24、ONO膜28、コントロールゲート40を形成する。コントロールゲート40をマスクとして導電膜24をエッチングしてフローティングゲート26を形成した後、層間絶縁膜80を形成し、第1の方向の幅が第1の幅よりも広いコンタクトホール84を形成する。その後、コンタクトホール84の内壁に、サイドウォールスペーサ88を形成する。

(もっと読む)

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

薄膜製造方法および薄膜素子

【課題】低コストで安定した品質の薄膜を製造すること。

【解決手段】薄膜製造方法は、基板20の第1主面20a上に形成させる薄膜の金属酸化物前駆体溶液12中に、基板を配置する配置工程と、光源13からレーザ光14を照射することにより、基板20の第1主面20a上に薄膜を形成する形成工程と、光源13と同一の光源13からレーザ光14を照射して、基板20の第1主面20aと金属酸化物前駆体溶液12の液面の距離73を計測する工程と、計測結果に基づいて、基板20の高さ方向の位置を調整する工程とを含む。

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】信頼性が高い不揮発性記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る不揮発性記憶装置は、第1配線と、前記第1配線上に設けられ、複数の微小導電体が集合したナノマテリアル集合層と、前記ナノマテリアル集合層上に設けられた第2配線と、を備える。そして、上方から見て、前記ナノマテリアル集合層の少なくとも下部は、前記第2配線の内側に配置されている。

(もっと読む)

半導体装置の製造方法

【課題】側壁接合領域を有した半導体装置の製造方法を提供する。

【解決手段】基板をエッチングしてトレンチを形成するステップと、前記トレンチ底面の基板内に接合領域を形成するステップと、前記トレンチ底面を一定の深さエッチングして側壁接合領域を形成するステップと、前記側壁接合領域に接続するビットラインを形成するステップと、を含む半導体装置の製造方法。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】動作不良の発生を抑制できる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体記憶装置の製造方法が提供される。半導体層11の主面上に、第1方向に沿って延在し電極となる帯状の複数の凸部21を形成する。凸部及び凸部同士の間の溝13tの内面を覆う層間絶縁膜30を形成する。溝内において、層間絶縁膜で囲まれた空間内に第1導電材料を埋め込んで埋め込み導電部40を形成する。埋め込み導電部を第1方向に沿って分断して、埋め込み導電部の第2方向に沿った埋め込み導電部側面40sfを露出させる。埋め込み導電部側面に露出する空洞51中に第2導電材料を埋め込む。第2導電材料の一部を除去する。

(もっと読む)

201 - 220 / 1,312

[ Back to top ]