Fターム[5F083PR05]の内容

Fターム[5F083PR05]に分類される特許

121 - 140 / 1,312

半導体装置

【課題】隣接するメモリセル間およびメモリセルと選択トランジスタとの間に間隙を設け

つつ、選択トランジスタおよび周辺回路における短絡を抑制する。

【解決手段】本実施形態による半導体記憶装置は、ゲートを有する複数のメモリセルが直

列に接続されたメモリセルストリングを備える。選択トランジスタが、メモリセルストリ

ングの一端にある端部メモリセルに接続されている。側壁膜が、端部メモリセルと選択ト

ランジスタとの間において、端部メモリセルのゲートの側面および選択トランジスタのゲ

ートの側面を被覆する。端部メモリセルの側壁膜と選択トランジスタの側壁膜との間に空

隙がある。

(もっと読む)

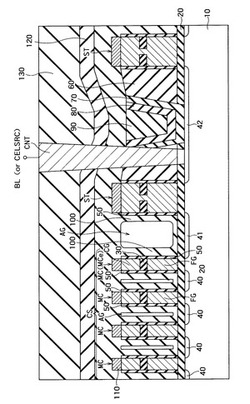

不揮発性半導体記憶装置とその製造方法

【課題】メモリセルが3次元的に積層された不揮発性半導体記憶装置で、メモリセルの投影面積を小さくすることができ、従来の平面型のフローティングゲート構造と類似の構造の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、シート状のチャネル半導体膜111の高さ方向に複数のメモリセルMCを有するメモリストリングが基板上にほぼ垂直に配置される。フローティングゲート電極膜109は、第2の方向に延在し、トンネル誘電体膜110を介してチャネル半導体膜111の第1の主面上に形成される。制御ゲート電極膜103は、第1の方向に延在する共通接続部1031と、共通接続部1031から第2の方向に突出し、フローティングゲート電極膜109の上部または下部に電極間絶縁膜108を介してメモリセルMCごとに設けられる電極構成部1032と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みビットライン型不揮発メモリの微細化に適した製造方法を提供し、かつコンタクトの位置ずれに起因するビットライン間ショートを生じ難い構造を提供する。

【解決手段】導電体膜が埋め込まれたシャロートレンチ溝内にビットライン拡散層を設けてSONOS構造セルとする。これにより、ビットライン拡散層の半導体基板主面上での面積を大きくせずにビットライン拡散層の抵抗を低くすることができ、セル面積を増大させることなく安定した電気的特性の半導体記憶装置が得られる。また、Si3N4のサイドウォールを設けてイオン注入することでビットラインを形成する。これにより、メモリセルの微細化が可能となる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜の不要な部分を除去するときのエッチングとして、ウェットエッチングを用いても、浮遊ゲート絶縁膜がサイドエッチングされることを抑制する。

【解決手段】選択ゲート絶縁膜172は浮遊ゲート絶縁膜110の隣に位置している。選択ゲート電極170は選択ゲート絶縁膜172上に位置しており、側面が第2絶縁膜152を介して浮遊ゲート電極120の第1側面に接続している。消去ゲート電極180は、第3絶縁膜160を介して浮遊ゲート電極120に接続している。第2絶縁膜152の下端は、浮遊ゲート絶縁膜110の上面よりも、半導体基板100の表面の近くに位置している。第2絶縁膜152の下端から半導体基板100の表面までの距離は、選択ゲート絶縁膜172の厚さよりも大きい。

(もっと読む)

記憶回路、記憶装置、信号処理回路

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶回路の提供、消費電力の低減可能な信号処理回路を提供する。

【解決手段】記憶回路は、トランジスタと、容量素子と、第1の演算回路と、第2の演算回路と、第3の演算回路と、スイッチと、を有し、第1の演算回路の出力端子は、第2の演算回路の入力端子と電気的に接続され、第2の演算回路の入力端子は、スイッチを介して第3の演算回路の出力端子と電気的に接続され、第2の演算回路の出力端子は、第1の演算回路の入力端子と電気的に接続され、第1の演算回路の入力端子は、トランジスタのソース及びドレインの一方と電気的に接続され、トランジスタのソース及びドレインの他方は、容量素子の一対の電極のうちの一方、及び第3の演算回路の入力端子と電気的に接続され、トランジスタのチャネルは酸化物半導体層に形成される。

(もっと読む)

半導体素子の形成方法

【課題】相互接続領域の具現が困難なパッドレイアウトを具現化し、オーバレイマージンを増大できる半導体素子の形成方法を提供する。

【解決手段】半導体基板に被食刻層、第1のハードマスク物質層、第1の分割パターン物質層及び第2のハードマスク物質層を形成して選択食刻し第2のハードマスクパターンを形成し、これをマスクとし第1の分割パターン物質層を食刻し第1の分割パターンを形成する。第1のハードマスク物質層の上部にスペーサ物質層及び第2の分割パターン物質層を形成し、第1の分割パターンが現われるまでスペーサ物質層及び第2の分割パターン物質層を部分食刻しスペーサ物質層を露出させ、複数の第1の分割パターン間に第2の分割パターンを形成し、第1、第2の分割パターンをマスクとしスペーサ物質層及び第1のハードマスク物質層を食刻し第1のハードマスクパターンを形成し、これをマスクとし被食刻層を食刻し微細パターンを形成する。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】金属酸化物中の酸素欠損を低減し、電気的特性の安定した半導体装置を提供することを目的の一とする。

【解決手段】ゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の金属酸化物膜と、第1の金属酸化物膜に接して設けられたソース電極及びドレイン電極と、ソース電極及びドレイン電極上に設けられたパッシベーション膜と、を有し、パッシベーション膜は、第1の絶縁膜と、第2の金属酸化物膜と、第2の絶縁膜とが順に積層された半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】 セレクトゲート部におけるゲート閾値電圧が安定した半導体装置の製造方法を提供する。

【解決手段】 実施形態に係る半導体装置の製造方法では、メモリセル部及びセレクトゲート部が形成される。半導体基板上にトンネル絶縁膜が形成され、前記トンネル絶縁膜上に電荷蓄積層が形成される。前記電荷蓄積層、前記トンネル絶縁膜、及び前記半導体基板のエッチングにより素子分離溝部が形成され、前記電荷蓄積層の側面に接するように前記素子分離溝部に素子分離絶縁膜が埋め込まれる。前記電荷蓄積層及び前記素子分離絶縁膜上に電極間絶縁膜が形成され、前記セレクトゲート部において、前記電極間絶縁膜がエッチングされる。前記電極間絶縁膜を覆い、前記電荷蓄積層に接続するシリコン膜が形成され、前記シリコン膜上に金属膜が形成される。熱処理により、前記セレクトゲート部において、前記トンネル絶縁膜に接する前記電荷蓄積層がシリサイド化される。

(もっと読む)

相変化メモリ装置

【課題】本発明は、相変化記録層に対する加熱を効率良く行うことができ、書き込み電流の低減を可能とする相変化メモリ装置を提供する。

【解決手段】ヒータプラグと、前記ヒータプラグと接して設けられた相変化記録層とを含んで構成される記憶素子を備え、前記ヒータプラグ及び前記相変化記録層のうち少なくとも一方の内部に空隙が設けられていることを特徴とする。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】従来のMONOS型の不揮発性半導体記憶装置の製造方法では、トップ絶縁膜のエッチング加工にウェットエッチングを用いるため、サイドエッチングが侵攻してしまうという問題があった。これにより電荷蓄積層とゲート電極との間の絶縁性が損なわれ、電気的リークが発生し、消去特性などの電気特性が低下していた。

【解決手段】メモリゲート絶縁膜の形成前に保護絶縁膜を形成し、この保護絶縁膜によりメモリゲート絶縁膜のサイドエッチングを防止する製造方法とすることで、電荷蓄積層とゲート電極との間の絶縁性が向上する。そして、この保護絶縁膜を不揮発性半導体記憶装置の製造後も側壁保護膜として残してもよい。そうすると不揮発性半導体記憶装置の完成後に、他の半導体素子を形成するためのウェットエッチング工程があったとしても、メモリゲート絶縁膜がサイドエッチングされることはない。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、酸化シリコン膜上に、酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている非晶質酸化物半導体層を形成し、該非晶質酸化物半導体層上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体層の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体層を形成する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】従来のMONOS型の不揮発性半導体記憶装置の製造方法では、トップ絶縁膜のエッチング加工にウェットエッチングを用いるため、サイドエッチングが侵攻してしまうという問題があった。これにより電荷蓄積層とゲート電極との間の絶縁性が損なわれ、電気的リークが発生し、消去特性などの電気特性が低下していた。

【解決手段】本発明の不揮発性半導体記憶装置の製造方法は、2つの犠牲膜を用いることにより、トップ絶縁膜と側壁保護膜とを同時に形成するエリアを作り出し、酸化処理によってそれらを形成する。このような製造方法とすることで、メモリゲート絶縁膜のサイドエッチングが発生することはない。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造工程数の削減が可能な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1、第2積層体、第1、第2半導体ピラー、第1、第2メモリ膜、接続部及び分断部を備えた不揮発性半導体記憶装置が提供される。第1、第2積層体は、第1軸に沿って積層された複数の第1、第2電極膜と、第1、第2電極膜間に設けられた第1、第2電極間絶縁膜と、をそれぞれ含む。第1、第2半導体ピラーは第1、第2積層体を第1軸に沿って貫通する。第2積層体は、第1積層体と並置される。接続部は第1、第2半導体ピラーを接続する。第1メモリ膜は、第1、第2電極膜と、第1、第2半導体ピラーとの間に設けられる。分断部は、第1、第2半導体ピラー間で第1、第2電極膜を分断し、接続部に接し、第1メモリ膜に用いられる材料を含む積層膜を含む。

(もっと読む)

半導体装置の製造方法

【課題】実施形態によれば、メモリストリングの下端を連結する構造を少ない工程数で形成することができる半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、シリコンを含む下地層にマスクを用いて選択的に不純物を注入し、下地層に、ホウ素を含むホウ素添加領域と、ホウ素添加領域よりもホウ素濃度が低い被エッチング領域とを形成する工程を有する。また、複数層の電極層を含む積層体に、被エッチング領域に達する一対のホールを形成する工程を有する。また、エッチング液を用いて被エッチング領域をホールを通じて除去し、下地層に、一対のホールのそれぞれの下端とつながった凹部を形成する工程を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】3次元に積層されたメモリセルトランジスタにおける誤動作を防止する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20と、半導体基板の上方に形成された第1導電層40と、第1導電層の上方に順に積層された第2導電層43、電極間絶縁膜53’、および第3導電層43と、一対の貫通ホール49の内面上、および一対の貫通ホールの下端を連結させる連結ホール50の内面上に形成されたブロック絶縁膜53と、電荷蓄積層54と、トンネル絶縁膜55と、半導体層SPと、一対の貫通ホールの間に位置し、第2導電層、電極間絶縁膜、および第3導電層を分断するスリット46内に埋め込まれた絶縁材59と、第2導電層および第3導電層の表面上に形成されたシリサイド層58と、を具備し、スリットの内面に沿った第2導電層と第3導電層との間の距離は、積層方向に沿った第2導電層と第3導電層との距離よりも大きい。

(もっと読む)

圧電素子の製造方法、圧電素子、液体噴射ヘッド及び液体噴射装置

【課題】鉛を含有せず、かつ膜剥がれ等の問題がなく、圧電特性の劣化のない圧電素子の製造方法、液体噴射ヘッド及び圧電素子を提供する。

【解決手段】酸化ジルコニウムからなる絶縁体膜55上にジルコニウムからなる密着層56を形成する工程と、密着層56上に第1電極60を形成する工程と、第1電極60上にビスマスを含む複合酸化物からなる圧電体層70を形成する工程と、圧電体層70上に第2電極80を形成する工程と、を具備する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するものである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】実施形態によれば、十分な消去速度が得られる半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、第1の積層体と、メモリ膜と、第1のチャネルボディと、第2の積層体と、ゲート絶縁膜と、第2のチャネルボディとを備えている。前記選択ゲートの側面と前記第2の絶縁層との間に段差部が形成されている。前記段差部を被覆する部分の前記第2のチャネルボディの膜厚は、前記第2の絶縁層間に設けられた部分の膜厚よりも厚い。

(もっと読む)

121 - 140 / 1,312

[ Back to top ]