Fターム[5F083PR05]の内容

Fターム[5F083PR05]に分類される特許

81 - 100 / 1,312

エッチング方法及びこれに用いられるシリコンエッチング液

【課題】少なくとも無機アルカリ化合物、ヒドロキシルアミン化合物、及びアニオン性化合物を含むシリコンエッチング液を、多結晶シリコン膜またはアモルファスシリコン膜に適用して、該膜の少なくとも一部を除去するエッチング方法。

【解決手段】アモルファスシリコン又は多結晶シリコン膜を的確かつ効率よく除去して半導体基板に凹凸を形成するに当たり、ウエハの中央部から端部に至るまでバランスよくエッチングするシリコンエッチング液及びこれを用いたエッチング方法を提供する。

(もっと読む)

半導体装置

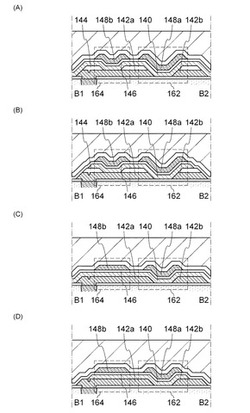

【課題】電力供給がない状況で記憶保持が可能で、書き込み回数に制限が無い、新たな半導体装置を提供する。

【解決手段】チャネル領域と第1のゲート絶縁層と第1のゲート電極と第1のソース及びドレイン電極とを有する第1のトランジスタと、酸化物半導体層140と第2のソース電極142a及び第2のドレイン電極142bと第2のゲート絶縁層146と第2のゲート電極148aとを有する第2のトランジスタ162と、第2のソース電極142aまたは第2のドレイン電極142bの一方と第2のゲート絶縁層146と第2のゲート絶縁層146上に第2のソース電極142a又は第2のドレイン電極142bの一方と重なるように設けられた第3の電極148bとを有する容量素子164と、を有し、第1のゲート電極と第2のソース電極142a又は第2のドレイン電極142bの一方とは接続され、第3の電極148bは酸化物半導体層140と重なる領域を有する。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

キャパシタ構造の形成方法及びこれに用いられるシリコンエッチング液

【課題】半導体基板に凹凸形状をなすよう、アモルファスシリコン又は多結晶シリコンを的確かつ効率よく除去することができ、しかもそのエッチングが行われる条件下において長時間活性が維持されるシリコンエッチング液及びこれを用いたキャパシタ構造の形成方法を提供する。

【解決手段】アンモニアと、ヒドロキシルアミン化合物、塩基性有機化合物、及び金属含有塩基性化合物からなる群から選ばれる少なくとも1つの特定塩基性化合物とを組み合わせて含むシリコンエッチング液を、多結晶シリコン膜またはアモルファスシリコン膜6に適用して、該多結晶シリコン膜またはアモルファスシリコン膜の少なくとも一部を除去することにより、キャパシタとなる凹凸形状を形成するキャパシタ構造10の形成方法。

(もっと読む)

記憶回路

【課題】短時間の電源停止により消費電力を抑えることができ、電源再開時において誤動作を引き起こすことなく初期化することのできる信号処理装置の記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性記憶部に記憶していたデータ信号を、不揮発性記憶部に保持する。不揮発性記憶部では、オフ電流が極めて小さいトランジスタを用いることによって、容量素子に保持されたデータ信号は長期間にわたり保持する。こうして、不揮発性記憶部は電源の供給が停止した間も論理状態を保持する。また電源停止時に容量素子で保持されたデータ信号は、電源再開時にはリセット回路を導通状態とすることで、誤動作を引き起こすことのない電位にする。

(もっと読む)

半導体装置

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】第1のトランジスタ及び第2のトランジスタを有するメモリセルを有し、第1のトランジスタは第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタは酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される不揮発性メモリによって解決する。

(もっと読む)

半導体装置の製造方法

【課題】DHF処理後に実施されるHPM処理またはAPM処理を、良好に行うことができる半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、槽内に水を導入して、槽内から希フッ酸を排出する工程と、槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、槽内に、H2O2と、上記水よりも温度の高い温水とを導入する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造において基板の金属汚染を抑える。

【解決手段】半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、前記半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性半導体装置の高集積化を図ることのできる技術を提供する。

【解決手段】スイッチ用nMIS(Qs)のスイッチゲート電極SGと、スイッチ用nMIS(Qs)にワード線に対して交差する方向に沿って隣接するメモリ用nMIS(Qm)のメモリゲート電極MGとの間に、スイッチ用nMIS(Qs)のソース/ドレイン領域SDHとして機能し、同時にメモリ用nMIS(Qm)のドレイン領域Dとして機能する半導体領域を形成し、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)側のソース/ドレイン領域SDHを構成する半導体領域の形状と、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)と反対側(ビット線側)のソース/ドレイン領域SDLを構成する半導体領域の形状とを非対称とする。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

記憶回路、電子機器

【課題】新たな構成の不揮発性の記憶回路を提供する。

【解決手段】第1の記憶回路と、第2の記憶回路と、第1のスイッチと、第2のスイッチと、位相反転回路と、を有し、第1の記憶回路は、酸化物半導体膜により形成された第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、を有する。酸化物半導体膜により形成された第1のトランジスタと、容量素子と、を用い不揮発性の記憶回路を構成する。また、記憶回路に接続する電源線、及び信号線を少なくし、当該記憶回路に用いるトランジスタ数を減少させることで、回路規模の小さい不揮発性の記憶回路を実現することができる。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

記憶装置、及び当該記憶装置を用いた半導体装置

【課題】DRAMよりも書き込み、読み出しなどの動作速度が高く、SRAMよりもメモリセルあたりの半導体素子の数を減らすことができる記憶装置。

【解決手段】制御装置と、演算装置と、緩衝記憶装置とを有し、緩衝記憶装置は、主記憶装置から、或いは演算装置から送られてきたデータを、制御装置からの命令に従って記憶し、緩衝記憶装置は複数のメモリセルを有し、メモリセルは、チャネル形成領域に酸化物半導体を含むトランジスタと、トランジスタを介してデータの値に従った量の電荷が供給される記憶素子とを有する。さらに、緩衝記憶装置が有する複数のメモリセルは、バリッドビットに対応するメモリセルが、データフィールドに対応するメモリセルよりも、そのデータの保持時間が短い。

(もっと読む)

ラッチ回路及び半導体装置

【課題】新規のラッチ回路を提供すること。

【解決手段】ラッチ回路は、酸化物半導体(OS)によってチャネル領域が形成されるトランジスタ10を有し、出力端子(Q端子)並びにトランジスタ10のソース及びドレインの一方に電気的に接続され、且つトランジスタ10がオフ状態となることによって浮遊状態となるノード11においてデータを保持する。なお、当該酸化物半導体は、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い。このような酸化物半導体によってトランジスタのチャネル領域が形成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。

(もっと読む)

記憶素子、信号処理回路

【課題】新たな構成の不揮発性の記憶素子、それを用いた信号処理回路を提供する。

【解決手段】第1の回路と第2の回路とを有し、第1の回路は第1のトランジスタと第2のトランジスタとを有し、第2の回路は第3のトランジスタと第4のトランジスタとを有する。第1の信号に対応する信号電位は、オン状態とした第1のトランジスタを介して第2のトランジスタのゲートに入力され、第2の信号に対応する信号電位は、オン状態とした第3のトランジスタを介して第4のトランジスタのゲートに入力される。その後、第1のトランジスタ及び第3のトランジスタをオフ状態とする。第2のトランジスタの状態と第4のトランジスタの状態との両方を用いて、第1の信号を読み出す。第1のトランジスタ及び第3のトランジスタは、チャネルが酸化物半導体層に形成されるトランジスタとする。

(もっと読む)

エッチング方法及びこれに用いられるエッチング液、これを用いた半導体素子の製造方法

【課題】Ti等の特定の金属材料からなる層を優先的に溶解する選択的なウエットエッチングを可能とし、しかもエッチング・アッシング等により生じる残渣をも効果的に洗浄除去することができるエッチング方法及びこれに用いるエッチング液、これを用いた半導体素子の製造方法を提供する。

【解決手段】Ti、Mo、Ag、V、Al、及びGeの少なくとも1種を含む金属材料層と、SiC、SiOC、及びSiONの少なくとも1種を含むケイ素化合物層とを有する半導体基板にエッチング液を適用し、前記金属材料層を選択的に溶解するエッチング方法であって、前記エッチング液として、フッ素化合物と、炭素数が8以上の疎水性基と1つ以上の親水性基とを有する特定有機化合物とを含み、pHを3〜7に調整したものを使用するエッチング方法。

(もっと読む)

半導体装置およびその製造方法

【課題】信号速度の遅延を防止することができる半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、基板上に成膜された第1の絶縁膜と、配線と、第2の絶縁膜とを持つ。前記配線は、前記第1の絶縁膜に互いに平行に所定間隔で形成されたトレンチを埋め込むように金属で形成される。前記第2の絶縁膜は、前記第1の絶縁膜と前記配線とを覆うように前記第1の絶縁膜よりも誘電率の高い材料で成膜される。前記配線間の領域における前記第2の絶縁膜の下面は、前記配線の上面の周縁を互いに結ぶ面に対して上方へ離隔している。

(もっと読む)

信号処理装置

【課題】消費電力を抑えることができる信号処理装置を提供する。

【解決手段】信号処理装置が有する記憶回路に、酸化物半導体にチャネルが形成されるトランジスタを適用することで、電力の供給を停止している間もデータの保持(記憶)を可能とする。記憶回路に記憶されているデータは、信号処理装置への電力の供給を停止している間も、破壊すること無く読み出すことができる。

(もっと読む)

半導体装置および半導体装置を用いた記憶装置

【課題】データを一時的に待避させるための周辺回路を用いることなくオフ状態とすることが可能であり、かつ、装置の電源がオフ状態になっても記憶されたデータが消失しない、消費電力の低減された半導体装置および、当該半導体装置を用いた記憶装置を提供する。

【解決手段】半導体装置の保持回路に、オフ電流を十分に小さくすることができる酸化物半導体材料を用いて半導体層(少なくともチャネル形成領域)を形成したトランジスタを用いる。また、保持回路に蓄えられた記憶データと、外部から入力される参照データの比較処理を行う必要がない比較回路を、強制的に非活性状態とするスイッチング素子を備える構成とする。

(もっと読む)

81 - 100 / 1,312

[ Back to top ]