Fターム[5F083PR05]の内容

Fターム[5F083PR05]に分類される特許

101 - 120 / 1,312

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】メモリ・ロジック混載型の半導体装置の高性能化を可能にする技術を提供する。

【解決手段】ストッパ膜17は、ストッパ膜13及び層間絶縁膜14から成る絶縁層上に形成されている。コンタクトプラグ16,65,66のそれぞれは、その上面がストッパ膜17から露出するように、ソース・ドレイン領域9,59とそれぞれ電気的に接続されてストッパ膜13、層間絶縁膜14及びストッパ膜17に設けられている。絶縁層20は、ストッパ膜17及びコンタクトプラグ16,65,66の上に設けられている。キャパシタ82の下部電極は、メモリ形成領域において、コンタクトプラグ66の上面とストッパ膜17の上面とに接触するように絶縁層20内に設けられている。

(もっと読む)

記憶装置、及び半導体装置

【課題】プロセスを複雑化させることなく、単位面積あたりの記憶容量を高めることができる記憶装置を提案する。

【解決手段】複数のメモリセルと、複数のワード線と、複数のビット線とを有し、複数のメモリセルは、スイッチング素子と、第1の電極及び第2の電極を有する容量素子と、をそれぞれ有し、複数のメモリセルの少なくとも1つにおいて、複数のワード線のうち一のワード線に与えられる電位に従って、スイッチング素子が複数のビット線のうち一のビット線と第1の電極の接続を制御し、なおかつ、第2の電極が複数のワード線のうち一のワード線とは異なる一のワード線に接続されている記憶装置。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

半導体装置の製造方法、並びにデータ処理システム

【課題】チャネル領域を拡大することが可能な半導体装置の製造方法を提供する。

【解決手段】素子分離用の溝部3を形成した後、素子分離絶縁膜4として、当該溝部3に埋め込まれた状態で基板2の面上を覆うシリコン酸化膜26,31を形成する工程と、シリコン酸化膜26,31上に少なくとも埋め込みゲート用の溝部10を形成する位置に開口部を有するマスクパターンを形成する工程と、マスクパターンの開口部を通してシリコン酸化膜31を異方性エッチングにより選択的に除去することによって、当該シリコン酸化膜31に第1の溝部9と同じ幅及び深さとなる第2の溝部10を形成する工程と、第2の溝部10の底面及び側面に位置するシリコン酸化膜26,31を等方性エッチングにより選択的に除去することによって、当該第2の溝部10を活性領域6に形成される第1の溝部9よりも深く、且つ、第1の溝部9よりも大きい幅とする工程とを含む。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールに埋め込まれたコンタクトプラグが埋め込み配線と非導通になることを防止した半導体装置及びその製造方法を提供する。

【解決手段】ゲート絶縁膜を介してピラー部9の側面と対向する位置において幅広となる形状を有する第1の溝部8を形成し、この第1の溝部8の幅広となる部分8bに埋め込まれた状態で第1の埋め込み配線15を形成し、複数のピラー部9が並ぶ領域よりも外側の領域において、第1の溝部8の間に位置すると共に、第1の溝部8の幅広となる部分8bに埋め込まれた第1の埋め込み配線15に至る深さで第1のコンタクトホール25を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極用溝18の底部18cから活性領域の一部が突き出すように形成されたフィン部15と、ゲート電極用溝18及びフィン部15の表面を覆うゲート絶縁膜21と、ゲート電極用溝18の下部に埋め込まれ、ゲート絶縁膜21を介してフィン部15を跨ぐように形成されたゲート電極22と、第1の不純物拡散領域28と、第2の不純物拡散領域29と、フィン部15の表面に設けられた準位形成領域30と、を備える半導体装置10を選択する。

(もっと読む)

ルチル結晶構造を備えた酸化チタン膜の製造方法

【課題】高温のアニールを必要とせずに、誘電率の高いルチル結晶構造の酸化チタン膜を形成する。

【解決手段】非晶質の酸化ジルコニウム膜上に、チタンプリカーサとしてメチルシクロペンタジエニルトリスジメチルアミノチタンを用いてALD法により非晶質の酸化チタン膜を形成し、300℃以上の温度でアニールして結晶化することでルチル結晶構造を有する酸化チタン膜が得られる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

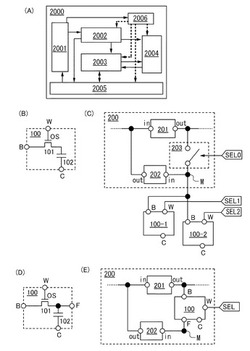

半導体記憶装置

【課題】不揮発性の記憶装置を有するCAMとする際に、メモリセルの低消費電力化を図ることのできる半導体記憶装置を提供することを課題の一とする。また、データの書き込みを繰り返し行う際の劣化をなくすことができる半導体記憶装置を提供することを課題の一とする。また、メモリセルの高密度化が可能な不揮発性の記憶装置を提供する。

【解決手段】酸化物半導体を半導体層に有する第1のトランジスタ及び当該第1のトランジスタをオフ状態とすることで書き込んだデータに対応する電位を保持できる容量素子を有するメモリ回路と、書き込んだ電位を参照するための参照回路を有し、参照回路を構成する第2のトランジスタの導通状態を検出することで、整合するデータのアドレスを取得し、高速な検索機能を可能にした半導体記憶装置である。

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】メモリセルが3次元的に積層された不揮発性半導体記憶装置を工程数の増大を抑制しながら製造可能な不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】半導体基板101上にスペーサ膜104とチャネル半導体膜103とを交互に複数層積層させた積層構造を形成し、積層構造に第1の方向に延在するトレンチを形成する。ついで、トレンチからチャネル半導体膜103を第2の方向にリセスして空隙を形成し、空隙内のチャネル半導体膜103上にトンネル誘電体膜108を形成し、フローティングゲート電極膜109を埋め込む。その後、第1の方向に隣接するメモリセル間でフローティングゲート電極膜109が分離され、チャネル半導体膜103が分離されないように、積層構造を第1の方向に所定の間隔で分割する。また、第2の方向に隣接するメモリセル間でチャネル半導体膜103が分離されるように、積層構造を第2の方向に所定の間隔で分割する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させる。

【解決手段】シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させ、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成し、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。

(もっと読む)

半導体デバイス及びその製造方法

【課題】エッチング選択比の高い非晶質炭素膜を用いたシリンダ型キャパシタを有する半導体デバイスでは、非晶質炭素膜を除去する際に、キャパシタの下部電極に変形が生じやすい。

【解決手段】非晶質炭素膜及び層間絶縁膜をメモリセル領域及び周辺回路領域にそれぞれ形成し、非晶質炭素膜及び層間絶縁膜上に絶縁膜を形成し、非晶質炭素膜上のキャパシタに対応した部分における絶縁膜を除去して、キャパシタの下部電極を両側から支持すると共に、メモリセル領域から周辺回路領域まで連続的に覆う絶縁膜パターンを形成する。続いて、非晶質炭素膜を用いたキャパシタを形成した後、絶縁膜パターン下部の非晶質炭素膜を除去する。

(もっと読む)

半導体装置の製造方法

【課題】 CMOS型半導体装置におけるデュアルゲート構造のゲート電極をエッチングにより形成する時に、局所的なゲート絶縁膜の「突き抜け」やゲート電極サイドエッチ等の欠陥が発生することを防止できる製造方法を提供する。

【解決手段】 ゲート絶縁膜5を介して半導体基板1上に形成されたシリコン膜等の、実質的に不純物を含まない半導体膜6を選択的にエッチングしてゲート電極7を形成する。隣接するゲート電極7間の領域をレジスト等の絶縁膜9で埋め込む。さらに例えば所定のゲート電極7が形成された領域を覆うマスク層10を形成し、絶縁膜9とマスク層10とをマスクとして、マスク層10で覆われないゲート電極7にイオン注入等の手段により所定導電型の不純物を導入する。同様の方法を用いてマスク層10で覆われていたゲート電極7に異なる導電型の不純物を導入する。

(もっと読む)

101 - 120 / 1,312

[ Back to top ]