Fターム[5F083PR06]の内容

Fターム[5F083PR06]に分類される特許

101 - 120 / 887

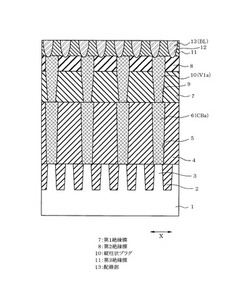

半導体装置およびその製造方法

【課題】配線部を通じた信号伝搬速度を向上できるようにした半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板上に形成された第1絶縁膜と、前記第1絶縁膜上に形成された、前記第1絶縁膜より比誘電率が高い第2絶縁膜と、前記第2絶縁膜と隣接する側面が順テーパ形状を有し、前記第1絶縁膜および前記第2絶縁膜を貫通して形成された複数の縦柱状プラグと、前記第2絶縁膜上に形成された、前記第2絶縁膜よりも比誘電率が低い第3絶縁膜と、前記複数の縦柱状プラグの上部に到達するように前記第3絶縁膜に形成された複数の溝と、前記複数の溝内にそれぞれ形成され、前記複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部と、を備える。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】半導体記憶装置におけるデータ保持のためのリフレッシュ動作の回数を低減し、消費電力の小さい半導体記憶装置を提供する。また、三次元の形状を適用することで、集積度を高めても短チャネル効果の影響が低減され、かつ従来に比べてフォトリソグラフィ工程数の増加を抑えた半導体記憶装置を提供する。

【解決手段】溝部の設けられた絶縁膜103と、溝部を挟んで離間した一対の電極116と、溝部の側面および底面と接し、溝部の深さよりも厚さの薄い、一対の電極116と接する酸化物半導体膜106と、酸化物半導体膜106を覆うゲート絶縁膜112と、ゲート絶縁膜112を介して酸化物半導体膜106と重畳して設けられたゲート電極112と、を有するトランジスタ150と、キャパシタ160と、を有する半導体記憶装置である。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量コンタクトプラグと半導体基板の活性領域との間の重ねマージンを十分に確保して、低抵抗且つ接続信頼性の高い半導体装置を提供する。

【解決手段】埋め込みゲート電極19A及びキャップ絶縁膜20Aと、活性領域1Aの上面に設けられたビットコンタクト27A及びビット線27と、半導体基板1上に設けられた絶縁層32,40と、第1容量コンタクトプラグ39Aと、を備え、第1容量コンタクトプラグ39Aは、柱状部39aとこの柱状部39aの下方に設けられた板状部39bとを有し、板状部39bの底面と、素子分離領域及びキャップ絶縁膜20Aによって区画された活性領域1Aの表面1a,1cとが全面で接触するように設けられていることを特徴とする半導体装置を選択する。

(もっと読む)

半導体装置の製造方法

【課題】下部電極の相変化膜接触面と相変化膜の下面との間で位置ずれが発生することを防止する。

【解決手段】本発明による半導体装置1の製造方法は、導電材料を成膜することにより、スルーホール10a内に下部電極HEを形成する工程と、層間絶縁膜10の上面が露出する程度まで表面を平坦化する工程と、下部電極HEの上面の一部を覆うマスク膜をマスクとして用いて下部電極HEをエッチングすることにより、層間絶縁膜10の上面に絶縁膜埋込用溝部を設け、その内部に絶縁膜13aを埋め込む工程と、層間絶縁膜14を形成して表面を平坦化することによりマスク膜の上面を露出させる工程と、マスク膜を除去することにより、層間絶縁膜14の上面に開口部14aを設ける工程と、開口部14a内に相変化材料を成膜することにより、開口部14a内に露出した下部電極HEの上面を相変化膜GSTで覆う工程とを備える。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲート電極および当該選択ゲート電極に隣接する他のゲート電極間の間隔を所望の距離に調整できるようにした不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】複数本のラインパターンのうち選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてマスクした条件にて複数本のラインパターンの側壁面をスリミングし、選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてパターン間膜を埋込むと共にスリミングされたラインパターンの側壁面に沿ってパターン間膜を形成し、選択ゲート電極の形成領域のラインパターンをマスクした条件にて当該ラインパターン以外のラインパターンを除去しマスクされたラインパターンを残留させ、パターン間膜および残留したラインパターンをマスクとして第1膜を異方性エッチングし、第1膜をマスクとして導電膜をエッチングする不揮発性半導体記憶装置の製造方法を提供する。

(もっと読む)

メモリセルキャパシタ構造におけるメモリセルキャパシタプレートの形成方法

【課題】酸素にさらされても絶縁膜を形成しない材料からメモリセルキャパシタプレートを製造するための形成方法を提供する。

【解決手段】メモリセルキャパシタプレートの形成方法は、犠牲層を堆積する工程と、その犠牲層内に開口部を形成する工程とを含む。続いて、酸素にさらされても相当の導電性を維持する導電性料を含む電極材料層702を、犠牲層の上面に堆積し、開口部の少なくとも一部を充填する。次に、電極材料層702の一部を少なくとも犠牲層の上面と同じ略同じ高さにまで除去することによりメモリセルキャパシタプレートの上面を画定し、その後、犠牲層を除去する。

(もっと読む)

記憶装置およびその製造方法

【課題】メモリセルの構造を最適化することにより、更なる微細化を可能にする記憶装置を提供する。

【解決手段】複数の第1の電極配線と、第1の電極配線と交差する複数の第2の電極配線と、1本の第2の電極配線と、互いに隣接する2本の第1の電極配線との間に形成される1個のビアプラグであって、前記第1の電極配線に対向する底面の、第1の電極配線の伸長方向に垂直な方向の最大径が、第1の電極配線幅の2倍と第1の電極配線間の幅を加えた長さよりも小さいビアプラグと、ビアプラグと2本の第1の電極配線の一方との間に形成される第1の記憶素子と、ビアプラグと2本の第1の電極配線の他方との間に形成される第2の記憶素子とを有する記憶装置。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

半導体メモリ素子及びその製造方法

【課題】垂直型トランジスタを形成する過程において、ゲートと接触する活性領域の面積を増加させてゲートの接触抵抗特性を改善し、チャネル幅を増加させる半導体メモリ素子及びその製造方法を提供する。

【解決手段】第1の方向に延長するように形成された下部ピラーと、下部ピラー上に第1の方向と垂直な第2の方向に突出するように形成された上部ピラー290と、下部ピラーの一側壁に配置された埋め込みビットライン接合領域265と、トレンチを一部埋め込む埋め込みビットライン280と、エッチング停止膜285a上に形成された少なくとも上部ピラーの外周側面の一部を露出するようにリセスされた第1の層間絶縁膜290と、第1の層間絶縁膜上に形成された第2の層間絶縁膜295と、側面の一部が露出した上部ピラーの外周側面を覆いつつ、埋め込みビットラインと相互交差するゲート320aとを備えるように形成される。

(もっと読む)

不揮発性記憶素子および不揮発性記憶装置

【課題】電極と抵抗変化層の界面に小さな突起を形成することなく、低電圧での初期化が可能な不揮発性記憶素子を提供する。

【解決手段】下部電極105と上部電極107との間に介在され、両電極間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層116を備える。抵抗変化層116は、第1の抵抗変化層1161と第2の抵抗変化層1162との少なくとも2層から構成され、第1の抵抗変化層1161は第1の遷移金属酸化物116bから構成され、第2の抵抗変化層1162は、第2の遷移金属酸化物116aと第3の遷移金属酸化物116cとから構成され、第2の遷移金属酸化物116aの酸素不足度は第1の遷移金属酸化物116bの酸素不足度及び第3の遷移金属酸化物116cの酸素不足度のいずれよりも高く、第2の遷移金属酸化物116a及び第3の遷移金属酸化物116cは、第1の抵抗変化層1161と接している。

(もっと読む)

半導体メモリ装置

【課題】高度に集積化したDRAMを提供する。

【解決手段】基板201上にメモリセルアレイを駆動するための回路202を形成し、その上にビット線205を形成し、ビット線205上に半導体領域208とワード線210a、210b、キャパシタを形成する。ビット線が半導体領域208の下に位置し、ワード線210a、210b、キャパシタが半導体領域208の上に位置するため、ビット線205の配置の自由度が高まり、オープンビット線型のDRAMとすることで6F2以下、あるいはセルトランジスタの構造を特殊なものとすることで4F2以下とできる。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】低いビットコストで積層化可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1メモリセルアレイ層10と、第1絶縁層31と、第2メモリセルアレイ層20とを有する。第1メモリセルアレイ層10は、複数の第1メモリセルMC1を具備する第1NANDセルユニットNU1を有する。第1メモリセルMC1は、第1半導体層11と、その上に形成された第1ゲート絶縁膜12と、第1浮遊ゲート13とを有する。第2メモリセルアレイ層20は、複数の第2メモリセルMC2を具備する第2NANDセルユニットNU2を有する。第2メモリセルMC2は、第2浮遊ゲート23と、第2ゲート絶縁膜22と、第2半導体層21とを有する。上下に連続する第1及び第2浮遊ゲート13,23の第1の方向の両側面に第1の方向と直交する第2の方向に延びる制御ゲート33が形成される。

(もっと読む)

半導体記憶装置の製造方法

【課題】高集積化を図ることができる半導体記憶装置の製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、基板上に第1膜と第2膜とを交互に積層して第1積層体を形成する工程と、前記第1積層体上に第3膜と第4膜とを交互に積層して第2積層体を形成する工程と、前記第1膜のエッチング速度よりも前記第3膜のエッチング速度の方が低くなる条件でエッチングを施すことにより、前記第2積層体及び前記第1積層体を貫く貫通ホールを形成する工程と、前記貫通ホールの内面上に電荷蓄積膜を形成する工程と、前記貫通ホール内に半導体部材を形成する工程と、を備える。そして、前記第1膜と前記第2膜とを相互に異なる材料によって形成し、前記第3膜と前記第4膜とを相互に異なる材料によって形成し、前記第1膜と前記第3膜とを相互に異なる材料によって形成する。

(もっと読む)

半導体記憶装置

【課題】動作速度が高い半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、一方向に沿って相互に平行に配列された複数枚のゲート電極膜と、前記一方向に延び、前記複数枚のゲート電極膜を貫通する半導体部材と、前記ゲート電極膜と前記半導体部材との間に設けられた電荷蓄積膜と、を備える。前記ゲート電極膜における前記半導体部材に対向した端部には、前記一方向に沿って突出した凸部が設けられており、前記ゲート電極膜間の空間の一部は気体層となっている。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コストが低い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、絶縁膜及び電極膜が交互に積層された積層体を形成する工程と、前記積層体上に、サイズが相互に異なる複数のホールが形成されたハードマスクを形成する工程と、マスク材料を堆積させることにより、最も小さい前記ホールを閉塞させると共に、その他の前記ホールを小さくする工程と、前記マスク材料及び前記ハードマスクをマスクとしてエッチングを施すことにより、前記その他のホールの直下域において、各所定枚数の前記絶縁膜及び前記電極膜を除去して、コンタクトホールを形成する工程と、前記コンタクトホールを介してエッチングを施すことにより、前記電極膜の一部分を除去して隙間を形成する工程と、前記隙間内に絶縁材料を埋め込む工程と、前記コンタクトホール内に導電材料を埋め込む工程と、を備える。

(もっと読む)

101 - 120 / 887

[ Back to top ]