Fターム[5F083PR21]の内容

Fターム[5F083PR21]に分類される特許

121 - 140 / 1,567

記憶装置

【課題】アモルファスシリコンを記憶部に用いる記憶装置の動作電圧を低減し、かつ、それを低温プロセスで形成する。

【解決手段】実施形態に係わる記憶装置は、結晶化されたSixGe1−x (0≦x<1)層を含む第1の電極EL1と、金属元素を含む第2の電極EL2と、第1及び第2の電極EL1,EL2間に配置され、アモルファスSi層を含む可変抵抗部VRと、アモルファスSi層内の金属元素を含むフィラメントの長さを制御する制御回路とを備える。

(もっと読む)

電子部品の製造方法

【課題】導電膜を含む層の加工によって密の配線と疎の配線とが混在して形成された配線層で、所望の配線間の領域にのみ空隙を形成することができる電子部品の製造方法を提供する。

【解決手段】実施形態によれば、電子部品の製造方法は、まず、密の配線と疎の配線とを含む配線パターンとなるように、基板1上の導電性材料膜を含む加工対象を加工する。ついで、密の配線の形成領域にのみ配線間を埋め込む犠牲膜111を形成した後、基板1上に絶縁膜112を形成する。絶縁膜112上にレジスト113を塗布し、密の配線の形成領域上の一部と疎の配線の形成領域とが露出するようにレジスト113のパターニングを行った後、レジスト113をマスクとして絶縁膜112をエッチングする。さらに、密の配線の形成領域上の一部を通して、犠牲膜111を除去する。そして、疎の配線の形成領域で隣接する配線間を埋め込むように基板1上に埋込絶縁膜114を形成する。

(もっと読む)

半導体装置

【課題】実施形態によれば、他の特性を損ねずにセル間の電荷の移動を抑制することができる半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、積層体と、第1の絶縁膜と、電荷蓄積膜と、第2の絶縁膜と、チャネルボディとを備えている。積層体は、基板上にそれぞれ交互に積層された複数の電極層と複数の絶縁層とを有する。第1の絶縁膜は積層体を貫通して形成されたホールの側壁に設けられている。電荷蓄積膜はホール内における第1の絶縁膜の内側に設けられている。電荷蓄積膜は、電極層に対向する部分で電極層に向かって突出し、他の部分よりも膜厚が厚い凸部を有する。第2の絶縁膜は電荷蓄積膜の内側に設けられている。チャネルボディは第2の絶縁膜の内側に設けられている。

(もっと読む)

不揮発性記憶装置

【課題】駆動電圧が低く、消費電力が少ない不揮発性記憶装置を提供する。

【解決手段】実施形態に係る不揮発性記憶装置1は、第1の方向に延びる複数本のワード線を含むワード線配線層WLと、前記第1の方向に対して交差する第2の方向に延びる複数本のビット線を含むビット線配線層BLと、各前記ワード線と各前記ビット線との間に配置されたピラー16と、前記ピラー16の側面上に設けられ、負の固定電荷を含有する電荷含有部材18と、を備える。前記ピラー16は、p形層22p及びn形層22nが設けられたダイオード膜22と、前記ダイオード膜22に積層された抵抗変化膜25と、を有する。そして、前記電荷含有部材18は前記p形層22pの側面上に配置されており、前記n形層22nの側面上には配置されていない。

(もっと読む)

半導体装置及びその製造方法

【課題】実施形態によれば、十分な消去速度が得られる半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、第1の積層体と、メモリ膜と、第1のチャネルボディと、第2の積層体と、ゲート絶縁膜と、第2のチャネルボディとを備えている。前記選択ゲートの側面と前記第2の絶縁層との間に段差部が形成されている。前記段差部を被覆する部分の前記第2のチャネルボディの膜厚は、前記第2の絶縁層間に設けられた部分の膜厚よりも厚い。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

半導体デバイスの製造方法及び半導体デバイス

【課題】 高誘電率及び高温状態で安定したキャパシタ絶縁膜の形成を実現する。

【解決手段】 基板上に形成された下電極の上に、キャパシタの絶縁膜としてルチル型のチタン酸化膜を形成する半導体デバイスの製造方法であって、チタン酸化膜の結晶格子の大きさとほぼ等しい大きさの結晶格子を有する絶縁膜をチタン酸化膜の下地膜として形成する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い歩留りで製造し得る半導体装置の製造方法を提供する。

【解決手段】ゲート配線16aを形成するのと同時に形成された位置合わせマーク16fに対して位置合わせして、コンタクトホールの第1の部分パターン61a1をゲート配線の一部と重なり合うようにフォトレジスト膜に露光する工程と、活性領域11bを形成するのと同時に形成された位置合わせマーク11fに対して位置合わせして、コンタクトホールの第2の部分パターン61a2を活性領域の一部と重なり合うようにフォトレジスト膜に露光する工程と、フォトレジスト膜を現像し、第1の部分パターンと第2の部分パターンとが露光された箇所に開口部を形成する工程と、フォトレジスト膜をマスクとして絶縁膜をエッチングし、ゲート配線とソース/ドレイン拡散層20とに達するコンタクトホールを形成する工程とを有している。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化した半導体集積回路において用いられるキャパシタを提供する。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

(もっと読む)

キャパシタ、半導体装置及びそれらの製造方法

【課題】高い比誘電率を有する容量絶縁膜を使用して、静電容量を大きくし、しかもリーク電流を低減する。

【解決手段】容量絶縁膜として、c軸配向した結晶酸化ニオブを用い、特に成膜時の酸素含有量を、例えば、スパッタガスにおける酸素ガス比を調整することで制御して、a軸配向ピークを示さず、c軸配向ピークが優先した膜を形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ゲートの端部に集中する電界を緩和し、電荷のトラップおよびトンネル絶縁膜の破壊を抑制し、信頼性を向上させる。

【解決手段】半導体記憶装置は、半導体基板上に設けられたアクティブエリアを備えている。素子分離部が、アクティブエリア間に設けられ、絶縁膜で充填されている。データを記憶する複数のメモリセルがアクティブエリアに形成されている。空洞が、アクティブエリアのメモリセルが形成された部分の上端縁部と素子分離部内の絶縁膜との間に設けられている。

(もっと読む)

半導体装置の製造方法

【課題】チタン酸ストロンチウム膜を容量絶縁膜として用いたキャパシタにおいて、静電容量が大きく、リーク電流が小さいキャパシタを形成する。

【解決手段】半導体装置の製造方法は、下部電極を形成後、下部電極上に中間窒化チタン膜及び非晶質チタン酸ストロンチウム膜が互いに接するように積層された積層膜を形成する。次に、第1の熱処理を行うことにより、中間窒化チタン膜及び非晶質チタン酸ストロンチウム膜を結晶質チタン酸ストロンチウム膜に変換する。次に、結晶質チタン酸ストロンチウム膜上に上部電極を形成する。

(もっと読む)

記憶装置及びその製造方法

【課題】高集積化が可能な記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る記憶装置は、下部電極層と、前記下部電極層上に設けられ、複数の微小導電体が隙間を介して集合したナノマテリアル集合層と、前記ナノマテリアル集合層上に設けられ、導電性であり、前記微小導電体に接し、開口部が形成された保護層と、前記保護層上に設けられ、前記保護層に接した上部電極層と、を備える。

(もっと読む)

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

シリコン構造体、当該シリコン構造体を用いた容量素子および当該シリコン構造体の作製方法

【課題】3次元的に複雑な形状のシリコン構造体を提供する。また、当該シリコン構造体を、自然と秩序が生じて自分自身で秩序的なパターン形成が行われる現象を用いて簡便に作製する方法を提供する。

【解決手段】アモルファスシリコン層に水素雰囲気下でプラズマ処理を行って、当該シリコン層表面に微結晶シリコンを成長させる反応過程と、露出しているアモルファスシリコン層をエッチングする反応過程を並行して進行させ、当該シリコン層上に微結晶状の上部構造体とアモルファス状の下部構造体からなるナノ構造体を形成することにより、3次元的に複雑な形状のシリコン構造体を提供することができる。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】膜中の酸素濃度を制御しつつ、段差被覆性を向上させ、抵抗率の低い薄膜を形成することができる。

【解決手段】基板を収容した処理室内にCVD反応が生じる条件下で、タンタルを含む原料ガスを供給し排気して、前記基板上にタンタル含有層を形成する工程と、前記処理室内にオゾンガスを短パルスで供給し排気することで、前記タンタル含有層の表面を酸化して、前記タンタル含有層の表面に酸化タンタル層を形成する工程と、を行うことで基板上に酸化タンタル膜を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

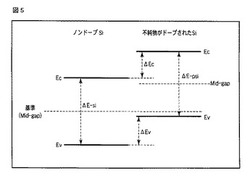

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

不揮発性半導体記憶装置

【課題】データ保持特性を向上させた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1配線と第2配線との間に配置され、抵抗を変化させる可変抵抗素子を有するメモリセルを備える。メモリセルは、可変抵抗層、第1電極層、第2電極層、及び第1バリアハイト制御層を備える。可変抵抗層は、可変抵抗素子として機能する。可変抵抗層は、炭素(C)、珪素(Si)、及び水素(H)を含み、又は炭素(C)、珪素(Si)、及び水素(H)を含み且つ窒素(N)及び酸素(O)の少なくともいずれか一方を含む。第1電極層は、可変抵抗素子の一方の面側に設けられている。第2電極層は、可変抵抗素子の他方の面側に設けられている。第1バリアハイト制御層は、絶縁物からなり且つ可変抵抗層の一方の面と第1電極層との間に構成されている。

(もっと読む)

121 - 140 / 1,567

[ Back to top ]