Fターム[5F083PR21]の内容

Fターム[5F083PR21]に分類される特許

201 - 220 / 1,567

不揮発性記憶装置およびその製造方法

【課題】より低抵抗な配線層を有する不揮発性記憶装置を提供する。

【解決手段】実施形態の不揮発性記憶装置は、書き替え可能な複数の不揮発性メモリセルと、前記複数のメモリセルのそれぞれに電気的に接続可能な配線層と、を備えた不揮発性半導体記憶装置である。前記配線層は、絶縁層に設けられたトレンチ内に設けられ、前記配線層は、第1導電層と、前記第1導電層の上に設けられた第2導電層と、を有し、前記配線層が充填されていない前記トレンチに対する前記第1導電層の埋め込み性は、前記配線層が充填されていない前記トレンチに対する前記第2導電層の埋め込み性よりも高く、前記第2導電層の比抵抗は、前記第1導電層の比抵抗よりも低い。

(もっと読む)

半導体装置の製造方法

【課題】ReRAM用のダイオードを形成するために、アモルファス半導体膜の表面に酸化膜が形成された場合であっても、アモルファス半導体膜を結晶化することが可能な半導体装置の製造方法を提供する。

【解決手段】基板101上に、下部電極層111とアモルファス半導体膜112を形成し、アモルファス半導体膜112上の自然酸化膜121を介して、還元性のある金属層113Aを含む上部電極層113を形成し、マイクロ波を用いたアニールにより、金属層113Aと酸化膜121を反応させて、酸化膜121を半導体へと還元する。また、アニールにより更に、金属層113Aと半導体112を反応させて、金属層113Aの構成元素と半導体112の構成元素とを含む反応生成物113Cを生成する。また、反応生成物113Cを結晶成長のためのシードとして、アモルファス半導体膜112を結晶成長させる。

(もっと読む)

半導体装置及びその製造方法、並びに吸着サイト・ブロッキング原子層堆積法

【課題】キャパシタの誘電体膜において、リーク特性改善のためのAlドープ層を設けても、誘電体膜がAlドープ層で分断されず、サイズ効果の影響を抑え、結晶性の良好な誘電体膜を提供する。

【解決手段】誘電体膜中に少なくとも1層のAlドープ層を有し、Alドープ層の1層におけるAl原子の面密度を1.4E+14[atoms/cm2]未満とする。また、その面密度を達成するため、通常のALDによる誘電体膜成膜と、Alソースの吸着サイトを制限するブロッカー分子の吸着を行った後、Alソースを吸着させ、反応ガスを導入して反応させる吸着サイト・ブロッキングALD法によるAl添加の組み合わせを採用する。

(もっと読む)

半導体記憶装置

【課題】動作速度が高い半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、それぞれ複数の絶縁膜及び電極膜が交互に積層され、前記絶縁膜及び前記電極膜の積層方向に延びる貫通ホールが形成された積層体と、前記貫通ホールの内面上に設けられたブロック層と、前記ブロック層に囲まれた電荷蓄積層と、前記電荷蓄積層に囲まれたトンネル層と、前記トンネル層に囲まれた半導体ピラーと、を備える。そして、前記トンネル層における前記半導体ピラー側の部分の誘電率は、前記トンネル層における前記電荷蓄積層側の部分の誘電率よりも高い。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGとp型ウエルPW1との間および制御ゲート電極CGとメモリゲート電極MGとの間には、絶縁膜5が形成されている。この絶縁膜5のうち、メモリゲート電極MGの下面と半導体基板1の上面との間の部分は、酸化シリコン膜9a,9bと酸化シリコン膜9a,9bに挟まれた窒化シリコン膜10aとを有している。絶縁膜5のうち、制御ゲート電極CGの側面とメモリゲート電極MGの側面との間の部分は、酸化シリコン膜6aからなり、窒化シリコン膜10aを有していない。

(もっと読む)

キャパシタの製造方法および半導体装置の製造方法

【課題】高温相の結晶構造の容量絶縁膜を電極上に直接形成可能なキャパシタの製造方法を提供する。

【解決手段】本発明のキャパシタCapの製造方法は、第一の電極3を形成する工程と、成膜温度が低い順に、非晶質相、低温相の結晶構造、高温相の結晶構造を形成し得る金属酸化物の形成工程であって、前記第一の電極3上に、前記低温相の結晶構造の成膜温度よりも低い第一の温度で前記非晶質相からなる前記金属酸化物を形成する工程と、前記第一の温度から、前記高温相の結晶構造の成膜温度である第二の温度まで、10℃/秒以上の昇温速度で昇温し、前記第二の温度で前記金属酸化物をアニールすることにより、前記金属酸化物に前記高温相の結晶構造を析出させて容量絶縁膜4とする工程と、前記容量絶縁膜4上に第二の電極5を形成する工程を採用する。

(もっと読む)

半導体装置の製造方法、基板処理方法及び基板処理装置

【課題】 膜中の酸素濃度を制御しつつ、良好な段差被覆性を有する酸化タンタル系の膜を形成する。

【解決手段】 基板を収容した処理室内にCVD反応が生じる条件下で、タンタルを含む原料ガスと窒化剤とを供給して、基板上に窒化タンタル層を形成する工程と、処理室内に酸化剤を供給して、窒化タンタル層の酸化剤による酸化反応が不飽和となる条件下で、窒化タンタル層を酸化する工程と、を交互に複数回繰り返すことで、基板上に、化学量論的にタンタルおよび窒素に対し酸素が不足した導電性の酸窒化タンタル膜を形成する。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】 高誘電率絶縁膜の吸湿を抑制し、信頼性を向上させる。

【解決手段】 処理容器内に基板を搬入する工程と、処理容器内で基板上に高誘電率絶縁膜を形成する工程と、処理容器内で高誘電率絶縁膜上に高誘電率絶縁膜よりも吸湿性の低い低吸湿性絶縁膜を形成する工程と、処理容器内より低吸湿性絶縁膜形成後の基板を搬出する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で横方向に成長するシリコン膜が連結されることを防ぎつつ、活性領域上に十分な厚みのシリコン膜を形成可能とした半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上に第1のシリコン膜12aを選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に第1のシリコン膜12aを覆うのに十分な厚みでマスク絶縁膜を埋め込んだ後、このマスク絶縁膜を第1のシリコン膜12aの表面が露出するまでエッチングにより除去する工程と、第1のシリコン膜12a上に第2のシリコン膜12bを選択的にエピタキシャル成長させる工程とを含む。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 セル部のブロック絶縁膜の誘電率を低下させることなく、セル部のブロック絶縁膜を分断するセル間における絶縁膜中の欠陥を低減し、電荷保持特性の劣化を抑制する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】 実施形態の不揮発性半導体記憶装置においては、半導体基板上にトンネル絶縁膜、前記トンネル絶縁膜上に電荷蓄積層、前記電荷蓄積層上にブロック絶縁膜が設けられる。前記半導体基板に設けられた素子分離溝部に埋め込まれ、底面が前記半導体基板と前記トンネル絶縁膜の接する面の高さよりも低く、かつ上面が前記電荷蓄積層および前記ブロック絶縁膜の接する面の高さよりも低い第1の素子分離絶縁膜が設けられる。前記第1の素子分離絶縁膜上に形成され、前記ブロック絶縁膜の側面と接して前記ブロック絶縁膜上面まで突出し、かつSi濃度が前記ブロック絶縁膜よりも高い第2の素子分離絶縁膜が設けられる。

(もっと読む)

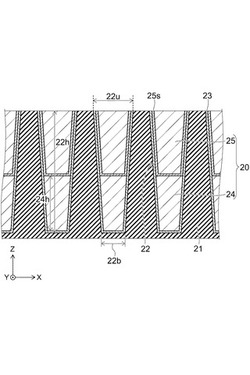

半導体装置およびその製造方法

【課題】半導体基板の結晶性の悪化を招くことなく、素子分離トレンチの幅を小さくできる半導体装置の製造方法を提供する。

【解決手段】マスク用窒化膜51およびパッド酸化膜52からなるハードマスクを用いて、シリコン基板2がエッチングされることにより、素子分離トレンチ21が形成される。素子分離トレンチ21の内面に熱酸化法によりライナー酸化膜22が形成される。続いて、半導体基板2を窒素雰囲気中に配置して、半導体基板2が熱処理される。熱処理後に、エッチングにより、ライナー酸化膜22が薄膜化される。そして、HDP−CVD法により、絶縁物23が素子分離トレンチ21内に埋め込まれる。

(もっと読む)

半導体装置の製造方法

【課題】第1の金属元素および第2の金属元素を含む第3の金属酸化膜を形成する際に、第3の金属酸化膜中の第1の金属元素及び第2の金属元素の組成比の制御性を向上させる。

【解決手段】第1の金属元素を含む第1原料を供給し排気する工程と、酸化剤を供給し排気する工程と、を1サイクルとしてこのサイクルを少なくとも1回行うことで第1の金属酸化膜を形成する工程と、第2の金属元素を含む第2原料を供給し排気する工程と、酸化剤を供給し排気する工程と、を1サイクルとしてこのサイクルを少なくとも1回行うことで第2の金属酸化膜を形成する工程と、を交互に所定回数行うことで第3の金属酸化膜を形成する工程を有し、第1原料および第2原料として、第2の金属酸化膜を形成する工程における1サイクルあたりに形成する膜厚が、第1の金属酸化膜を形成する工程における1サイクルあたりに形成する膜厚よりも小さくなるような原料を用いる。

(もっと読む)

相変化メモリ材料を製造するためのテルル(Te)前駆体

【課題】Te含有組成物を提供する。

【解決手段】R−Te−Dの一般構造を有する重水素化された有機テルロールであって、式中、Rが、1〜10個の炭素を直鎖、分枝又は環状の形態で有するアルキル基又はアルケニル基;C6-12の芳香族基;ジアルキルアミノ基;有機シリル基;及び有機ゲルミルからなる群より選択される重水素化された有機テルロールを含むTe含有組成物が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】サイドウォール間に層間絶縁膜を埋め込むときに埋め込み不良の発生を防止できる半導体装置の製造方法を提供する。

【解決手段】シリコン基板2の表面上に、ゲート酸化膜6、ポリシリコン層(第1ゲート層)9、タングステンシリサイド層(第2ゲート層)10および絶縁層8が形成される。絶縁層8が所定のゲートパターンにエッチングされる。タングステンシリサイド層10が前記所定のゲートパターンにエッチングされる。タングステンシリサイド層10の側壁が後退される。この後、ポリシリコン層9が前記所定のゲートパターンにエッチングされる。ゲート酸化膜6が前記所定のゲートパターンにエッチングされる。

(もっと読む)

半導体装置の製造方法

【課題】メモリセル領域と周辺回路領域の双方におけるMOSトランジスタの最適化が可能な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、サイドウォールを側壁に有するゲート電極を含むMOSトランジスタを、半導体基板1上のメモリセル領域及び周辺回路領域に備えた半導体装置の製造方法であって、前記サイドウォールを形成した後に、選択エピタキシャル成長法により、前記半導体基板1上面にシリコン層10を形成する工程を備え、前記シリコン層10を形成した後に、少なくとも前記周辺回路領域をマスク20bで覆い、エッチングにより、前記メモリセル領域内のMOSトランジスタTr1のサイドウォール9cを薄化する工程を採用する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】容量絶縁膜である強誘電体のアニール工程を経ても、PchMOS型トランジスタのVth変動を抑制することができる半導体記憶装置およびその製造方法を提供すること。

【解決手段】半導体基板1上に形成され、P型不純物が導入されたゲート電極を有するPchMOS型トランジスタ4と、前記PchMOS型トランジスタ4の上方を覆うように、前記半導体基板1上に形成された第1の水素バリア膜8と、前記第1の水素バリア膜8上に形成され、容量絶縁膜として強誘電体を用いた強誘電体キャパシタ7と、前記強誘電体キャパシタ7の上方および側方を覆い、前記強誘電体キャパシタ7の周縁部において前記第1の水素バリア膜8と接続する第2の水素バリア膜14とを備え、前記第1の水素バリア膜8は、シリコン元素、水素元素、およびシリコン元素よりも水素元素を脱離しにくい第3の元素を含む。

(もっと読む)

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼できる非常に小型の記憶素子を含む、3次元集積回路メモリ用の構造を低い製造コストで提供すること。

【解決手段】3次元メモリデバイスは、絶縁材料によって分離され、復号化回路を介してセンスアンプに結合可能なストリングとして配置された複数の隆起した形状スタック含む。ダイオードは、ストリングのストリング選択端部又は共通ソース選択端部のどちらか一方においてビット線構造に接続される。導電材料の帯片は、隆起した形状のスタックのサイドに側面を有する。ワード線として配列された複数の導電線は、行デコーダに結合することができ、複数の隆起した形状のスタックの上で直交して延びる。記憶素子は、スタック上の電導性帯片の側面と導電線との間の交点における界面領域の多層アレイに設けられる。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】周辺回路領域の素子の寿命が劣化するのを抑制しつつ、浮遊ゲート電極と制御ゲート電極とのカップリング性を確保する。

【解決手段】シリコン基板11は、セル領域および周辺回路領域が設けられている。トンネル絶縁膜12は、セル領域および周辺回路領域のシリコン基板11上に形成されている。浮遊ゲート電極膜13は、セル領域および周辺回路領域のトンネル絶縁膜12上に形成されている。電極間絶縁膜16は、セル領域の浮遊ゲート電極膜13上に形成されている。シリコン酸化膜14および電極間絶縁膜16は、周辺回路領域の浮遊ゲート電極膜13上に形成されている。制御ゲート電極膜17は、セル領域および周辺回路領域の電極間絶縁膜16上に形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】メモリセル間の短絡を防止した上で、活性領域上にシリコン膜が十分に形成された半導体装置を提供する。

【解決手段】半導体基板2の表層に埋め込み形成された素子分離膜8によって、活性領域7が区画された半導体装置1であって、前記活性領域7の側面17が露出するように、前記素子分離膜8の上面の一部が除去されて設けられた凹部と、前記凹部を埋め込みつつ、前記活性領域7の上面7d及び前記側面17と接するように設けられたシリコン膜10と、を有することを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】リークパスを確実に防止することができる、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置は、ゲート絶縁膜を介して半導体基板上に設けられたゲート電極と、前記ゲート電極の側部に設けられた側壁絶縁膜と、前記半導体基板内における前記ゲート絶縁膜を挟むような位置に形成され、前記側壁絶縁膜により覆われた被覆領域と前記側壁絶縁膜により覆われていない露出領域とを有する、ソース又はドレイン領域と、前記ゲート電極及び前記側壁絶縁膜を覆うように形成された、エッチングストッパ膜と、前記半導体基板上に、前記エッチングストッパ膜を埋め込むように設けられた、層間絶縁膜と、前記層間絶縁膜を貫通するように設けられ、前記露出領域に接続される、第1セルコンタクトプラグとを具備する。前記エッチングストッパ膜は、前記被覆領域と前記露出領域との境界部分が完全に覆われるように、前記露出領域の一部を覆っている。

(もっと読む)

201 - 220 / 1,567

[ Back to top ]