Fターム[5F083PR21]の内容

Fターム[5F083PR21]に分類される特許

141 - 160 / 1,567

半導体装置の製造方法、基板処理方法及び基板処理装置

【課題】 金属薄膜上に金属酸化膜を形成する際に、金属薄膜の酸化を抑制させる。

【解決手段】 原料と酸化剤とを用い、金属薄膜が形成された基板上に、ハフニウム、イットリウム、ランタン、アルミニウム、ジルコニウム、ストロンチウム、チタン、バリウム、タンタル、ニオブからなる群から選択される少なくとも1種類以上の元素を含む金属酸化膜を、酸化による結晶粒の異常成長が起こらない温度であって、かつ、アモルファス状態となる第1温度で形成するステップと、原料と酸化剤とを用い、アモルファス状態の金属酸化膜上に、アモルファス状態を維持しつつ、ハフニウム、イットリウム、ランタン、アルミニウム、ジルコニウム、ストロンチウム、チタン、バリウム、タンタル、ニオブからなる群から選択される少なくとも1種類以上の元素を含む金属酸化膜を、第1温度を超える第2温度で形成するステップと、を有する。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

記憶素子、記憶装置、信号処理回路、記憶素子の駆動方法

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶素子を提供する。消費電力の低減可能な信号処理回路を提供する。

【解決手段】クロック信号に同期してデータを保持する記憶素子において、酸化物半導体層にチャネルが形成されるトランジスタ及び容量素子を用いることより、電源電圧の供給が停止した間もデータ保持ができる。ここで、電源電圧の供給を停止する前に、クロック信号のレベルを一定に保った状態で当該トランジスタをオフ状態とすることにより、データを正確に容量素子に保持させることができる。また、このような記憶素子を、CPU、メモリ、及び周辺制御装置のそれぞれに用いることによって、CPUを用いたシステム全体で、電源電圧の供給停止を可能とし、当該システム全体の消費電力を削減することができる。

(もっと読む)

気化装置及び成膜装置

【課題】液体ソースを気化して成膜処理に用いられる処理ガスを得るにあたり、気化量を安定させ、かつ処理ガス濃度を高めること。

【解決手段】液体ソースを貯留するための気化室3の天井部に面接触した状態で、毛細管現象により液体ソースが広がる繊維体からなる面状体41を設ける。また、一端側が前記面状体41に接続され、他端側が前記気化室3内の液体ソースに接触するように、前記液体ソースを毛細管現象により吸い上げて面状体41に供給する吸い上げ部42を設ける。気化室3を加熱することにより、面状体41が加熱され、液体ソースが液面から気化すると共に、面状体41の表面からも気化するので、処理ガス濃度を高めることができる。また、吸い上げ部42のみが液体ソースに接触しているので、液面の高さ位置が変動しても、面状体への液体ソースの拡散状態に影響がなく、安定した気化量を確保することができる。

(もっと読む)

半導体メモリ装置

【課題】短チャネルでも動作するフローティングゲートを有する半導体メモリ装置を提供する。

【解決手段】フローティングゲート104に窒化インジウム、窒化亜鉛等の仕事関数が5.5電子ボルト以上の高仕事関数化合物半導体を用いる。このことにより、基板101とフローティングゲート104の間のフローティングゲート絶縁膜103のポテンシャル障壁が従来のものより高くなり、フローティングゲート絶縁膜103を薄くしても、トンネル効果による電荷の漏洩を低減できる。フローティングゲート絶縁膜103をより薄くできるのでチャネルをより短くできる。

(もっと読む)

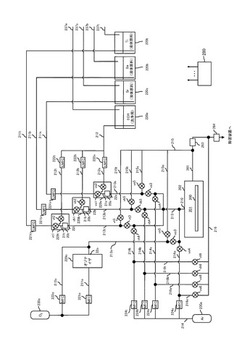

半導体装置及び半導体記憶装置

【課題】ノイズによるデータ信号への影響を抑制する半導体記憶装置を提供する。

【解決手段】記憶回路を具備し、記憶回路は、それぞれが電界効果トランジスタであり、1個目の電界効果トランジスタ111a−1のソース及びドレインの一方にデジタルデータ信号が入力され、k個目(kは2以上n(nは2以上の自然数)以下の自然数)の電界効果トランジスタのソース及びドレインの一方がk−1個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続されるn個の電界効果トランジスタと、それぞれ一対の電極を有し、m個目(mはn以下の自然数)の容量素子の一対の電極の一方が、n個の電界効果トランジスタのうち、m個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続され、少なくとも2つの容量素子における容量値が異なるn個の容量素子112aー1〜112aーnとを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】データ保持特性を向上させた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1配線と第2配線との間に配置され、抵抗を変化させる可変抵抗素子を有するメモリセルを備える。メモリセルは、可変抵抗層、第1電極層、第2電極層、及び第1バリアハイト制御層を備える。可変抵抗層は、可変抵抗素子として機能する。可変抵抗層は、炭素(C)、珪素(Si)、及び水素(H)を含み、又は炭素(C)、珪素(Si)、及び水素(H)を含み且つ窒素(N)及び酸素(O)の少なくともいずれか一方を含む。第1電極層は、可変抵抗素子の一方の面側に設けられている。第2電極層は、可変抵抗素子の他方の面側に設けられている。第1バリアハイト制御層は、絶縁物からなり且つ可変抵抗層の一方の面と第1電極層との間に構成されている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、半導体装置の歩留まりを向上可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】アンモニア水を用いた湿式エッチングにより、エッチングマスク形成用溝の側面を洗浄することで、下部電極及びエッチングマスクの母材となる下部電極形成用金属膜を成膜する前に、異方性ドライエッチング時にエッチングマスク形成用溝の側面に付着したポリマーを除去し、次いで、エッチングマスク形成用溝に、下部電極形成用金属膜を成膜することでエッチングマスクを形成し、その後、湿式エッチングにより、エッチングマスクをマスクとして、メモリセル領域に形成された第4の層間絶縁膜を選択的に除去する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】良好な電気特性及び信頼性を有する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、半導体基板に形成された素子分離溝に埋め込まれた素子分離絶縁膜と、素子分離溝により所定間隔だけ隔てられ、且つ、半導体基板上に第1の絶縁膜と電荷蓄積膜とが順次積層されてなる積層構造の複数のメモリセルと、電荷蓄積膜と素子分離絶縁膜との上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された制御電極膜とを有し、素子分離絶縁膜の上面は電荷蓄積膜の上面よりも低く、第2の絶縁膜は、電荷蓄積膜上のセル上部分と素子分離絶縁膜上のセル間部分とを備え、セル上部分の誘電率はセル間部分の誘電率よりも低い。

(もっと読む)

半導体装置及びその製造方法

【課題】所望の特性を維持しつつ強誘電体膜のより一層の薄膜化が可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上方に形成された強誘電体キャパシタ62は、下部電極48と、強誘電体特性を備えた誘電体膜(強誘電体膜)50と、上部電極60とを有する。上部電極50は、Ir等の導電材料を添加して導電性を付与した強誘電体材料により形成された導電体酸化物膜52を備え、この導電体酸化物膜52が誘電体膜50に接している。これにより、誘電体膜50と上部電極膜60との間に常誘電体層が発生することが抑制され、所望の特性を維持しつつ誘電体膜50のより一層の薄膜化が可能になる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、水素または希ガスのいずれかの元素が添加されている。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体膜を薄膜化して低電圧の動作を可能にしつつ、飽和反転電荷量を増大ささせる。

【解決手段】半導体装置は、下部電極41と、強誘電体膜36と、上部電極35とから形成されるキャパシタ42を有する。強誘電体膜36は、PZTから形成され、膜厚方向の中央部分のTiの含有量が他の領域の比べて多くなっている。Tiの分布は、膜厚方向の中央から上下の電極35,41に向けて減少するような分布である。さらに、Srなどのドーパント元素の含有量が、下部電極41との界面で最も多く、上部電極35に向けて減少する分布を有する。

(もっと読む)

半導体記憶装置の製造方法

【課題】製造が容易なNAND型半導体記憶装置の製造方法を提供する。

【解決手段】製造方法は、基板101上に第1絶縁膜105及び第2絶縁膜106を交互に積層して積層体110を形成する工程と、第1絶縁膜105及び第2絶縁膜106の積層方向に延び、積層体110を貫通する貫通孔114を形成する工程と、貫通孔114の内面上に、MONOS116を構成するブロック絶縁膜、チャージトラップ膜及びトンネル誘電体膜の少なくとも一部を形成する工程と、トンネル誘電体膜上にチャネル半導体117を形成する工程と、積層体110にトレンチ121を形成する工程と、トレンチ121を介してエッチングを施すことにより、第2絶縁膜106を除去する工程と、第2絶縁膜106を除去した後の空間内に導電材料を埋め込む工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】基板に電圧を印加して基板にダメージを及ぼすことなく、当該基板における、大型基板において特に顕在化する複雑な態様の反りの発生部位及び発生状態を容易且つ正確に特定する。そして、大型基板でも確実なチャッキングに供することを可能とする。

【解決手段】センサ部2は、搭載面1aの中央部分に設けられた第1のセンサ群11と、第1のセンサ群11を囲む第2のセンサ群12と、第2のセンサ群12を囲む第3のセンサ群13とを有する。第1のセンサ群11は、基板面の中央部分に対応して設けられた1つの静電容量センサ10aから、第2のセンサ群12は、第1のセンサ群11を同心状に囲む複数の静電容量センサ10aから、第3のセンサ群13は、第2のセンサ群12を同心状に囲み、搭載面1aの周縁の近くに設けられた複数の静電容量センサ10aを有する。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】複数のメモリセルを3次元状に配置し、かつ、メモリセルにMONOS型トランジスタを使用するNAND型不揮発性メモリにおいて、データ保持特性の劣化を抑制することができる技術を提供する。

【解決手段】ギャップ絶縁層GIL1の右端部側に凹部CUが形成されている。このとき、この凹部CUの形状を反映するように、凹部CUの内部に上部電位障壁層EB2と電荷蓄積層ECが形成されており、この凹部CUの形状を反映した電荷蓄積層ECの内側に形成される下部電位障壁層EB1によって、凹部CUが完全に埋め込まれている。このため、凹部CUを埋め込んだ下部電位障壁層EB1の表面は平坦になっており、この平坦になっている下部電位障壁層EB1の内側に柱状半導体部PSが形成される。

(もっと読む)

埋め込みビットラインを備えた半導体装置の製造方法

【課題】埋め込みビットラインの抵抗を減少させることができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板201に活性領域203を分離するトレンチ202をエッチングにより形成するステップと、活性領域203の何れか1つの側壁の一部を露出させた開口部207を有する絶縁膜205を形成するステップと、絶縁膜205上にトレンチ202を部分的に埋め込み、開口部207を埋め込むようにシリコン膜パターン208Aを形成するステップと、シリコン膜パターン208A上に金属膜209を形成するステップと、金属膜209及びシリコン膜パターン208Aを反応させて、埋め込みビットラインとなる金属シリサイド膜211を形成するステップとを含む。

(もっと読む)

半導体デバイスの製造方法および基板処理装置

【課題】TiN膜の上部に形成するTiO膜の少なくとも一部の結晶構造をブルッカイト型構造又はルチル型構造とし、TiO膜の誘電率を高める。

【解決手段】ジルコニウム酸化膜の膜厚を制御することにより、ジルコニウム酸化膜の少なくとも一部の結晶構造を立方晶系構造又は正方晶系構造とし、これにより、チタン酸化膜の少なくとも一部の結晶構造をブルッカイト型構造又はルチル型構造とする。

(もっと読む)

誘電体膜の形成方法、及びこれを用いる半導体素子のキャパシタの形成方法

【課題】誘電特性及び漏れ電流特性を向上させることのできる半導体素子の誘電体膜の形成方法及びキャパシタの形成方法を提供する。

【解決手段】誘電体膜は、原子層堆積法により、ウェーハ上に酸化ジルコニウム(ZrO2)及び酸化アルミニウム(Al2O3)で構成された誘電体膜を形成する方法であって、チャンバー内に、1つのZrと1つのAl原子とが1つの分子を構成しているソースガスを注入し、ウェーハ上に、ZrO2とAl2O3とからなる[ZrO2]x[Al2O3]y(ここで、x及びyは正数である)膜を形成するステップを繰り返すことにより、ZrO2とAl2O3とで構成された厚さ30Å〜500Åの誘電体膜を形成する。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】シリンダ型下部電極の剥がれ落ちを防止する、半導体装置の製造方法を提供する。

【解決手段】複数の第1の開口を有するコア絶縁膜を半導体基板上に形成し、複数の第1の開口の側面を導電膜で覆う、シリンダ状の複数の下部電極を形成し、少なくとも複数の下部電極間のコア絶縁膜の上面を覆うサポート膜を形成し、サポート膜を用いて少なくとも複数の下部電極が形成される領域の外側を除去したマスク膜を形成し、マスク膜を形成した後、複数の下部電極間の一部にコア絶縁膜が残るように、コア絶縁膜に対して等方性エッチングを行うものである。

(もっと読む)

141 - 160 / 1,567

[ Back to top ]