Fターム[5F083PR33]の内容

Fターム[5F083PR33]の下位に属するFターム

RTA (917)

Fターム[5F083PR33]に分類される特許

1,761 - 1,779 / 1,779

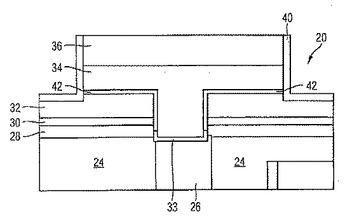

超小型電子デバイスにおいて導電ワイヤの周囲のライナとして磁界コンセントレータを製造する方法

【課題】 書き込み磁界をMTJの自由層に集中させる磁気ライナ形状を効率的に生成することができる方法を提供する。

【解決手段】 MRAMセルにおいて、書き込み電流を低リラクタンス材料内に閉じ込める。この材料を、いくつかの方法のうち1つで処理して、保存要素に最も近い材料を無効として磁束を伝達し、これによって、磁束を保存要素へと集中させるU字形の断面を達成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 強誘電体キャパシタを水素から保護する。

【解決手段】 下地膜8上に、下部電極10a、強誘電体膜10b及び上部電極10cをこの順に積層した強誘電体キャパシタ10を形成する工程と、強誘電体キャパシタ10の上面及び側面を、水素バリア膜11で覆う工程と、水素バリア膜11上及び下地膜8上に第1の層間絶縁膜12を形成する工程と、第1の層間絶縁膜12上に上部SBT膜13を形成する工程と、上部SBT膜13上に第2の層間絶縁膜14を形成する工程とを具備する。下地膜8上に下部SBT膜を形成する工程を更に具備してもよい。この場合、強誘電体キャパシタ10は下部SBT膜上に形成される。

(もっと読む)

半導体装置の製造方法

【課題】 セルトランジスタの拡散層に接続された多結晶シリコン電極と、周辺回路トランジスタの拡散層に接続された金属電極とを備え、多結晶シリコン電極が形成された拡散層の接合リーク電流が抑制され、これによって、良好な情報保持特性を有する半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、多結晶シリコン電極に接続された拡散層を有するトランジスタを形成する工程と、980〜1020℃の基板温度で熱処理する第1の高温熱処理工程(工程A2)と、700〜850℃の基板温度で熱処理する第1の低温熱処理工程(工程A3)とをこの順に有する。

(もっと読む)

半導体装置及びその製造方法

【課題】リーク電流を改善した高誘電率絶縁膜を電極間絶縁膜として使用する半導体装置及びその製造方法を提供することである。

【解決手段】半導体装置は、半導体基板上に形成された第1の絶縁膜と、前記第1の絶縁膜上に形成された第1のゲート電極と、前記第1のゲート電極の上方に形成された第2のゲート電極と、前記第1のゲート電極と第2のゲート電極との間に挟まれた結晶化した第2の絶縁膜を具備することを特徴とする。

(もっと読む)

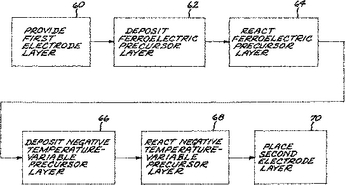

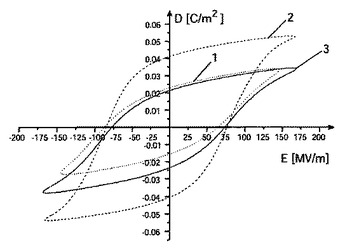

温度補償された強誘電キャパシタ装置およびその製造方法

温度補償されたキャパシタ装置20は、強誘電特性を有し、金属酸化物の強誘電材料のような強誘電材料を使用する強誘電キャパシタ22と、金属酸化物の常誘電材料のような負の温度係数のキャパシタンス材料を使用する負の温度可変キャパシタ24と、負の温度可変キャパシタ24と強誘電キャパシタ22との間の電気的に直列の接続26とを含んでいる。温度補償されたキャパシタ装置20は間にディスクリートな電気接続を有する集積された積層構造または別々のキャパシタとして形成されることができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 マスクの枚数を増加することなく、かつ、汚染することなく膜厚の異なるゲート絶縁膜を備えた半導体装置の製造方法を提供する。

【解決手段】 メモリセル領域Mに複数のアシストゲート電極部21が互いに間隔を隔てて形成される。周辺回路領域Pでは平坦な半導体基板1の表面が露出する。次に、所定の条件のもとで、露出している半導体基板1の表面に酸化処理が施される。平坦な周辺回路領域Pに露出する半導体基板1の表面に供給される酸素ラジカルの量と比べると、メモリセル領域Mでは、アシストゲート電極部21によって挟まれていることで、露出している半導体基板1の表面にまで供給される酸素ラジカルの量は少なくなる。その結果、メモリセル領域Mに形成されるフローティングゲート酸化膜8aの膜厚は、周辺回路領域Pに形成されるゲート酸化膜10の膜厚よりも薄くなる。

(もっと読む)

不揮発性半導体メモリ装置およびその動作方法

【課題】電源電圧相当の電圧でメモリデバイスの閾値電圧を最大限に上昇させる動作を実現する。

【解決手段】半導体基板2とゲート電極6との間に形成され電荷蓄積能力を有する積層膜5を備えるメモリトランジスタ1は、書き込み時と読み出し時とで短チャネル効果が生じているか否かの境界として見積もられるチャネル長Lminが異なり、当該異なるチャネル長Lmin(R)とLmin(W)の間に、実デバイスのチャネル長Lを有する。

(もっと読む)

有機電子デバイスとこの種のデバイスの製造方法

有機電子デバイスは、電極の間に挟まれた1種又は複数の電気活性有機又は高分子材料からなる。このようなデバイスにおいて重要であるのは、電極と高分子との間のインターフェースであり、そこでは、デバイスの正常な機能にとって有害な劣化又は化学反応生成物が生成し得る。これは、直接結合しているか或いは側鎖を通して結合しているホスホネート又はホスフェート官能基を有する分子骨格からなる材料の1種又は複数からなる機能性中間層を導入することによって解決され、前記の機能性の層は、デバイスにおけるそれぞれの電極の少なくとも1つと前記の1種又は複数の電気活性材料との間に配置される。  (もっと読む)

(もっと読む)

重合体中のナノ結晶体を用いるフラッシュメモリ装置

【課題】本発明は、重合体薄膜中に自発形成された金属又は金属酸化物のナノ結晶体を用いた高効率かつ低費用のナノフローティングゲートを有する、フラッシュメモリ素子及びその製造方法に関する

【解決手段】

本発明は、従来のフラッシュメモリ素子のナノ結晶体の形成過程と比較し非常に簡便にナノ結晶体を形成することを可能にする。全体的に均一な分布を有する結晶体であるため、重合体層中に結晶体の凝集現象を伴わずにナノ結晶体の大きさや密度を制御することが可能となる。更に本発明は、従来のナノフローティングゲートと比較し電気的または化学的に安全性を有するナノフローティングゲートを用いることにより、高効率かつ低費用のナノフローティングゲートを有するメモリ素子及びその製造方法を提供する。

(もっと読む)

半導体装置、半導体装置の製造方法

本発明では、水素またはH2Oの拡散を防止することで強誘電体キャパシタの劣化を防止し、高品質の強誘電体キャパシタを有する半導体装置を提供することを課題とする。そのため、本発明では、基板上に形成された強誘電体キャパシタと、前記強誘電体キャパシタ上に形成された配線構造とを有する半導体装置であって、前

記配線構造は、層間絶縁層と当該層間絶縁層中に形成されたCu配線部を含み、前記層間絶縁層に面するように、水素拡散防止層を含むエッチングストッパー層が形成されていることを特徴とする半導体装置を用いた。  (もっと読む)

(もっと読む)

強誘電性ポリマー層のパターニング方法

感光性架橋剤を含んでなる強誘電性スピンコーティング溶液から基材上に強誘電性ポリマーの層をスピンコーティングした後、強誘電性ポリマー層をマスクを通して照射し、強誘電性ポリマー層の非露光部分を除去することにより、例えば二フッ化ビニリデン(VDF)およびトリフルオロエチレン(TrFE)のコポリマーのような強誘電性ポリマーがパターニングされることができる。  (もっと読む)

(もっと読む)

メモリ装置、情報格納処理、処理、及び構造物質

物質(1502)の1又は2以上の領域(1510、1512)への圧力を印加又は除去することによって形成された複数のナノスケールメモリセル(1510、1512)を備えたメモリ装置である。電気伝導読出プローブ(1514)は、前記領域の伝導度及びこれによりセル中に格納された情報を決定する。書込プローブ(1508)は、これらのセルの電気伝導度及びこれによりセル中に格納された情報を変化させるために、選択セルへの圧力の印加又は除去を行う。  (もっと読む)

(もっと読む)

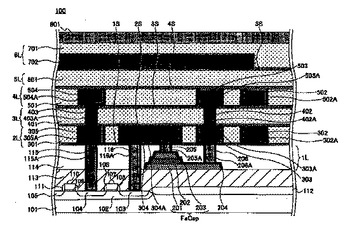

強誘電体キャパシタデバイスおよびFeRAMデバイス

1つ以上のコンタクトプラグが通過して延びている基板と、上記基板上に形成された第1の層間絶縁膜とから、強誘電体キャパシタデバイス(例えばFeRAMデバイス)が形成されている。上記第1の層間絶縁膜上にはスペーサ層が形成されていて、このスペーサ層上には第1の酸素バリア層が形成されていて、この第1の酸素バリア層上にはバッファ層が形成されている。上記バッファ層上において、上記バッファ層と上記コンタクトプラグとの間に下地材料の層が形成されていて、第1の電極と第2の電極との間に誘電体層が挟まれている。上記デバイスに第2の酸素バリア層が塗布される。上記スペーサ層があれば、上記下地材料と上記コンタクトプラグとの界面まで酸化が及ぶことが抑制される。なぜなら、上記界面が、上記第1の酸素バリア層の下に位置しているからである。この結果、電気コンタクトが破損することはない。  (もっと読む)

(もっと読む)

記憶装置用材料及びセル構造

本発明はメモリ用組成物に関し、同組成物と、2つの電極とからなるメモリセルに関する。さらに本発明は、微細電子部品の製造方法及び微細電子部品の製造における本発明の組成物の使用に関する。 (もっと読む)

電荷損失が減少された窒化物層を備えるメモリセル構造及びその製造方法

本発明の一実施形態に従って、半導体基板(210)、半導体基板上に配置された第1シリコン酸化物層(215)、第1シリコン酸化物層上に配置された電荷格納層(220)、電荷格納層上に配置された第2シリコン酸化物層(225)、及び第2シリコン酸化物層上に配置されたゲート層(230)がメモリセル構造に含まれる。例示的な実施形態では、例えば、水素含有量が約0at%〜約0.5at%の範囲に減少されたシリコン窒化物が電荷格納層(220)に含まれる。電荷格納層(220)における水素含有量が減少されることで、結果として電荷損失が減少される。電荷損失が減少された電荷格納層(220)が、メモリデバイスにおける閾電圧シフト、プログラミングデータ損失及びプログラミング性能損失を減少する利点を有し、その結果メモリデバイスパフォーマンスを改善する。  (もっと読む)

(もっと読む)

コンデンサ構造体、でこぼこ状珪素含有面、及びでこぼこ状珪素含有面形成方法

【課題】でこぼこ状珪素含有面の形成方法を提供する。

【解決手段】 非晶質珪素が含まれた層を第一温度に設定された反応室内へ供する。水素同位元素の少なくとも1種を反応室中へ流入させながら、温度を前記第一温度よりも少なくとも40℃高い第二温度まで上昇させる。温度が第二温度まで達したら、前記層へ種子結晶を加える。次いで種子結晶が加えられた層をアニール処理してでこぼこ状珪素含有面を形成させる。でこぼこ状珪素含有面はコンデンサ構造体へ組み入れることができる。このようなコンデンサ構造体をDRAMセル中へ組み入れ、組み入れられたDRAMセルは電子装置に利用可能である。

(もっと読む)

半導体装置の製造方法

【課題】下層のポリシリコン膜を酸化させることなく、酸素アニールによりHTO膜を十分に改質させ、電気的にリークが少ないトンネル酸化膜を形成する半導体装置の製造方法を提供すること。

【解決手段】ポリシリコン膜からなる第1フローティングゲート16上に、窒化膜26又は酸窒化膜28を介してHTO膜を成膜し、酸素アニール処理を施して、トンネル酸化膜18(HTO膜)を形成する。

(もっと読む)

磁気抵抗効果型素子ならびにこれを用いた磁気記憶素子および磁気ヘッド

【課題】 ペロブスカイト型酸化物を用いて良好なトンネル接合を実現し、低磁場でも大きな磁気抵抗効果を発現する磁気抵抗効果型素子を提供する。

【解決手段】 式L2(A1-zRz)2An-1MnO3n+3+xにより表される組成を有し、結晶構造内に(L-O)2層を有する層状ペロブスカイト型酸化物と、この酸化物を挟むようにこれに接して形成された一対の強磁性体と、を含む磁気抵抗効果型素子とする。ただし、AはCa、SrおよびBaから選ばれる少なくとも1種の元素を、LはBi、TlおよびPbから選ばれる少なくとも1種の元素を、MはTi、V、Cu、Ru、Ni、Mn、Co、FeおよびCrから選ばれる少なくとも1種の元素を、Rは希土類元素をそれぞれ示し、nは1、2または3であり、x、zは、それぞれ、−1≦x≦1、0≦z<1により示される範囲内の数値である。

(もっと読む)

半導体装置およびその製造方法

【課題】 強誘電体キャパシタに保護膜を設け、強誘電体膜の還元を抑制する。

【解決手段】 前記保護膜としてAl2 O3 膜を、3.0〜3.1g/cm3 、あるいはそれ以上の密度に形成する。

(もっと読む)

1,761 - 1,779 / 1,779

[ Back to top ]