Fターム[5F083PR34]の内容

Fターム[5F083PR34]に分類される特許

201 - 220 / 917

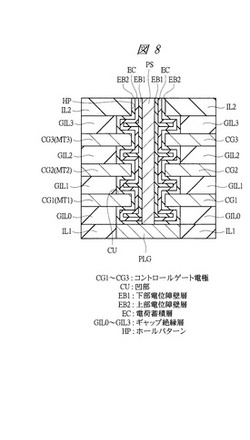

不揮発性半導体記憶装置およびその製造方法

【課題】複数のメモリセルを3次元状に配置し、かつ、メモリセルにMONOS型トランジスタを使用するNAND型不揮発性メモリにおいて、データ保持特性の劣化を抑制することができる技術を提供する。

【解決手段】ギャップ絶縁層GIL1の右端部側に凹部CUが形成されている。このとき、この凹部CUの形状を反映するように、凹部CUの内部に上部電位障壁層EB2と電荷蓄積層ECが形成されており、この凹部CUの形状を反映した電荷蓄積層ECの内側に形成される下部電位障壁層EB1によって、凹部CUが完全に埋め込まれている。このため、凹部CUを埋め込んだ下部電位障壁層EB1の表面は平坦になっており、この平坦になっている下部電位障壁層EB1の内側に柱状半導体部PSが形成される。

(もっと読む)

誘電体膜の形成方法、及びこれを用いる半導体素子のキャパシタの形成方法

【課題】誘電特性及び漏れ電流特性を向上させることのできる半導体素子の誘電体膜の形成方法及びキャパシタの形成方法を提供する。

【解決手段】誘電体膜は、原子層堆積法により、ウェーハ上に酸化ジルコニウム(ZrO2)及び酸化アルミニウム(Al2O3)で構成された誘電体膜を形成する方法であって、チャンバー内に、1つのZrと1つのAl原子とが1つの分子を構成しているソースガスを注入し、ウェーハ上に、ZrO2とAl2O3とからなる[ZrO2]x[Al2O3]y(ここで、x及びyは正数である)膜を形成するステップを繰り返すことにより、ZrO2とAl2O3とで構成された厚さ30Å〜500Åの誘電体膜を形成する。

(もっと読む)

埋め込みビットラインを備えた半導体装置の製造方法

【課題】埋め込みビットラインの抵抗を減少させることができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板201に活性領域203を分離するトレンチ202をエッチングにより形成するステップと、活性領域203の何れか1つの側壁の一部を露出させた開口部207を有する絶縁膜205を形成するステップと、絶縁膜205上にトレンチ202を部分的に埋め込み、開口部207を埋め込むようにシリコン膜パターン208Aを形成するステップと、シリコン膜パターン208A上に金属膜209を形成するステップと、金属膜209及びシリコン膜パターン208Aを反応させて、埋め込みビットラインとなる金属シリサイド膜211を形成するステップとを含む。

(もっと読む)

半導体記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能(不揮発性)で、且つ、書き込み回数にも制限が無い、新たな構造の半導体記憶装置を提供する。

【解決手段】半導体記憶装置に、複数のメモリセルがマトリクス状に配設されたメモリセルアレイと、制御信号に応じて、複数のメモリセルの中から動作を行うメモリセルを選択するデコーダと、デコーダに対して制御信号を出力するか否かを選択する制御回路と、を設ける。なお、複数のメモリセルのそれぞれは、酸化物半導体によってチャネル領域が形成される選択トランジスタをオフ状態とすることによってデータの保持を行う。

(もっと読む)

ジルコニウム酸化膜を有する半導体素子のキャパシタ及びその製造方法

【課題】70nm以下の金属配線を有する次世代DRAMで要求される容量および良好な漏れ電流特性を確保できるキャパシタ及びその製造方法を提供する。

【解決手段】キャパシタ形成方法は、ストレージ電極65を形成するステップと、ストレージ電極65の表面をプラズマ窒化66A処理するステップと、該表面がプラズマ窒化66A処理されたストレージ電極65上にZrO2薄膜67を蒸着するステップと、ZrO2薄膜67の表面をプラズマ窒化処理して、表面が窒化66BされたZrO2薄膜を形成するステップと、窒化66Bされた前記ZrO2薄膜上にプレート電極68を形成するステップとを含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みゲート型トランジスタの電流駆動能力の低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置100は、半導体基板1において素子分離領域5によって複数の活性領域50が区画されると共に、前記半導体基板1内に埋め込まれたワード線8を有する半導体装置100であって、前記ワード線8は、第一の溝部8a内にゲート絶縁膜7aを介して埋め込まれた導電層8bからなり、前記素子分離領域5は、前記第一の溝部8aよりも幅の狭い第二の溝部5aに前記ゲート絶縁膜7bを介して埋め込まれた前記導電層5bからなることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】注入した不純物の拡散を抑制しつつ結晶欠陥を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、リンまたはボロンを分子状イオンの形態で含有する第1の不純物80と、リンまたはボロンよりも注入量が少ない炭素、フッ素または窒素を分子状イオンの形態で含有する、もしくは、リンまたはボロンよりも注入量が少ない炭素を原子イオンの形態で含有する第2の不純物81と、を半導体層1に注入して不純物注入層9を形成する工程を含む。

(もっと読む)

太陽電池

【課題】高温ポストアニールのステップを必要とせず、従来の低温ポリシリコン薄膜トラ

ンジスタと集積可能な、高効率の太陽電池を提供する。

【解決手段】基板と、前記基板上に形成された第1導電層と、前記第1導電層上に形成されたNドープまたはPドープの第1半導体層と、前記第1半導体層上に形成され、複数のレーザー誘起凝集シリコンナノドットを有するシリコンリッチ誘電体層と、前記シリコンリッチ誘電体層上に形成されたNドープまたはPドープの第2半導体層と、前記第2半導体層上に形成された第2導電層と、を含み、前記基板、前記第1導電層、および前記第1半導体層と、前記第2半導体層および前記第2導電層と、のいずれかは、透明材料からなることを特徴とする太陽電池。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】データの保持期間を長くする半導体装置又は半導体記憶装置を提供する。

【解決手段】一対の不純物領域を有する第1の半導体層152aと、第1の半導体層と同じ材料であり、第1の半導体層と離間する第2の半導体層152bと、第1、第2の半導体層の上に設けられた第1の絶縁層153と、第1の絶縁層153を介して第1の半導体層に重畳する第1の導電層154と、第1の絶縁層153を介して第1の導電層に重畳し、第1の半導体層と異なる材料である第3の半導体層156と、第1の導電層及び第3の半導体層に電気的に接続される第2の導電層157bと、第3の半導体層156に電気的に接続され、第2の導電層と同じ材料である第3の導電層157aと、第3の半導体層、第2の導電層、及び第3の導電層の上に設けられた第2の絶縁層158と、第2の絶縁層を介して第3の半導体層に重畳する第4の導電層159と、を含む。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】集積度を向上させた不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1積層構造体と、第1半導体層と、第1有機膜と、第1半導体側絶縁膜と、第1電極側絶縁膜と、を備えた不揮発性半導体記憶装置が提供される。前記第1積層構造体は、第1方向に沿って積層された複数の第1電極膜と、前記複数の第1電極膜どうしの間に設けられた第1電極間絶縁膜と、を有する。前記第1半導体層は、前記複数の第1電極膜の側面に対向する。前記第1有機膜は、前記複数の第1電極膜の前記側面と前記第1半導体層との間に設けられ有機化合物を含む。前記第1半導体側絶縁膜は、前記第1有機膜と前記第1半導体層との間に設けられる。前記第1電極側絶縁膜は、前記第1有機膜と前記複数の第1電極膜の前記側面との間に設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

半導体装置

【課題】パーコレーションリークを抑制可能な構造を有する半導体装置を提供する。

【解決手段】ソース領域18、ドレイン領域18及びチャネル領域を有する半導体領域と、チャネル領域上に形成された第1のトンネル絶縁膜12と、第1のトンネル絶縁膜上に形成され、エネルギー障壁を有する障壁層13と、障壁層上に形成された第2のトンネル絶縁膜14と、第2のトンネル絶縁膜上に形成され、SiY(SiO2)X(Si3N4)1-X (ただし、0≦X≦1、Y>0)で表される絶縁膜を具備する電荷蓄積部15と、電荷蓄積部上に形成され、エネルギー障壁の高さを制御する制御電極17とを備え、X及びYは、[2×2X/(4−2X)+(4−4X)/(4−2X)]×[Y/(Y+7−4X)]≧0.016 なる関係を満たし、障壁層は、クーロンブロッケイド条件を満たす導電性微粒子を含んだ微粒子層で形成されている。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は半導体装置に関する。

【解決手段】本発明は、半導体基板上のセル領域のセルトランジスタ上の層間膜を貫通してコンタクトプラグが形成され、周辺回路領域のトランジスタ上の層間膜を貫通してコンタクトプラグが形成されてなる半導体装置の製造方法であり、セルトランジスタ上の層間膜にコンタクトホールを形成し、その底部側にシリコン膜の下部導電プラグを形成する工程と、その上に金属膜を積層して積層構造のセルコンタクトプラグを形成する工程と、周辺回路用トランジスタ上の層間膜にコンタクトホールを形成し、その内部に金属膜を形成してコンタクトプラグを形成する工程とを具備し、前記セル領域のコンタクトホール内のシリコン膜上に金属膜を形成する工程と前記周辺回路領域のコンタクトホール内に金属膜を形成する工程を同時に行うことを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極GE2の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極GE2側に位置する側壁部において、第1の斜面と、第1の斜面と交差する第2の斜面と、を有する。このように、溝g2の形状をΣ形状とすることで、pチャネル型電界効果トランジスタのチャネル領域に加わる圧縮歪みを大きくすることができる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

半導体記憶装置

【課題】メモリデータを外部回路を用いずに、コピーを行う半導体記憶装置を提供することを課題とする。

【解決手段】複数のメモリセルの第一端子が共通接続されたビット線と、ビット線に接続され、読み出し時にビット線を特定の電位にプリチャージするプリチャージ回路と、メモリセルから読み出したデータ、もしくはメモリセルへの書き込みデータを一時的に保持する容量素子を有するデータ保持回路と、データ保持回路で保持しているデータの反転データをビット線に出力する反転データ出力回路とを有し、反転データ出力回路は、データ保持回路で保持しているデータの反転データの出力を制御する手段を有する構成とする。

(もっと読む)

結晶性酸化物半導体膜の作製方法

【課題】優れた結晶性を有する酸化物半導体膜を作製する。

【解決手段】酸化物半導体の膜を形成するに際し、基板を第1の温度以上第2の温度未満に加熱しつつ、基板の、典型的な長さが1nm乃至1μmの部分だけ、第2の温度以上の温度に加熱する。ここで、第1の温度とは、何らかの刺激があれば結晶化する温度であり、第2の温度とは、刺激がなくとも自発的に結晶化する温度である。また、典型的な長さとは、その部分の面積を円周率で除したものの平方根である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込みワード線に電気的に接続する容量素子またはノイズ除去回路を設けることで、駆動回路等からメモリセルに入力されうる制御信号とは異なる短パルスやノイズ等の信号を低減または除去することができる。これにより、メモリセルが有するトランジスタが瞬間的にオンすることでメモリセルに書き込まれたデータが消失してしまう誤動作を防ぐことが可能である。

(もっと読む)

201 - 220 / 917

[ Back to top ]