Fターム[5F092AA04]の内容

Fターム[5F092AA04]に分類される特許

21 - 40 / 130

電力消費量を削減したMRAMベースのメモリ装置の書き込み方法

【課題】書き込み電力消費量を削減することが可能な磁気トンネル接合部を有するMRAMセルを備えたメモリ装置の書き込み方法を提供する。

【解決手段】ビットラインBLの中の一つにビットライン電圧を印加するとともに、ワードラインWLの中の一つにワードライン電圧を印加して、選定したMRAMセル1の磁気トンネル接合部2に加熱電流を流す工程を有し、このワードライン電圧は、加熱電流の大きさが磁気トンネル接合部2を所定の高さの閾値温度に加熱するのに十分な大きさとなる、MRAMセル1のコア動作電圧よりも高いワードラインオーバードライブ電圧を印加する。

(もっと読む)

記憶素子、記憶素子の製造方法、及び、メモリ

【課題】消費電力化が可能な記憶素子を提供する。

【解決手段】積層方向に電流を流して、スピン偏極した電子を注入することにより、記憶層16の磁化M1の向きが変化して、記憶層16に対して情報の記憶が行われる記憶素子3を構成する。この記憶素子3は、情報を磁性体の磁化状態により保持する記憶層16と、記憶層16に対してトンネルバリア層15を介して設けられている磁化固定層14とを備える。そして、トンネルバリア層15は、厚さが0.1nm以上0.6nm以下であり、且つ、界面ラフネスが0.5nm未満である。

(もっと読む)

磁気抵抗効果素子及び磁気メモリ

【課題】磁化方向が膜面垂直方向に安定であり、磁気抵抗変化率が制御された磁気抵抗効果素子及びその磁気抵抗効果素子を用いた磁気メモリを提供する。

【解決手段】磁気抵抗効果素子を構成する強磁性層106,107の材料を、3d遷移金属を少なくとも1種類含んだ強磁性材料で構成することで、磁気抵抗変化率を制御し、且つ、強磁性層の膜厚を原子層レベルで制御することで磁化方向を膜面内方向から膜面垂直方向に変化させた。

(もっと読む)

不揮発性半導体メモリ及びその製造方法

【課題】不揮発性半導体メモリのリーク電流を削減する。

【解決手段】本発明の一態様に係る不揮発性半導体メモリ1は、複数のワード線WL0〜WLnと、複数のワード線WL0〜WLnと交差する複数のビット線BL0〜BLmと、複数のワード線WL0〜WLnと複数のビット線BL0〜BLmとの交差部のそれぞれに対して備えられており、第1のダイオード5aと抵抗変化型記憶素子5bとを含む複数のメモリセル5と、複数のビット線BL0〜BLmと交差するダミーワード線DWLと、複数のワード線WL0〜WLnと交差するダミービット線DBLと、ダミーワード線DWLと複数のビット線BL0〜BLmとの交差部、及び、ダミービット線DBLと複数のワード線WL0〜WLnとの交差部のそれぞれに対して備えられており、それぞれが第2のダイオード6aを含む複数のダミーセル6とを具備する。

(もっと読む)

減電圧の入出力デバイス(REDUCEDVOLTAGEINPUT/OUTPUTDEVICE)を有する抵抗ベースメモリ

減電圧のI/Oデバイスを含む抵抗ベースメモリが開示される。特定の一実施形態では、回路は、第1の抵抗メモリセルおよび第1の負荷トランジスタを含むデータ経路を含む。基準経路は、第2の抵抗メモリセルおよび第2の負荷トランジスタを含む。第1の負荷トランジスタおよび第2の負荷トランジスタは、回路内のコアトランジスタのコア供給電圧と同等の負荷供給電圧で動作するように構成された入出力(I/O)トランジスタである。  (もっと読む)

(もっと読む)

マルチフェロイックス素子

【課題】 既に市場で大量に生産されているM(マグネトプラムバイト)型フェライト磁石により、外部磁場で電流を誘起でき、外部磁場で電気分極の強度や方向を制御でき、また、外部電場で誘起した磁化の強度や方向を制御でき、且つ、室温の動作環境温度において動作可能なマルチフェロイックス素子を提供する。

【解決手段】 M(マグネトプラムバイト)型フェライトからなる強誘電性と強磁性を合わせもつマルチフェロイックス固体材料で、室温の動作環境温度において外部磁場を作用させることにより電流を誘起する。例えば、マルチフェロイックス素子は、BaFe12-x-δScx MgδO19(δ=0.05)結晶材料のSc濃度xが1.6から2であるマルチフェロイックス固体材料1とそれを挟むように形成される金属電極2とからなる構造を有し、金属電極2に平行に交流磁界5を印加するように配置され、金属電極2間に誘起される電流を利用する。

(もっと読む)

磁性層を備えたトラック及びそれを備える磁性素子

【課題】磁性層を備えたトラック及びそれを備える磁性素子を提供する。

【解決手段】複数の磁区及びそれらの間に磁壁を有するトラックと、前記トラックに連結された磁壁移動手段と、前記トラックについての情報の再生及び記録のための読み取り/書き込み手段と、を備え、前記トラックは、前記磁区及び磁壁を有する磁性層と、前記磁性層の第1面に備えられた第1非磁性層と、前記磁性層の第2面に前記第1非磁性層と異なる物質で形成され、原子番号が14以上である金属及びマグネシウムのうち少なくとも一つを含む第2非磁性層と、を備える磁性素子である。かかる構造に起因して、磁性層は、高い非断熱係数(β)を有する。磁性素子は、例えば、情報保存素子(メモリ)である。

(もっと読む)

磁気ランダムアクセスメモリを製造するシステムおよび方法

磁気ランダムアクセスメモリを製造するシステムおよび方法が開示される。特定の一実施形態では、磁気トンネル接合メモリシステムを作製する方法は、金属層の一部分を、ほぼ直線の部分を有する無分岐のソースラインの中に形成するステップを含む。この方法はまた、ソースラインをほぼ直線の部分で、第1のビアを使用して第1のトランジスタに結合するステップを含む。第1のトランジスタは、ソースラインから受け取った第1の電流を第1の磁気トンネル接合デバイスに供給するように構成される。この方法は、ソースラインを、第2のビアを使用して第2のトランジスタに結合するステップを含み、第2のトランジスタは、ソースラインから受け取った第2の電流を第2の磁気トンネル接合デバイスに供給するように構成される。  (もっと読む)

(もっと読む)

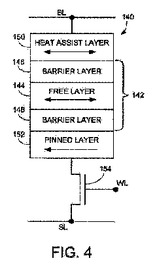

静磁場によりアシストされた抵抗性検知素子

スピン注入型ランダムアクセスメモリ(STRAM)等の不揮発性メモリセル(140,154)にデータを書込むための装置および関連する方法。いくつかの実施例に従うと、抵抗性検知素子(RSE)(140)は、ヒートアシスト領域(150)、磁気トンネル接合(MTJ)(142)およびピン止め領域(152)を有する。スピン分極された電流を用いてMTJに第1論理状態が書込まれるとき、ピン止め領域およびヒートアシスト領域は、各々、実質的にゼロの正味磁気モーメントを有する。静磁場を用いてMTJに第2論理状態が書込まれるとき、ピン止め領域は実質的にゼロの正味磁気モーメントを有し、ヒートアシスト領域は非ゼロの正味磁気モーメントを有する。  (もっと読む)

(もっと読む)

電流誘起スピン−運動量移動に基づく高速低電力磁気デバイス

スピン偏極電流を使用してメモリセルの磁気デバイスにおける磁気領域の磁化方向及び/又はヘリシティを制御してスイッチングする高速かつ低電力の方法。磁気デバイスは、固定の磁気ヘリシティ及び/又は磁化方向を有する基準磁化層と、可変の磁気ヘリシティ及び/又は磁化方向を有する自由磁化層とを含む。固定磁化層及び自由磁化層は、非磁化層により分離されることが好ましい。固定及び自由磁化層は、層法線に対して実質的に非ゼロ角度の磁化方向を有することができる。デバイスに電流を印加してトルクを誘起することができ、これは、デバイスの磁気状態を変更し、そのためにそれは情報を書き込むための磁気メモリとして作用することができる。デバイスの磁気状態に依存する抵抗が測定されてデバイスに格納された情報を読み出す。 (もっと読む)

混合器および周波数変換装置

【課題】永久磁石を使用しつつ低いローカルパワーで作動可能な混合器を提供することを主目的とする。

【解決手段】磁化固定層、磁化自由層、および磁化固定層と磁化自由層との間に配設された非磁性スペーサー層を備えた磁気抵抗効果素子2と、磁化自由層に磁場Hを印加する磁場印加部3とを備え、高周波の信号S1およびローカル信号S2を入力したときに磁気抵抗効果素子2によって両高周波信号S1,S2を乗算して乗算信号S3を生成する。この場合、磁場印加部3は、温度係数が異なり、かつ残留磁束密度の温度変化量が同等の2種の永久磁石31,32が磁化方向を互いに逆向きとした状態で磁場Hの方向に沿って直列に配設されて構成されている。

(もっと読む)

半導体装置

【課題】ホール素子が形成された半導体装置において磁力線の検出感度を高める。

【解決手段】半導体基板10の半導体層11の表面に、定電流が供給される1対のコンタクト部12A,12Bを含むホール素子20が形成されている。ホール素子20は薄い第1の絶縁膜13に覆われており、その第1の絶縁膜13上には、1対のコンタクト部12A,12Bの間の領域11Aを覆う第1の金属層15が形成されている。また、第1の金属層15の一部上に開口部16Aを有して、第1の絶縁膜13及び第1の金属層15を覆うようにして、第2の絶縁膜16が形成されている。第2の絶縁膜16上には、開口部16A内で第1の金属層15と接続されると共に、当該第1の金属層15よりも広く延在する第2の金属層17が形成されている。第1の金属層15及び第2の金属層17の比透磁率は、いずれも、第2の絶縁膜16の比透磁率よりも大きい。

(もっと読む)

スピン伝導素子

【課題】スピンの散乱を抑制しつつ、良好なスピン伝導性及び電気抵抗特性を実現可能なスピン伝導素子を提供すること。

【解決手段】スピン伝導素子100Aは、半導体材料からなるチャンネル7と、チャンネル7上に第1絶縁層81を介して配置された磁化固定層12Bと、チャンネル7上に第2絶縁層82を介して配置された磁化自由層12Cと、チャンネル7上に配置された第1電極20A及び第2電極20Dと、を備え、チャンネル7のうちの第1絶縁層81との接触面を含む第1領域71、第2絶縁層82との接触面を含む第2領域72、第1電極20Aとの対向面を含む第3領域74、及び第2電極20Dとの対向面を含む第4領域75のキャリア濃度は、チャンネル7全体の平均のキャリア濃度よりも高いことを特徴とする。

(もっと読む)

スピン素子を使用した弛緩発振器

【課題】スピン素子を使用した弛緩発振器を提供する。

【解決手段】弛緩発振器は、電源を印加する電源部と、該電源部から印加される電源によって駆動されるスピン素子と、該スピン素子に並列に連結されるキャパシタとを含む。スピン素子は、磁場の強さによって可変な可変電圧値を有する。キャパシタは、前記スピン素子が臨界電圧範囲の最小電圧値を有すると放電し、スピン素子が前記臨界電圧範囲の最大電圧値を有すると充電する。従って弛緩発振器は、製作に必要な部品の個数が少なくて回路が単純化され、製造費用と消費電力が少ない。よって弛緩発振器は、広範囲な周波数帯域の調節が可能で活動範囲が広く、磁化反転を使用することによって高出力が可能であるという効果がある。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】 ビットラインにプリチャージされる電圧をデータに応じて異なるようにし、プリチャージ動作を行なうことのできる半導体メモリ装置を提供すること。

【解決手段】本発明に係る半導体メモリ装置は、ソースラインおよびビットラインを介して流れる電流の方向に対応する極性のデータが保存される複数のメモリセル410と、前記データが複数の前記メモリセルに保存される前にプリチャージ信号PREに応答し、前記ビットラインを前記データに対応する電圧でプリチャージするプリチャージ駆動手段450とを備える。

(もっと読む)

磁性膜を用いた信号処理デバイスおよび信号処理方法

【課題】低消費電力で、多入力信号の加算処理に優れた信号処理デバイスおよび信号処理方法を提供することを可能にする。

【解決手段】少なくとも1層以上の磁性層を含む連続膜10と、連続膜上に、連続膜に直接に接触するかまたは絶縁層を介して接触するように設けられ、前記連続膜との接触面の形状はドット形状であり、入力信号を受けることにより、連続膜との接触面直下の、連続膜の磁性層の領域にスピン波を発生させる複数のスピン波発生部201〜20nと、連続膜上に設けられ、スピン波発生部によって発生されられて連続膜を伝播するスピン波を電気信号として検出する少なくとも1個の信号検出部30と、を備えている。

(もっと読む)

磁性メモリデバイス、および磁性メモリデバイスにおけるデータ読み出し方法

【課題】複数の磁性層を含む磁性メモリセルに対するデータの書き込み/読み出しを行う磁性メモリデバイス、およびそのデータ読み出し方法に関し、磁性メモリデバイス全体の消費電力の節減を図ることを目的とする。

【解決手段】複数の磁性層を積層して形成される磁性メモリセルMijが、複数の磁性層の磁気モーメントの方向によって異なる抵抗値を有し、複数の磁性メモリセルを複数の第1のラインと、第1のラインと交差する複数の第2のラインとの交点に沿って配置し、各々の磁性メモリセルの容量値とほぼ同一の容量値を有する電圧読み出し手段8を、各々の磁性メモリセルに直列に接続し、第1および第2のラインにより選択される磁性メモリセルの一端と電圧読み出し手段との接点の過渡状態の電位を、予め定められたタイミングで計測して得られる電圧のレベルを判定し、磁性メモリセルのデータを読み出すように構成される。

(もっと読む)

磁界検出装置および磁界検出方法

【課題】消費電力が小さくかつ磁界の検出精度の高い磁界検出装置および磁界検出方法を提供する。

【解決手段】トンネル磁気抵抗効果素子10の下部電極17にバイアス電流Ibを流す。これによって、別途バイアス電流用の配線層を設ける場合に比べて、より少ない消費電力でバイアス磁界をトンネル磁気抵抗効果素子に印加することができる。また、外部磁界に応じてバイアス磁界の大きさを変化させることによって、磁界検出精度を向上させることができる。

(もっと読む)

不揮発性磁気メモリを使用している低電力電子システム

コンピューティングシステムが少なくとも1つの機能的ユニット及び少なくとも1つの機能的ユニットに接続された磁気ランダムアクセスメモリ(MRAM)ブロックを含む。MRAMブロックは少なくとも1つの機能的ユニットのパワーダウン状態の間、少なくとも1つの機能的ユニットの機能的状態を格納するように構成される。  (もっと読む)

(もっと読む)

磁気抵抗素子及び磁気メモリ

【課題】記録層が磁化反転する際の反転電流を低減することを可能にする。

【解決手段】電圧を印加することによって格子が伸縮する圧電層11と、圧電層上に設けられ、かつ膜面に垂直方向の磁気異方性を有しスピン偏極した電子の作用により磁化の方向が変化する記録層12と、記録層上に設けられた第1の非磁性層13と、第1の非磁性層上に設けられ、かつ膜面に垂直方向の磁気異方性を有する参照層14と、を備え、記録層は、読み出し時の電圧印加時での熱擾乱耐性が書き込み時の電圧印加時での熱擾乱耐性よりも大きい。

(もっと読む)

21 - 40 / 130

[ Back to top ]