Fターム[5F092AB06]の内容

Fターム[5F092AB06]の下位に属するFターム

マトリックス型 (149)

選択トランジスタを有するもの (815)

Fターム[5F092AB06]に分類される特許

141 - 160 / 470

磁気渦記憶装置

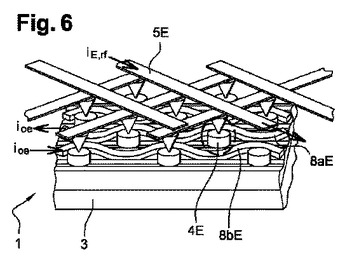

本発明は、渦状態の平面磁気セル(4)のネットワークを含む磁気記憶装置(1)であって、各セルの渦コアが、反対方向でありかつセル(4)面に垂直な第1と第2の平衡位置のいずれかの磁化を有し、2つの位置のそれぞれが2進情報を表す、磁気記憶装置(1)に関する。装置(1)は、セルに格納される2進情報を書き込む手段(5、8a、8b、3)であって、各セル(4)の近傍で前記セル(4)面にほぼ垂直な第1のバイアス静磁場と前記セル(4)にほぼ平行な直線偏波無線周波数磁場とを選択的に印加する手段を含む書き込み手段(5、8a、8b、3)を含む。説明の装置はまた、点接触(7)により渦コアの周囲の領域を介し電流線を導くことにより、2つの交差する電極(6)と(9)間の選択的輸送測定を使用して、好ましくは共振的に極性を読み取る手段を含む。  (もっと読む)

(もっと読む)

スピン伝導デバイス

【課題】磁化自由層、磁化固定層、及びトンネル絶縁層の金属原子がチャンネル層へ拡散することを抑制し、良好な特性を有するスピン伝導デバイスを提供すること。

【解決手段】スピン伝導デバイス100は、チャンネル層と、チャンネル層上に設けられ、酸化アルミニウム、酸化チタン、酸化亜鉛、及び酸化ベリリウムのうちのいずれか一つを含む金属酸化物層8と、金属酸化物層8上に設けられた酸化マグネシウム層9と、酸化マグネシウム層9の第一の部分上に設けられた磁化自由層12Cと、酸化マグネシウム層9の第二の部分上に設けられた磁化固定層12Bと、を備えることを特徴とする。

(もっと読む)

スピントランジスタ、このスピントランジスタを備えたリコンフィギャラブル論理回路および磁気メモリ

【課題】電子と正孔の相互作用による、磁化方向が略平行なときの電流IDPと、磁化方向が略反平行なときの電流IDAPとの差の絶対値の減少を抑制することを可能にする。

【解決手段】表面にn型の半導体領域が設けられた半導体基板10と、半導体領域上に離間して設けられたソース電極30aおよびドレイン電極30bであって、ドレイン電極は半導体領域上に設けられ半導体領域の半導体よりもバンドギャップが大きくかつ価電子帯端が半導体領域の半導体の価電子帯端よりも低いエネルギーを有するn型の第1半導体層31bと、第1半導体層上に設けられた第1強磁性層34bとを有し、ソース電極は半導体領域上に設けられた第2強磁性層34aを有する、ソース電極およびドレイン電極と、ソース電極とドレイン電極との間の半導体領域に設けられたゲート電極24と、を備え、第1および第2強磁性層のうちの一方は磁化方向が不変であり、他方は磁化方向が可変である。

(もっと読む)

情報保存装置及びその動作方法

【課題】情報保存装置及びその動作方法を提供する。

【解決手段】情報保存装置及びその動作方法に係り、該情報保存装置は、バッファトラック及びこれに連結された複数の保存トラックを含む磁性構造体;磁性構造体に備わった書込み/読取りユニット;バッファトラック、複数の保存トラック及び書込み/読取りユニットにそれぞれ連結された複数のスイッチング素子を含む。該バッファトラックと複数の保存トラックとに連結されたスイッチング素子は、同じ信号ラインに連結されうる。該磁性構造体と書込み/読取りユニットとのうち、少なくとも一つに電流を印加するための回路部がさらに備わりうる。

(もっと読む)

磁気トンネル接合素子、磁気ランダムアクセスメモリ

【課題】MTJ素子のMR比を向上させること。

【解決手段】MTJ素子(1)は、第1磁性層(10)と、第2磁性層(20)と、第1磁性層(10)と第2磁性層(20)との間に位置するトンネルバリア層(30)と、ハーフメタル材料で形成された第1ハーフメタル層(40)と、を備える。第1ハーフメタル層(40)は、第1磁性層(10)とトンネルバリア層(30)との間に介在し、トンネルバリア層(30)と接触し、第1磁性層(10)と磁気的に結合する。

(もっと読む)

磁気記憶デバイスの製造方法及び磁気記憶装置

【課題】磁壁移動型の磁気記憶装置に使用する磁気細線の製造時に、磁気細線のフリー層とバリア層の境界部に発生するラフネスを低減して読出し素子の出力を増大する。

【解決手段】強磁性材料からなるデータ記録用の磁気細線1に、データ読出部と、データ書込部を配置した磁気記憶デバイスを製造する際に、シード層11、ホウ素を添加したフリー層12、バリア層13、及びピンド層14をこの順に積層し、この状態で熱処理を行ってフリー層12に添加されたホウ素を拡散除去することによって磁気細線1を形成し、形成した磁気細線1の上にデータ読出部とデータ書込部を形成して磁気記憶デバイスを製造する方法である。このデバイスを複数個並列に接続すれば磁気記憶装置となる。

(もっと読む)

共に結合された2つ以上の基板から形成された電子デバイス、電子デバイスを備える電子システム、及び、電子デバイスの製造方法

電子デバイスは、第1の基板及び第2の基板を備える。第1の基板は、第1の基板の少なくとも一部を介して相互に少なくとも実質的に平行な複数の導電性トレースを含む回路を備える。複数のボンドパッドは、第1の基板の表面上に配置されるとともに、複数の導電性トレースの少なくとも2つの上に延在する幅を持つ。複数のビアは、少なくともいくつかの導電性トレースの隣接部から複数のボンドパッドまで延在する。第2の基板は、第1の基板に結合されるとともに、複数の導電性バンプを有する第1の基板上の複数のボンドパッドに接続される回路を備える。更に、メモリデバイスと、電子デバイス及びメモリデバイスを形成する関連方法とが開示され、同様に電子システムも開示されている。 (もっと読む)

磁性発振素子

【課題】高出力及び長寿命で、発振周波数が安定な磁性発振素子を提案する。

【解決手段】本発明の磁性発振素子は、磁化方向が可変の磁気フリー層1と、磁化方向が不変の磁気ピンド層3と、両者間に配置されるスペーサー層2と、磁気フリー層1に外部磁場を与える磁場発生部7とを備える。磁気フリー層1は、一軸磁気異方性を有し、それに発振閾値電流よりも大きな電流が流れることにより磁化振動を行う。磁場発生部7は、磁化振動による反磁場に起因する発振周波数のシフト量と磁気フリー層1の一軸磁気異方性による磁場に起因する発振周波数のシフト量とを相殺する方向に外部磁場の大きさ及び方向を制御する。磁気フリー層1の磁化振動の中心となる方向と磁気ピンド層3の磁化方向とのなす角度θは、0°≦θ≦70°及び110°≦θ≦180°の範囲内にある。

(もっと読む)

スピン流回路

【課題】複数の出力電圧のバラつきを低減可能なスピン流回路を提供する。

【解決手段】スピン流回路は、スピン流を発生する第1スピン注入素子SIEと、第1スピン注入素子SIEにおいて発生したスピン流が流れる非磁性のチャンネル層5Aと、チャンネル層5A上の異なる位置に設けられた複数の磁化自由層4,6と、チャンネル層5Aとそれぞれの磁化自由層4,6との間に介在するトンネル障壁19B,19Cとを備えている。それぞれの磁化自由層4,6とチャンネル層5Aの間の電圧が、それぞれ検出される。各フリー層4,6とチャンネル層5Aとの間にトンネル障壁19B,19Cを介在させておくことで、各フリー層4,6とチャンネル層19B,19Cとの間の出力電圧のバラつきを低減させることができる。

(もっと読む)

スピントランジスタ及びその製造方法

【課題】効率的なスピン偏極電流の注入が可能で低抵抗な電極構造を有するスピントランジスタ及びその製造方法を提供する。

【解決手段】半導体基板上にソース及びドレイン電極並びにゲート電極を備え、ソース及びドレイン電極の少なくとも一方は以下の構成を有する。半導体領域12にはn+型半導体領域12A,12Bが形成されている。n+型半導体領域12A,12B上には、コバルト(Co)あるいは鉄(Fe)の少なくとも一方を含む結晶質のホイスラー合金を含む磁性層31が形成されている。n+型半導体領域12A,12B及び磁性層31は同一の不純物元素を含んでいる。

(もっと読む)

トンネル型磁気検出素子

【課題】 特に、フリー磁性層の磁歪λsの増加を小さく抑えつつ、従来に比べて抵抗変化率(ΔR/R)を増大させることが可能なトンネル型磁気検出素子を提供することを目的としている。

【解決手段】 絶縁障壁層5は、Mg−Oで形成され、前記フリー磁性層6は、下からエンハンス層12、第1軟磁性層13、Co−Ta層14及び第2軟磁性層15の順に積層されている。このように軟磁性層13,15間にCo−Ta層14を挿入した構成とすることで、フリー磁性層6の磁歪λsの増加を小さく抑えつつ、従来に比べて抵抗変化率(ΔR/R)を増大させることが可能である。

(もっと読む)

トンネル型磁気検出素子

【課題】 特に、抵抗変化率(ΔR/R)を増大させることが可能なトンネル型磁気検出素子を提供することを目的としている。

【解決手段】 第1軟磁性層13と第2軟磁性層15との間に、Ti、Mg、Ir−Mn、RuあるいはPtのうち少なくともいずれか1種で形成された金属挿入層14が挿入されている。前記第1軟磁性層13と前記第2軟磁性層15は、磁気的に結合されて同一方向に磁化されている。前記第1軟磁性層13と絶縁障壁層5との間にはエンハンス層12が形成されている。これにより、絶縁障壁層5がMg−Oで形成されたトンネル型磁気抵抗効果素子において、従来に比べて、抵抗変化率(ΔR/R)を増大させることが可能である。

(もっと読む)

トンネル型磁気検出素子

【課題】 特に、フリー磁性層内にTa層を挿入した形態に比べて、上下シールド層間のギャップ長(GL)を小さくしつつ抵抗変化率(ΔR/R)を増大させることが可能なトンネル型磁気検出素子を提供することを目的としている。

【解決手段】 フリー磁性層6は、例えば、Mg−Ti−Oから成る絶縁障壁層5上に、下から、エンハンス層12、第1軟磁性層13、非磁性金属層14、第2軟磁性層15の順に積層されている。前記エンハンス層12は例えばCo−Feで、第1軟磁性層13及び第2軟磁性層15は例えばNi−Feで、非磁性金属層14は例えばTiで形成される。前記エンハンス層12の平均膜厚と前記第1軟磁性層13の平均膜厚を足した総合膜厚T5は19Å以上28Å以下で形成される。これにより従来に比べて安定して高い抵抗変化率(ΔR/R)を得ることが出来る。

(もっと読む)

磁気抵抗素子

【課題】磁気抵抗素子全体の電力消費を低減させる。

【解決手段】磁気抵抗素子は、磁気異方性を示し、その磁化が少なくとも第一及び第二の方向の間で反転できるように構成された強磁性層と、強磁性領域に容量性結合されたゲートとを含んでいる。磁気抵抗素子を動作させる方法は、第一及び第二の方向の間で磁化を反転させるために、強磁性領域の磁気異方性の方向を変化させるように、強磁性領域に電場パルスを印加するステップを含んでいる。

(もっと読む)

磁性構造体、磁性構造体の形成方法、磁性構造体を含む情報記録装置、及びその製造及び動作方法

【課題】磁性構造体、磁性構造体の形成方法、磁性構造体を含む情報記録装置、及びその製造及び動作方法を提供する。

【解決手段】基板に平行な第1方向に延びた第1部分と、第1部分の両端から第1方向に垂直な第2方向に延びた第2部分と、を備え、相互逆方向に磁化した二つの磁区及びそれらの間に磁壁を有する情報記録用磁性構造体である。情報記録用磁性構造体は、U字型または逆U字型である。磁壁は、第1部分内に位置する。情報記録用磁性構造体は、垂直磁気異方性を有する。

(もっと読む)

メモリ素子

【課題】電界によって分極と磁化を誘起し、その強度と方向を制御できるメモリ素子を提供する。

【解決手段】メモリ素子において、マルチフェロイック固体材料1からなる構造を有し、上下の金属電極2,2′に電界を印加するように配置し、上下の金属電極2,2′間に誘起される電荷、磁化を利用する。データの書き込みは、特定の選択されたビット線4とワード線5の間に印加する電圧による電界で分極を発生させることにより実現する。データの読み出しは、保持されている電気分極に起因する電圧強度で0もしくは1を判定すればよい。データの消去は、そのメモリセル3へ印加する電圧の符号を先に印加した電圧と反転させ、一定の強度を与えればよい。一方、分極発生すると同時に磁化6が発生する。この磁化6は磁界7をメモリセル3の外部に及ぼす。このことからメモリセル3の情報に相応した磁界を発生し得るアクティブ型メモリ素子を提供することができる。

(もっと読む)

磁気抵抗効果素子の磁気抵抗効果率の測定方法

【課題】高精度な測定値の取得が可能な磁気抵抗効果素子の磁気抵抗効果率の測定方法を提供する。

【解決手段】本発明に係る磁気抵抗効果率の測定方法は、固定磁性層の磁化方向を判定するステップと、自由磁性層の磁化方向を判定するステップと、自由磁性層の磁化方向に対して90°より大きく180°より小さく、且つ固定磁性層の磁化方向に対して90°より大きく180°より小さい角度の方向に、強度が0から徐々に増加する外部磁場を印加してρH曲線を得て抵抗最大値を得るステップと、自由磁性層の磁化方向に対して180°より大きく270°より小さく、且つ固定磁性層の磁化方向に対して0°より大きく90°より小さい角度の方向に、強度が0から徐々に増加する外部磁場を印加してρH曲線を得て抵抗最小値を得るステップと、抵抗最大値と抵抗最小値とから磁気抵抗効果率を算出するステップとを備える。

(もっと読む)

情報保存装置及びその動作方法

【課題】情報保存装置及びその動作方法を提供する。

【解決手段】情報保存装置及びその動作方法について開示されている。該情報保存装置は、磁性トラック及び書込み/読取りユニットを含むメモリ領域と、メモリ領域に連結された制御回路部とを含むことができる。磁性トラックの両端にそれぞれ連結された第1スイッチング素子及び第2スイッチング素子が備わり、書込み/読取りユニットに連結された第3スイッチング素子が備わりうる。制御回路部によって、第1スイッチング素子、第2スイッチング素子及び第3スイッチング素子が制御され、磁性トラックと書込み/読取りユニットとのうち、少なくとも一つに動作電流が印加されうる。

(もっと読む)

レーストラック・メモリ・デバイス

【課題】 電子のスピン分極を利用したレーストラック・メモリ・デバイスを提供する。

【解決手段】 レーストラック・メモリ・ストレージ・デバイスは、磁壁をレーストラックに沿って一方向のみに移動させる。読み出し要素は、(レーストラックの中央部よりも)レーストラックの1つの端部に配置することができる。磁壁は、読み出し要素を横切って移動させると消滅するが、それらの対応する情報は、1つ又は複数のメモリ・デバイス(例えば、組み込みCMOS回路)に読み込まれる。次いで、情報は、計算ニーズに対して回路内で処理され、読み出し要素と対向するレーストラックの端部に配置された書き込み要素を用いて、その元の形式(レーストラックから読みだされたときの)か、又は何らかの計算後の異なる形式のいずれかで、レーストラックに書き戻される。こうしたレーストラックは、より単純に構築することができ、従来のレーストラック・メモリ・デバイスよりも動作の信頼性が高い。

(もっと読む)

磁気抵抗効果素子とその製造方法、磁気再生ヘッド、および情報記憶装置

【課題】面積抵抗(RA)を増加させることなく、所定値以上の磁気抵抗効果率(MR比)を確保しつつ、固定磁化層と自由磁化層との間の層間結合磁界(Hin)の低減が可能な磁気抵抗効果素子を提供する。

【解決手段】本発明に係る磁気抵抗効果素子1は、絶縁材料を用いて形成される絶縁層15と、磁性材料を用いて形成される第2の磁化層との間に、非磁性材料を用いて形成される非磁性層20を備え、非磁性層20は、絶縁層15上に形成される。

(もっと読む)

141 - 160 / 470

[ Back to top ]