Fターム[5F092EA04]の内容

Fターム[5F092EA04]の下位に属するFターム

Fターム[5F092EA04]に分類される特許

1 - 20 / 43

半導体装置、および、その製造方法

【課題】電流により発生する磁場を化合物半導体回路で集約して検出することができる小型で、高感度かつ高精度な電流センサを実現すること。

【解決手段】半導体回路(LSI回路)と化合物半導体回路(ホール素子を有する化合物半導体素子)とが形成された基板に、さらに、化合物半導体素子の直上に、該直下の化合物半導回路に対して磁束密度を増加させるための所定の形状からなる電気配線(コ字型または馬蹄型の形状を呈した金属配線)を形成し、この電気配線に被検出電流を流すようにした。

(もっと読む)

電流センサ

【課題】電流値を精度良く検知する。

【解決手段】磁気抵抗素子11を備えた電流センサ10であって、該磁気抵抗素子11の、磁気抵抗素子11自体に流すセンス電流に応じた出力変化(センス電流部12による出力変化)と、磁気抵抗素子の近傍に配置される電気配線(電気配線wd2等の影響による出力変化)への電流に応じた出力変化と、の2つの出力変化に基づいて測定対象である負荷Aへの電流を測定する。

(もっと読む)

磁気センサ

【課題】 動作点の変動と抵抗値比のばらつきを抑制することができると共に、温度特性を改善した磁気センサを提供する。

【解決手段】 磁気センサ1は、センサ回路部2を備える。このセンサ回路部2は、第1および第3の磁気抵抗素子R1,R3を直列接続した第1の直列回路6と、第2および第4の磁気抵抗素子R2,R4を直列接続した第2の直列回路7とを備え、第1の直列回路6と第2の直列回路7とを並列接続したブリッジ回路5によって構成される。第1ないし第4の磁気抵抗素子R1〜R4の表面は絶縁膜12によって覆われる。また、第3の磁気抵抗素子R3および第4の磁気抵抗素子R4の表面には、絶縁膜12を挟んで磁性材料からなる磁束集磁膜13が形成される。

(もっと読む)

磁気抵抗効果素子及びこれを用いた磁気センサ

【課題】MR素子の消費電力を低減する。

【解決手段】MR素子10は、基板11と、基板11上に設けられたMR膜12とを備えている。MR膜12は、ジグザグ状に折れ曲がる直線12aが更に多重にジグザグ状に折れ曲がる形状12bを有する。直線12aは、複数の形状部121,122,123を形成している。それぞれの形状部121,122,123は、互いに平行な複数の長方形12cがジグザグ状に直列に接続された形状を有し、かつジグザグ状に互いに直列に接続されている。

(もっと読む)

磁気センサ装置およびその製造方法

【課題】1つの基板に形成した複数の磁気抵抗素子部のピン磁性層を任意の方向に着磁させたとしても、磁気抵抗素子部の検出精度の低下を防止する。

【解決手段】基板10に各磁気抵抗素子部22に対応するヒータ部30をそれぞれ形成し、ヒータ部30の上方に各磁気抵抗素子部22を形成する。磁場の向きが基板10の一面13の面方向のうちの第1の方向に設定された磁場中において、一方の磁気抵抗素子部22に対応するヒータ部30を加熱して磁場中アニールを行い、当該磁気抵抗素子部22を構成するピン磁性層22aの磁化の向きを第1の方向に着磁する。続いて、磁場の向きを第1の方向とは異なる第2の方向に設定した磁場中において、他方の磁気抵抗素子部22に対応するヒータ部30を加熱して磁場中アニールを行い、当該磁気抵抗素子部22を構成するピン磁性層22aの磁化の向きを第2の方向に着磁する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】基板の反射率に依存せず、アライメントマークの識別性を確保することができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、シリコン基板24と、シリコン基板24上に少なくともNiCoパターン31とアルミ電極30とを含んで形成される回路部3と、シリコン基板24上に回路部3のNiCoパターン31と同工程において形成される低反射パターンとしてのNiCoパターン22と、NiCoパターン22上に形成され、回路部3のアルミ電極30と同工程において形成される高反射パターンとしてのアルミパターン20とを有する。

(もっと読む)

マイクロコンピュータ周辺装置、初期設定方法、半導体集積装置

【課題】半導体集積回路装置におけるマイクロコンピュータ周辺装置の高速起動。

【解決手段】マイクロコンピュータ周辺装置は、マイクロコンピュータから受信した初期設定コマンドに基づく設定信号をレジスタを介して機能回路部に出力し、初期設定を行う。ここで、レジスタにおける設定信号のデータをMTJ素子等の不揮発性記憶素子を用いた保持回路で記憶しておく。電源再投入時には、保持回路に記憶された設定信号のデータで初期設定を行う。

(もっと読む)

半導体記憶装置

【課題】半導体基板の表面の空き領域が少ない半導体記憶装置を提供する。

【解決手段】このMRAMの各メモリセルMCは、磁気抵抗素子18と2つのアクセストランジスタ19a,19bを含み、トランジスタ19a,19bのドレインを磁気抵抗素子18を介して対応のビット線BLに接続し、それらのゲートを対応のワード線WLに接続し、それらのソースをそれぞれソース線SLおよび補助配線ALに接続する。したがって、アクセストランジスタ19bのソースとDLドライバ14に含まれるドライバトランジスタ23のソースとを共通化することができ、シリコン基板31の表面の空き領域を減らすことができる。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】データ消失温度が高く、かつ生産性の高い不揮発性記憶装置およびその製造方法を提供することである。

【解決手段】実施形態に係る不揮発性記憶装置の製造方法は、第1の記憶部と、第1の記憶部が有するデータ消失温度よりも高いデータ消失温度を有する第2の記憶部と、を有する不揮発性記憶装置の製造方法であって、第2の記憶部のメモリセルを形成するための第2の積層体を形成する工程と、第1の記憶部が形成される領域に形成された第2の積層体を除去する工程と、第1の記憶部のメモリセルを形成するための第1の積層体を形成する工程と、第2の記憶部が形成される領域に形成された第1の積層体を除去する工程と、第1の記憶部が形成される領域に形成された第1の積層体と、第2の記憶部が形成される領域に形成された第2の積層体と、を同時に処理して、第1の積層体から第1の記憶部のメモリセルを形成するとともに、第2の積層体から第2の記憶部のメモリセルを形成する工程と、を備えている。

(もっと読む)

モータ制御用半導体装置

【課題】モータ制御用半導体装置に対するコンタクト用ピンからの影響を低減する

【解決手段】ホール素子102からの出力のオフセット電圧を取り除くオフセットキャンセル回路104に含まれるオシレータ回路12と、オフセットキャンセル回路104からの出力信号を受けて、当該出力信号と基準信号とを比較して比較信号を生成して出力するコンパレータ回路106と、モータを駆動するための駆動信号を生成して出力する出力回路110と、モータの制御に関係しないテスト回路112と、を有し、オシレータ回路12の回路パターン上、コンパレータ回路106の回路パターン上、及び、テスト回路112の回路パターン上のいずれか1つに重なるようにパルス幅変調信号の入出力パッドP1を形成する。

(もっと読む)

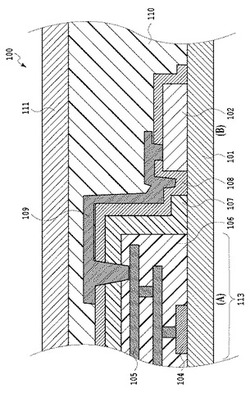

電流検知器を備えた半導体装置

【課題】磁気抵抗効果素子を用いて電流を検知するセンサを備えた半導体装置に関する。簡単な構成により、電流の検出を高精度に実現することを目的にする。

【解決手段】半導体回路が形成された基板と、基板に配設された第1の配線部材と、第1の配線部材に立設された垂直配線部材と、垂直配線部材に接続され第1の配線部材と平行に架設された第2の配線部材と、垂直配線部材に対向配置された第1の磁電変換素子と、垂直配線部材をはさんで第1の磁電変換素子と対向する第2の磁電変換素子と、第1の磁電変換素子と第2の磁電変換素子を直列に接続する第1の素子配線と、第1の素子配線の中点が入力される第1の増幅回路とを備えている。

(もっと読む)

混合器および周波数変換装置

【課題】磁気抵抗効果素子から伝送路に出力される乗算信号の歪みを確実に低減する。

【解決手段】RF信号SRF、およびローカル信号S2を入力すると共に、両信号SRF,S2を加算して加算信号S12として出力する加算部6と、磁化固定層、磁化自由層、および磁化固定層と磁化自由層との間に配設された非磁性スペーサー層を備え、加算信号S12を入力したときに加算信号S12に含まれているRF信号SRFおよびローカル信号S2を磁気抵抗効果によって乗算して乗算信号S4を生成する磁気抵抗効果素子2と、磁化自由層に磁場を印加する磁場印加部3と、磁気抵抗効果素子2から出力される乗算信号S4を入力すると共に、入力インピーダンスよりも低いインピーダンスに変換して出力する受動型の第1インピーダンス変換部7とを備えている。

(もっと読む)

回転センサ

【課題】 回転角度の検出精度を高めながら小型化することができる回転センサを実現する。

【解決手段】 磁気抵抗素子R1〜R8が各磁気抵抗素子の出力信号間に位相差が出るように配置された磁気抵抗素子領域E1と、ホール素子H1,H2が各ホール素子の出力信号間に位相差が出るように配置されたホール素子領域E2とを有し、かつ、磁気抵抗素子領域およびホール素子領域の少なくとも一部同士が重ねられたセンサチップ5と、各ホール素子の各出力レベルと閾値レベルとの比較結果を出す比較部53と、各磁気抵抗素子の各出力信号を用いて相対回転角度θに対応する演算角度φを演算する角度演算部60と、その演算された角度と閾値角度とを比較し、その比較結果と比較部53の比較結果とを用い、相対回転角度に対応する信号を出力する出力部70とを備える。

(もっと読む)

回転センサ

【課題】 磁気発生部の相対回転角度の演算時間を短縮することができる回転センサを実現する。

【解決手段】角度演算部60はAMRセンサM1,M2から出力される信号を用い永久磁石2に対する相対回転角度θと演算により求めた演算角度φとの偏差が所定値に収束するようにフィードバック制御を行って相対回転角度θを演算する。初期値決定部53はホール素子H1,H2から出力された各検出信号の各信号レベルと閾値との各比較結果を用い相対回転角度θの初期値θ0が含まれる角度範囲を判定し、その判定した角度範囲の中で発生し得る相対回転角度の初期値と前記演算角度の初期値との差の絶対値が90°未満となるように演算角度の初期値を決定する。初期値決定部は永久磁石2が相対回転を開始する前にのみ演算角度φの初期値φ0を決定し角度演算部60はその決定された演算角度φの初期値φ0を用いてフィードバック制御を開始し、相対回転角度θを演算する。

(もっと読む)

磁気センサ

【課題】TMR素子などのスピントロニクス素子を用いた磁気センサに関し、ノイズを低減し、かつ、高感度化を図ることができる磁気センサを提供する。

【解決手段】磁気抵抗素子群を用いた磁気センサ20は、検知素子10を直列に接続して磁気抵抗素子群8a、8b、8cとし、これらを並列に配置してセル9として磁気抵抗素子群を連動する。基準抵抗11を直列に配置することにより、磁気抵抗値の変化につれて出力変化を実現する。

(もっと読む)

半導体ウェーハ及びその製造方法

【課題】半導体基板上に形成されたスクライブラインと集積回路部との間の段差を低減することで、集積回路部におけるレジストの塗布ムラを低減することができる半導体ウェーハ及びその製造方法を提供する。

【解決手段】p−Si基板21上に、IC部51、シールリング部52及びスクライブライン53が形成されたシリコンウェーハであり、最上層の絶縁層25bの平坦面上に配線層24cが形成されるとともに、最上層の配線層24cと同一の材料からなる金属層54cがシールリング部52に形成され、配線層24c及び金属層54cを覆うように、IC部51、シールリング部52及びスクライブライン53の全面に亘って表面が平坦化された平坦化絶縁層55が形成され、この平坦化絶縁層55上にパッシベーション膜56が形成され、パッシベーション膜56上にGMR素子6〜9が形成されていることを特徴とする。

(もっと読む)

光磁気一体型センサ及びこれを搭載する電子機器

【課題】光センサと磁気センサの両方を用いる場合の省スペース化。

【解決手段】集積回路内に、磁気検出素子と、印加された磁界に応じて前記磁気検出素子で得られる電圧信号を取り出して磁気検出信号を得る磁気検出信号処理部と、を備える磁気センサ部と、光検出素子と、照射された光量に応じて該光検出素子で得られる電流信号を取り出して光検出信号を得る光検出信号処理部と、を備える光センサ部と、を設け、磁気検出素子と、光検出素子とは、共通の半導体基板に形成し、光磁気一体型センサとする。半導体基板のp導電型領域の上にn導電型領域を形成し、n導電型領域を磁気検出素子として用い、かつp導電型領域とn導電型領域とのpn接合を光検出素子として用いれば、単一のセンサ素子を光検出素子、磁気検出素子として利用することもできる。

(もっと読む)

半導体集積回路装置

【課題】複数のMTJメモリセルアレイを同一チップ内に含む半導体集積回路装置の製造工程を効率化する。

【解決手段】システムLSI100は、複数のMRAM回路ブロック110a〜110fを備える。MRAM回路ブロック110a〜110fは、MTJメモリセルが行列状に配置されるMTJメモリセルアレイ10a〜10fをそれぞれ含む。MTJメモリセルアレイ10a〜10fの各々には、書込データに応じて双方向のデータ書込電流を流すためのビット線BLが配置される。MTJメモリセルアレイ10a〜10fのそれぞれにおけるビット線BLの延在方向は、システムLSI100上で同一方向である。

(もっと読む)

磁気メモリ、磁気メモリアレイおよび磁気メモリアレイへの情報書込み方法

【課題】 読出し時に熱的に安定で、かつ書き込み時の電流を低減した、スピントルク磁化反転応用の磁気ランダムアクセスメモリを提供する。

【解決手段】 強磁性体からなる固定層、非磁性障壁層、強磁性体からなる記録層、記録層と磁気的に結合した強磁性体からなる強磁性付加層が順次積層されたメモリ素子を備え、前記記録層の磁化方向と前記固定層の磁化方向が、略平行か、略反平行かによって情報の検出を行い、さらに前記記録層の磁化の方向を、前記記録層の膜面に垂直な方向に通電するスピン偏極した電流でスイッチングする磁気メモリにおいて、前記強磁性付加層の磁化方向が前記記録層と略平行とし、前記強磁性付加層の磁化の大きさが、150℃から250℃の温度範囲で消失する材料で、前記強磁性付加層を構成する。

(もっと読む)

「論理関数」を実行するための磁気デバイス

本発明は、非強磁性中間層によって分離された第一の強磁性層および第二の強磁性層を含む少なくとも一つの第一の磁気抵抗スタック(MTJ1)、そして第一(N3)および第二(N2)レベルのメタライゼーションに各々属する少なくとも一つの第一(19)および一つの第二(18)の電流ラインからなる磁気構造を含む「論理関数」実行のためのデバイス(9)に関する。二つのラインの各々は、電流がそれを通って流れると第一のスタックの近くに磁場を発生させる。なお、強磁性硬層は、基準として機能する固定磁束に留められる。第一および第二のライン(19、18)は、第二の強磁性層の種々の距離に配置されるが、それら種々の距離は「論理関数」によって決定される。 (もっと読む)

1 - 20 / 43

[ Back to top ]