Fターム[5F101BD07]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | メモリセル(センサ) (3,677) | MOSトランジスタ (3,641) | SD領域 (1,220) | LDD等高耐圧構造(メモリセルの) (599)

Fターム[5F101BD07]に分類される特許

21 - 40 / 599

半導体装置およびその製造方法

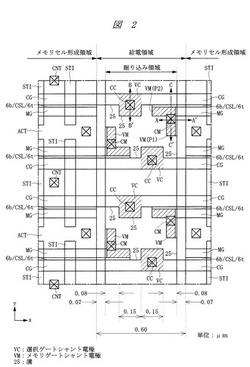

【課題】スプリットゲート構造の不揮発性メモリセルを有する半導体装置において、メモリアレイのレイアウト面積を低減する。

【解決手段】給電領域において、メモリゲートシャント部が形成される領域の素子分離部に溝25が形成されており、選択ゲートシャント部に備わる選択ゲートシャント電極VCは、メモリセル形成領域に形成された選択ゲート電極CGに繋がる第1導電膜からなり、メモリゲートシャント部に備わるメモリゲートシャント電極VMは、給電領域に形成された選択ゲート電極CGの延長部の片側面の一部および素子分離部に形成された溝25の側面の一部に絶縁膜6b,6tおよび電荷蓄積層CSLを介してサイドウォール状に形成され、メモリセル形成領域に形成されたメモリゲート電極MGに繋がる第2導電膜からなる。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】スループットを低下させずに異なるメモリセルの誘電体膜とキャパシタの誘電体膜を同時に形成するための半導体装置の製造方法を提供する。

【解決手段】第1酸化膜18、窒化膜19、第2酸化膜20を順に形成した第1の誘電体膜を第1の半導体膜16上に形成する工程と、第1領域I内の第1の誘電体膜21をエッチングする工程と、第1領域Iの半導体基板1の表面に第3酸化膜25を形成する工程と、第1領域VI及び第2領域IIIに開口部28a、28bを有し、さらに第3領域II内の第1の誘電体膜21を覆う形状を有するマスク28を半導体基板1の上方に形成する工程と、マスク28の開口部28a、28bを通して、第1領域VI内の前記第3酸化膜25と前記第2領域III内の第1の誘電体膜21の第2酸化膜20を同時にエッチングする工程を含む。

(もっと読む)

半導体装置

【課題】浮遊状態の配線と洗浄水との間において高い密度で電荷が移動することに起因する配線の高抵抗化を防ぐ。

【解決手段】半導体製造装置の製造工程中において、半導体基板1Sなどと絶縁された浮遊状態となる銅配線である第1層配線L1の上面に、電気的に機能する接続ビアPL2と電気的に機能しないダミービアDP2とを接続させて形成する。これにより、第1層配線L1の上面に接続ビアPL2を形成するためのビアホールを形成した後の洗浄工程中に、第1層配線L1に溜まった電荷が洗浄水中に移動する際、前記電荷をダミービアDP2形成用のビアホールにも分散させることで、接続ビアPL2形成用のビアホールの底部のみに前記電荷が集中することを防ぐ。

(もっと読む)

半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供する

ことを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウ

ム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて

、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化

物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以

下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有

し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でス

パッタリングを行う。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

半導体装置

【課題】消去特性と消去ディスターブ特性との双方を向上することが可能な、MONOS型メモリセルなどの半導体装置を提供する。

【解決手段】半導体基板SUBの主表面に形成される第1のゲート電極CGと、主表面上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる絶縁膜ONOと、第1および第2のゲート電極CG,MGの真下のチャネル領域を挟むように、主表面に形成される1対のソース/ドレイン領域NR1,NR2とを備える。上記ソース領域NR1は、第1のソース領域N11および第2のソース領域N12を含んでいる。上記第2のソース領域N12は第1のソース領域N11よりも主表面から深い領域に形成されている。上記第1のソース領域N11と第2のソース領域N12とに含まれる不純物の材質が異なっている。

(もっと読む)

半導体メモリの製造方法及び製造装置

【課題】自動的に処理レシピを変更することにより製造歩留を向上させることができる半導体メモリの製造方法及び製造装置を提供する。

【解決手段】計算部が、第2酸化膜厚、第1酸化膜厚、ゲート電極幅、アクティブ領域幅とを含む測定値を受け取り、半導体メモリのセル部の予測電流値を算出する工程(S3)と、プロセス処理実行部が、予測電流値が基準電流値以下であると判断されたときに第1処理レシピを選択し、予測電流値が基準電流値より大きいと判断されたときに第2処理レシピを選択し、第1及び第2処理レシピのうちの選択された処理レシピに従って浮遊ゲート電極の側壁を覆うSWを形成する工程(S4,S5,S6)とを有し、第2処理レシピに従って形成されたSWの第1方向の膜厚である第2のSW膜厚が、第1処理レシピに従って形成されたSDの第1方向の膜厚である第1のSW膜厚よりも大きい。

(もっと読む)

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のトランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電位を保持させることで行う。メモリセルの読み出しは、ビット線にプリチャージ電位を供給した後ビット線への電位の供給を止め、ビット線の電位がプリチャージ電位に保たれるか、または電位が下がるか、により行う。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性半導体装置の高集積化を図ることのできる技術を提供する。

【解決手段】スイッチ用nMIS(Qs)のスイッチゲート電極SGと、スイッチ用nMIS(Qs)にワード線に対して交差する方向に沿って隣接するメモリ用nMIS(Qm)のメモリゲート電極MGとの間に、スイッチ用nMIS(Qs)のソース/ドレイン領域SDHとして機能し、同時にメモリ用nMIS(Qm)のドレイン領域Dとして機能する半導体領域を形成し、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)側のソース/ドレイン領域SDHを構成する半導体領域の形状と、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)と反対側(ビット線側)のソース/ドレイン領域SDLを構成する半導体領域の形状とを非対称とする。

(もっと読む)

ラッチ回路及び半導体装置

【課題】新規のラッチ回路を提供すること。

【解決手段】ラッチ回路は、酸化物半導体(OS)によってチャネル領域が形成されるトランジスタ10を有し、出力端子(Q端子)並びにトランジスタ10のソース及びドレインの一方に電気的に接続され、且つトランジスタ10がオフ状態となることによって浮遊状態となるノード11においてデータを保持する。なお、当該酸化物半導体は、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い。このような酸化物半導体によってトランジスタのチャネル領域が形成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

記憶装置

【課題】リフレッシュ動作の回数を減らすことで、消費電力を抑える。また、先に書き込んだデータを破壊することなく、データを読み出す。

【解決手段】ソースまたはドレインの一方となる第1の電極と、ソースまたはドレインの他方となる第2の電極と、第1のチャネル形成領域に絶縁膜を介して重畳して設けられた第1のゲート電極と、を有する第1のトランジスタと、ソースまたはドレインの一方となる第3の電極と、ソースまたはドレインの他方となる第4の電極と、第2のチャネル形成領域が第2のゲート電極と第3のゲート電極との間に絶縁膜を介して設けられた第2のトランジスタと、を有するメモリセルを複数有し、第1のチャネル形成領域及び第2のチャネル形成領域は、酸化物半導体を含んでおり、第2の電極は、第2のゲート電極に直接接続されている記憶装置とする。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

バイト、ページおよびブロックに書き込むことができ、セルアレイ中で干渉を受けず分割が良好な特性を備え、新規のデコーダ設計とレイアウトの整合ユニットと技術を使用する単体式複合型不揮発メモリ

【課題】

バイト、ページおよびブロックで書き込むことができる新単体式複合型不揮発メモリを提供する。

【解決手段】

不揮発メモリアレイは、シングルトランジスタフラッシュメモリセルおよびダブルトランジスタEEPROMメモリセルを備え、同じ基板上に整合することができ、該不揮発メモリセルは低いカップリング係数の浮遊ゲートを備えて、メモリセル体積を減少でき、該浮遊ゲートをトンネル絶縁層の上に配置し、該浮遊ゲートは該ソース領域の辺縁および該ドレイン領域の辺縁に揃って、且つ該ソース領域辺縁および該ドレイン領域辺縁の幅に画定される幅を備え、該浮遊ゲートと該制御ゲートは50%より小さい相対的に小さなカップリング係数を備えて、該不揮発メモリセルを縮小できるようにし、該不揮発メモリセルのプログラムはチャネル熱電子方式で達成し、消去は高電圧でFNトンネル方式で達成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の電気的性能および信頼性を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGは、金属膜6aと金属膜6a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極であり、金属膜6aの上端部には、金属膜6aの一部が酸化することで金属酸化物部分17が形成されている。スプリットゲート型の不揮発性メモリの制御ゲート電極は、金属膜4aと金属膜4a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極である。

(もっと読む)

半導体装置およびその製造方法

【課題】FMONOSメモリセルとCMOSトランジスタが共存する半導体装置において、トランジスタの駆動電流を高めるとともにFMONOSメモリセルとしての機能を確保する半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面上に形成された、チャネルを有するMONOS型メモリセルと、主表面上に形成されたnチャネル型トランジスタと、主表面上に形成されたpチャネル型トランジスタとを備える半導体装置である。上記MONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタの上面に接するように窒化膜CS1、CS2が形成されている。上記窒化膜CS1、CS2はMONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタのチャネルに応力を付加する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリおよび容量素子を有する半導体装置の性能を向上させる。

【解決手段】同一の半導体基板1上に、不揮発性メモリのメモリセルMCと容量素子とが形成されている。メモリセルMCは、半導体基板の上部に絶縁膜3を介して形成された制御ゲート電極CGと、半導体基板1の上部に形成されて制御ゲート電極CGと隣合うメモリゲート電極MGと、メモリゲート電極MGと半導体基板1との間および制御ゲート電極CGとメモリゲート電極MGとの間に形成されて内部に電荷蓄積部を有する絶縁膜5とを有している。容量素子は、制御ゲート電極CGと同層のシリコン膜で形成された下部電極と、絶縁膜5と同層の絶縁膜で形成された容量絶縁膜と、メモリゲート電極MGと同層のシリコン膜で形成された上部電極とを有している。そして、上部電極の不純物濃度は、メモリゲート電極MGの不純物濃度よりも高くなっている。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

21 - 40 / 599

[ Back to top ]