Fターム[5F101BD13]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | メモリセル(センサ) (3,677) | MOSトランジスタ (3,641) | チャンネル領域 (360) | チャンネル形状 (138)

Fターム[5F101BD13]に分類される特許

121 - 138 / 138

記憶素子及び回路素子

【課題】 強誘電体ゲートFETにおける、強誘電体にかかる反電場を抑制することにより、強誘電体ゲートFETを備え、良好な記憶保持特性を有する記憶素子を提供する。

【解決手段】 極薄い半導体薄膜1によりチャネルを、強誘電体2によりゲート絶縁膜をそれぞれ構成した電界効果トランジスタ10から成り、強誘電体2の分極状態により情報を保持し、電界効果トランジスタ10に電場が印加されることにより、強誘電体2の分極状態が変化して情報の記録が行われ、極薄い半導体薄膜1の厚さが電子閉じ込め効果が発現する厚さである記憶素子を構成する。

(もっと読む)

チャージトラップインシュレータメモリ装置

【課題】ナノスケールチャージトラップインシュレータメモリ装置において維持特性を向上させ、多数のセル絶縁層を用いて多数のチャージトラップインシュレータセルアレイが垂直方向に積層してセル集積容量を高める技術を開示する。

【解決手段】チャージトラップインシュレータに格納されたデータがビットラインに出力される直列に連結された多数のメモリセルと、第1の選択信号の状態に従いビットラインと前記多数のメモリセルを選択的に連結する第1のスイッチング素子と、第2の選択信号の状態に従いセンシングラインと複数個のメモリセルを選択的に連結する第2のスイッチング素子とを含み、チャージトラップインシュレータの極性に従い抵抗が変化するP型フロートチャンネルと、P型フロートチャンネルの両側に形成されたP型ドレイン領域及びP型ソース領域とを含む。

(もっと読む)

不揮発性半導体記憶装置、その製造方法、その書き込み方法、その読み出し方法、記録媒体並びに半導体記憶装置

【課題】電荷捕獲量の調節を容易且つ確実に行い、情報ばけ等の不都合の発生を防止し

て所望の多値情報を記憶する。

【解決手段】ソース領域3−ドレイン領域4間のチャネル領域Cとゲート電極6との間

に、ゲート酸化膜11、シリコン窒化膜12、シリコン酸化膜13、シリコン窒化膜14

、シリコン酸化膜15、シリコン窒化膜16及びシリコン酸化膜17が順次積層されてな

る電荷捕獲膜5が配されて半導体記憶装置が構成される。ここで、各窒化膜12,14,

16とその下層の各酸化膜11,13,15,17との間に存するトラップに電荷を蓄積

することで、4値("00","01","10","11")の情報が記憶される。

(もっと読む)

サドル型フラッシュメモリ素子及び同製造方法

本発明はサドル(Saddle)構造を持つナノ寸法のフラッシュメモリ素子及びその製造方法に関し、特にMOS基盤フラッシュメモリ素子の縮小化特性と性能を改善するためのサドル型高集積/高性能フラッシュメモリ素子に関する。

本発明によれば、リセスされたチャネルの表面及び側面を露出するためリセスされたチャネル周辺の絶縁膜が選択的に取り除かれる。露出された表面及び側面にトンネル絶縁膜が形成される。形成された構造上に、浮遊電極、電極間絶縁膜及び制御電極が形成され、このようにして素子が製造される。特に、浮遊電極が絶縁窒化膜又は多数のナノ寸法のドットで造られる場合は、追加マスクを使用することなく優れたメモリ素子を造ることができる。本発明によれば、素子の縮小化特性がすぐれ、かつリセスされたチャネルの表面及び側面に電流が流動できるチャネルが形成されるため、電流駆動能力が大きく向上する。また、チャネルを制御する制御電極の能力も向上させることができ、それによりメモリ書き込み/消去が改善できる。  (もっと読む)

(もっと読む)

マルチビット不揮発性メモリ素子の単位セル、これを用いたマルチビット不揮発性メモリ素子の動作方法、及びその製造方法、並びにマルチビット不揮発性メモリ素子のNANDセルアレイ

【課題】マルチビット不揮発性メモリ素子、その動作方法、及びその製造方法を提供する。

【解決手段】マルチビット不揮発性メモリ素子の単位セル200は、垂直に形成された複数のチャンネル215,220と、そのチャンネルの外側に垂直に形成されたストレージノード225,230と、そのチャンネル及びストレージノードの上部とストレージノードの側面とを取り囲んでいる制御ゲート240と、そのチャンネル、ストレージノード及び制御ゲートの各間に介在された絶縁膜235と、を含む。

(もっと読む)

不揮発性半導体メモリの製造方法

【課題】安定でかつ信頼性の高い不揮発性半導体メモリを形成する。

【解決手段】p型シリコン半導体基板65への不純物導入後に溝63を形成し、この溝63を形成する凸部64a,64bに、不純物拡散層62a,62bを形成する。このようなp型シリコン半導体基板65上に、シリコン酸化膜からなる第1絶縁膜66a、シリコン窒化膜からなる電荷捕獲膜66b、およびシリコン酸化膜からなる第2絶縁膜66cが順に積層された3層構造のゲート絶縁膜66が形成される。このゲート絶縁膜66上に、ゲート電極61が形成される。ここで、p型シリコン半導体基板65の溝63の部分は、不揮発性半導体メモリ60のチャネル領域となる。この不揮発性半導体メモリ60では、素子が微細化されても、その実効的なチャネル長が確保されるので、安定で、高い信頼性を実現できる。

(もっと読む)

不揮発性半導体メモリの製造方法

【課題】安定でかつ信頼性の高い不揮発性半導体メモリを形成する。

【解決手段】p型シリコン半導体基板15に溝13a,13bを形成し、この溝13a,13b底面部に、不純物拡散層12a,12bを形成する。このようなp型シリコン半導体基板15上に、シリコン酸化膜からなる第1絶縁膜16a、シリコン窒化膜からなる電荷捕獲膜16b、およびシリコン酸化膜からなる第2絶縁膜16cが順に積層された3層構造のゲート絶縁膜16が形成される。このゲート絶縁膜16上に、ゲート電極11が形成される。ここで、溝13a,13bによって形成された凸部14は、不揮発性半導体メモリ10のチャネル領域となる。この不揮発性半導体メモリ10では、素子が微細化されても、その実効的なチャネル長が確保されるので、安定で、高い信頼性を実現できる。

(もっと読む)

マルチビット不揮発性メモリセルを含む半導体素子及びその製造方法

【課題】マルチビット不揮発性メモリセルを含む半導体素子及びその製造方法を提供する。

【解決手段】不揮発性半導体素子は、ソース及びドレーン領域がそれぞれ共有される複数のトランジスタを備える単位セルを含み、複数のトランジスタは、それぞれ少なくとも一つのコントロールゲートと少なくとも一つの電荷蓄積領域とを含み、各コントロールゲートは各トランジスタのスレッショルド電圧をシフトするための少なくとも一つのコントロール電圧に連結される。これにより、フラッシュEEPROMの高集積化及びメガバイト当たり低コスト化を効果的に達成できる。

(もっと読む)

FeRAM装置に適用するSiO2、TiおよびIn2O3薄膜の選択的エッチング処理法

【課題】MFMoxに用いられるSiO2、チタンおよびIn2O3の薄膜の選択的エッチング技術を提供する。

【解決手段】本発明の上記薄膜の3層構造を選択的にエッチングする方法は、約10から30sccmの範囲内のC3F8と、約20から40sccmの範囲内のアルゴンとを使用し、約2から6mtorrの範囲内の圧力下での、約1000から3000wattの範囲内のRFソースと約400から800wattの範囲内のRFバイアスとを使用する、チタンの層で停止するSiO2のエッチングと、約10から50sccmの範囲内のBClと、約40から80sccmの範囲内の塩素と、約4から8mtorrの範囲内の圧力と約100から200wattの範囲内のRFバイアスとの下での約200から500wattの範囲内のTcpとを使用する、In2O3の層で停止するチタンのエッチング、とを含む。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】しきい値の動作許容領域を狭くすることなく、あるいは、動作電圧を高めることなく、マルチビットの動作を可能とするメモリセルを提供する。

【解決手段】メモリセルトランジスタのチャネルの幅方向にチャネル特性の異なる領域を有するメモリセルを提供するものである。すなわち、チャネル領域中で不純物濃度の異なる領域を設けることにより、チャネルしきい値の異なる領域を設けたメモリセル、あるいは、チャネル長が一定ではなく、短い領域と長い領域を有するメモリセル構造を提供する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 フィン型NAND Flashメモリーを自己整合的に製造できる構造及びその製造方法を提供する。

【解決手段】 SOI層を短冊状にすることによりシリコン層領域8がBOX酸化膜13上に形成され、このシリコン層領域8の側面及び上面にそれぞれにトンネル絶縁膜9及び絶縁膜領域31が形成され、トンネル絶縁膜9及び絶縁膜領域31に接してフローティングゲート領域36が形成され、フローティングゲート領域36に接して絶縁膜37が形成され、絶縁膜37及び絶縁膜領域31に接してフローティングゲート領域38が形成されている構造において、フローティングゲート領域36の高さがシリコン領域8の高さよりも大きく形成されている。

(もっと読む)

不揮発性メモリ

【課題】 シリコンドットに密度を増加させずに、書き込み前と書き込み後における、メモリ素子のしきい値電圧のシフトを大きくし、かつ電荷の保持時間を長くすることが可能な、シリコンドットを電荷の蓄積に利用した不揮発性メモリ素子を提供する。

【解決手段】 本発明の不揮発性メモリ素子は、完全空乏型の薄膜SOI表面に形成されたトンネル酸化膜と、該トンネル酸化膜表面に所定の密度で形成された複数のシリコンドットと、該シリコンドットを挟んで、トンネル酸化膜上に形成された酸化膜と、該酸化膜の表面に形成されたゲート電極とを備える。

(もっと読む)

フィン電界効果トランジスタメモリセル、フィン電界効果トランジスタメモリセルアレイおよびフィン電界効果トランジスタメモリセルの製造方法

本発明は、フィン電界効果トランジスタメモリセル(200)、フィン電界効果トランジスタメモリセルアレイおよびフィン電界効果トランジスタメモリセルの製造方法に関するものである。フィン電界効果トランジスタメモリセル(200)は、第1ソース/ドレイン領域(201)および第2ソース/ドレイン領域(202)と、ゲート領域とを有している。メモリセル(200)は、さらに、上記第1ソース/ドレイン領域(201)と第2ソース/ドレイン領域(202)との間にチャネル領域を有する半導体フィン(204)を有し、少なくとも一部が上記ゲート領域上に形成されてなる電荷蓄積層(207・208)を有している。上記電荷蓄積層の少なくとも一部の領域上には、ワード線領域(205・206)が形成されている。フィン電界効果トランジスタセルへの所定の電位の印加により、電荷キャリアを選択的に上記電荷蓄積層へ注入または該電荷蓄積層から放出することができる。  (もっと読む)

(もっと読む)

SONOS記憶セル及びその形成方法

【課題】 SONOS記憶セル及びその形成方法を提供する。

【解決手段】 このセルは少なくとも一つの側壁を有する陥没された領域が配置された基板及び第1絶縁膜を介在して陥没された領域を満たすトラップ貯蔵パターンを含む。基板の上部面及びトラップ貯蔵パターンの上部面上に第2絶縁膜を介在して制御ゲート電極が配置される。制御ゲート電極両側の基板内に第1及び第2ソース/ドレイン領域が配置される。トラップ貯蔵パターンの上部面は平ら(flat)であり、少なくとも基板の上部面と同一の高さである。

(もっと読む)

3次元不揮発性メモリ

【課題】 小さい幾何学的形状のビットトランジスタを作る。

【解決手段】 半導体材料(たとえばP型シリコン)のストリップが酸化され、結果として得られる酸化物のストリップは除去されて、急勾配の側壁を有する半導体材料の上表面に窪みを残す。急勾配の側壁にはイオン衝撃による大きなダメージはない。なぜならこれらは酸化によって形成されたものであって、半導体材料に反応性イオンエッチングを施すことによって形成されたものではないからである。したがって高品質のトンネル酸化物が急勾配の側壁上に形成され得る。次にフローティングゲート124がトンネル酸化物上に形成され、対応のワード線がフローティングゲート上に形成され、導電領域(たとえばN型シリコン)が窪みの底部の中へ形成され、フローティングゲートと対応するいくつかの導電領域150(たとえばN型シリコン)が窪みの縁の上方に形成される。

(もっと読む)

スプリットゲート型フラッシュメモリ素子及びその製造方法

【課題】ディスターバンス問題を防止できるスプリットゲート型フラッシュメモリ素子及びその製造方法を提供する。

【解決手段】バルクシリコン基板の活性領域に形成されているシリコンエピタキシャル層と、素子のソース及びドレイン間のバルクシリコン基板に形成されているディスターバンス防止用絶縁膜とを備えるスプリットゲート型フラッシュメモリ素子であり、該スプリットゲート型フラッシュメモリ素子では、ディスターバンス防止用絶縁膜は、STI形成工程を利用して形成される。

(もっと読む)

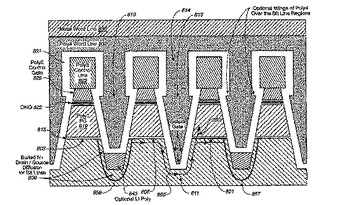

ピラー構造セルのフラッシュメモリ技術

ピラー形不揮発性メモリセル803は各々がトレンチ810によって隣接するメモリセルから絶縁されるメモリセルを各々有している。各メモリセルは基板上に処理層を積層することによって形成される。すなわち、トンネル酸化物層815、ポリシリコンフローティングゲート層819、ONOまたは酸化物層822、ポリシリコンコントロールゲート層825である。ステップの多くの態様が自己整合される。これらのメモリセルのアレイにはより少ない分割しか必要ない。さらに、このメモリセルは、電子がフローティングゲート819に対して直角またはほぼ垂直843に向けられるので、プログラミング特性が増強される。  (もっと読む)

(もっと読む)

個別ゲート構造を備えたトランジスタ

個別ゲート構造(701,703)を備えたトランジスタを形成する方法。これらのゲート構造はそれぞれ、半導体構造(105)の複数の側壁に隣接する。本方法は、ゲート材料層(203)を含む少なくとも一つの共形な層を、チャネル領域を含む半導体基板の上に堆積させることを含む。平坦層(403)がウェハの上に形成される。平坦層は、基板上の所定の位置において少なくとも一つの共形な層の頂部表面よりも低い位置に頂部表面を有する。少なくとも一つの共形な層をエッチングすることにより、半導体構造の上のゲート材料は除去される。  (もっと読む)

(もっと読む)

121 - 138 / 138

[ Back to top ]