Fターム[5F101BD13]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | メモリセル(センサ) (3,677) | MOSトランジスタ (3,641) | チャンネル領域 (360) | チャンネル形状 (138)

Fターム[5F101BD13]に分類される特許

21 - 40 / 138

不揮発性半導体メモリ

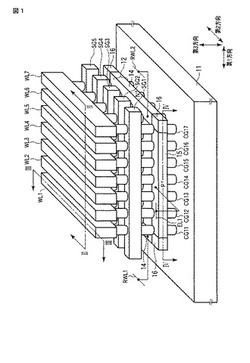

【課題】新たなコンセプトに基づく不揮発性半導体メモリを提供する。

【解決手段】本開示の不揮発性半導体メモリは、半導体基板11上の半導体層12と、半導体層12を貫通する複数のコントロールゲートCG11〜CG17と、第1方向の2つの端部における半導体層12内にそれぞれ配置される2つの第1導電型拡散層14と、半導体層12上で第1方向に延びる複数のセレクトゲート線SG1〜SG5と、複数のセレクトゲート線SG1〜SG5上で第2方向に延びる複数のワード線WL1〜WL7とを備える。複数のセレクトゲート線SG1〜SG5の各々は、第1方向に並ぶ複数のコントロールゲートCG11〜CG17と複数のワード線WL1〜WL7との間に接続される複数のセレクトトランジスタに共有されるセレクトゲートとして機能する。半導体層12及び複数のコントロールゲートCG11〜CG17は、メモリセルアレイを構成する。

(もっと読む)

限られたチャージ拡散を有するチャージトラップメモリ

【課題】隣接メモリセルへの漏洩電流を減らすフラッシュメモリ、特にチャージトラップメモリおよびそれを形成するプロセスフローの提供。

【解決手段】セルチャンネル620を含む半導体線が、STI領域120上に形成される。セルチャンネルは、トンネル酸化物層621、トラッピング誘電体層623、およびブロッキング誘電体層628を含む活性誘電体スタックで覆われる。結果として得られるセルチャンネルを分離するトレンチ625は、伝導層460で少なくとも部分的に充填され得る。活性誘電体層および/または伝導層の部分は、セルチャンネルの下、たとえば、セルチャンネルおよびSTI領域の間の界面695の下に位置し得る。そのような構成は、活性誘電体スタックおよび/または半導体層がセルチャンネルの下に位置しない構成に比べて、あるセルチャンネルから隣接セルチャンネルに拡散する荷電粒子670に対して経路長の増大をもたらす。

(もっと読む)

メモリセル電荷記憶素子あたりに二重のコントロールゲートを有するフラッシュメモリセルアレイ

【課題】フローティングゲートが少なくとも2つのコントロールゲートラインと容量的に結合するようになっているフラッシュNANDタイプのEEPROMシステムの提供。

【解決手段】コントロールゲートラインはフローティングゲートの側壁と結合するようにフローティングゲート間に位置し、メモリセルの結合比が望ましく高められる。フローティングゲートの選択された行の両側の両方のコントロールゲートラインは普通同じ電圧まで高められ、隣接するフローティングゲートの選択されていない行に結合された第2のコントロールゲートラインは低く保たれる。選択されたフローティングゲートの領域でその電圧を選択的に高めるために、コントロールゲートラインを基板と容量的に結合させる。フローティングゲートの長さとコントロールゲートラインの厚さとは、スペーサのエッチマスクを形成することによってプロセスの最小分解エレメントより小さくされ得る。

(もっと読む)

SeOIの連想メモリでデータを比較するデバイス

【課題】連想メモリの比較デバイス、比較デバイスを制御する方法、および連想メモリを提供する。

【解決手段】データビットを格納する第1のトランジスタT1およびデータビットの補数を格納する第2のトランジスタT2によって形成されたメモリセルであって、各トランジスタは、セミコンダクタ・オン・インシュレータ基板上に作られ、各々は、フロント制御ゲート、およびトランジスタを遮断するように制御するバック制御ゲートBG1、BG2を有する、メモリセルと、各々のフロント制御ゲートに公称読出し電圧を加えることによって読出しモードで動作させ、一方、バック制御ゲートBG1、BG2を、一方をビット(DATA)、他方をビットの補数(DATAb)で制御し、ビット(DATA)と格納されたビットが一致する場合には各々のうちの通過トランジスタを遮断し、各々のソースに連結されたソース線SLの電流の有無を検出する比較回路を備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】従来の半導体記憶装置では、十分に半導体チップの面積を削減することができない問題があった。

【解決手段】本発明の半導体記憶装置は、半導体基板の平坦部に形成されたドレイン領域13と、半導体基板に形成された凸部の上端部に形成されたソース領域10と、ドレイン領域13の一部と重なる領域であって、かつ、平坦部の上層に形成されるコントロールゲート12と、コントロールゲート12と隣り合った領域であって、平坦部、凸部の壁面及びソース領域10の一部を覆う領域に形成されるフローティングゲート11と、を有する。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

スプリットゲート不揮発性メモリセルの作製に有用な半導体構造を形成する方法

半導体層(12)に半導体デバイス(10)を形成する方法が提供される。方法は、半導体層(12)の上方に選択ゲート誘電体層(14)を形成すること、選択ゲート誘電体層(14)の上方に選択ゲート層(16)を形成すること、選択ゲート層の少なくとも一部分を除去することによって、選択ゲート層(16)の側壁を形成することを含む。方法は、選択ゲート層(16)の側壁の少なくとも一部分に、および選択ゲート層(16)の少なくとも一部分の下に、犠牲層(22)を成長させること、犠牲層(22)を除去して、選択ゲート層の側壁の少なくとも一部分の表面および選択ゲート層の下の半導体層の表面を露出させることをさらに含む。方法は、制御ゲート誘電体層(28)、電荷蓄積層(32)、および制御ゲート層(34)を形成することをさらに含む。 (もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】N+型ソース層とフローティングゲートとのカップリング比を高くしてプログラム特性を改善すると共にメモリーセルの面積の縮小化を図る。

【解決手段】N+型ソース層4の両側にトレンチ3を形成する。トレンチ3の側壁は2つの素子分離層STI2の端面と平行なトレンチ側壁2a、トレンチ側壁2bと、STI2に垂直な面からなるトレンチ側壁3a、及びトレンチ側壁3aと平行でないトレンチ側壁3bから構成される。かかる構成のトレンチ3の上部からトレンチ側壁3aに平行で、且つP型ウエル層1に垂直又は角度をもった砒素イオン等のイオン注入を行い、トレンチ3底面からトレンチ側壁3bに延在するフローティングゲートFG6と広い面積で対峙するN+型ソース層4を形成する。

(もっと読む)

Fin−FET型不揮発性メモリ・セル及びアレイ並びにその製造方法

不揮発性メモリ・セルが、基板層を有し、第1の導電型のフィン形状半導体部材が基板層上にある。フィン形状部材は、第2の導電型の第1の領域と、第1の領域から離間配置された第2の導電型の第2の領域とを有し、チャネル領域が第1の領域と第2の領域との間に延びている。フィン形状部材は、第1の領域と第2の領域との間に上面及び2つの側面を有する。ワード線が、第1の領域に隣接し、チャネル領域の第1の部分の上面及び2つの側面に容量結合される。浮遊ゲートが、ワード線に隣接し、上面から絶縁され、チャネル領域の第2の部分の2つの側面に容量結合される。 (もっと読む)

半導体記憶装置

【課題】最小加工寸法幅で並列され、コンタクトの抵抗抑制が可能な素子領域を有する半導体記憶装置を提供する。

【解決手段】素子領域33aが、曲折部35の両端部にそれぞれ接続され、最小加工寸法幅の直線部34を有し相異なる素子領域方向21に延在し、素子領域33aと同形状の素子領域33b、cが、素子領域方向21から45度のワード線方向23に曲折部35があるように、それぞれ素子分離領域31を隔てて並行し、半導体基板11に垂直なコンタクトプラグ41が、曲折部35にそれぞれ接続され、素子領域33でそれぞれ構成の選択トランジスタ46に共通の選択ゲート線38が、絶縁膜39上で、コンタクトプラグ41に近接しワード線方向23に並列延在し、素子領域33でそれぞれ構成のメモリセル45に共通のワード線37が、絶縁膜39上で、選択ゲート線38に対してコンタクトプラグ41の反対側でワード線方向23に並列延在する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】ドレイン電流の制御性を向上させつつ、メモリセルを縦方向に積層するとともに、メモリセルにフィン構造を用いた場合においても、制御ゲート電極および電荷蓄積層の加工の難易度を低下させる。

【解決手段】ブロック層13、電荷蓄積層14およびトンネル酸化膜15を順次介してフィン状の制御ゲート電極12aに埋め込まれたチャネル領域を有するボディ層17を設ける。

(もっと読む)

半導体装置の製造方法

【課題】面方位が(110)面あるいはこれと等価な面であるシリコン層上に形成する酸化膜厚の制御を行うことのできる半導体装置の製造方法を提供すること。

【解決手段】面方位が(110)面あるいはこれと等価な面であるシリコン基板1表面の一部に、リンのイオン注入を行って、端部の不純物濃度が連続的に変化した第1の不純物領域2Aを形成する工程と、熱酸化を行って、シリコン基板1上に端部の厚さが連続的に変化したシリコン酸化膜3を形成する工程と、を含むこと、を特徴とする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリウィンドウが広い半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置1において、半導体基板11上にトンネル絶縁膜12及びブロック絶縁膜13を設け、その上に制御ゲート電極18を設ける。そして、トンネル絶縁膜12とブロック絶縁膜13との間に、電荷蓄積粒15を分散させる。電荷蓄積粒15は、シリコン窒化物からなる窒化部16と、窒化部16に接し、シリコンからなるシリコン部17とにより構成する。電荷蓄積粒15は、シリコン窒化膜の表面上にシリコンを堆積させることにより、複数のシリコン粒子を形成した後、シリコン窒化膜をシリコン粒子毎に分断することによって形成されたものである。

(もっと読む)

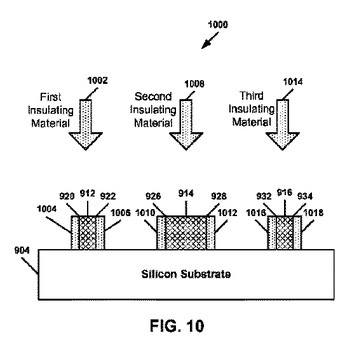

フィン電界効果トランジスタ(フィンFET)デバイスの製造方法

フィン電界効果トランジスタ(フィンFET)を用いた半導体の製造方法が開示される。特定の実施形態の方法は、第一の幅によって離隔された第一の側壁及び第二の側壁を有する第一のダミー構造体をシリコン基板上に堆積させるステップを含む。また、本方法は、第一のダミー構造体を堆積させるのと同時に第二のダミー構造体をシリコン基板上に堆積させるステップも含む。第二のダミー構造体は、第二の幅によって離隔された第三の側壁及び第四の側壁を有する。第二の幅は第一の幅よりも実質的に大きい。第一のダミー構造体を用いて略第一の幅によって離隔された第一の対のフィンを形成する。第二のダミー構造体を用いて略第二の幅によって離隔された第二の対のフィンを形成する。  (もっと読む)

(もっと読む)

メモリ装置

【課題】電荷トラップ層からのトンネル効果による電子の漏れを抑制することができ、データの保持時間の長期化を図ることができるとともに、トンネル酸化膜の薄膜化を可能として、データの書き込み速度の向上を図ることのできるメモリ装置を提供する。

【解決手段】シリコン層と、シリコン層と接して設けられたゲート絶縁膜と、ゲート絶縁膜に接して設けられたゲート電極とを有するメモリ素子を具備したメモリ装置において、ゲート絶縁膜は、トンネル酸化膜、電荷トラップ膜、ブロック酸化膜の3層を積層して構成されたゲート絶縁膜であり、ゲート電極は、ブロック酸化膜上に形成されたゲート電極であって、シリコン層が、当該シリコン層の厚さが2nm以上14nm以下となるように、ゲート絶縁膜によって挟まれた部分、又はゲート絶縁膜と他の絶縁膜とによって挟まれた部分を有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】損傷のない酸化膜及び電荷蓄積層の形成とその膜厚の制御を可能とする半導体装置及びその製造方法を提供する。

【解決手段】RIE等の異方性エッチングによって、マスク用窒化膜2、第1窒化膜12、及び第2酸化膜13を分離する。このとき、トレンチ3底部のマスク用酸化膜1をエッチングせずに残し、エッチングに対する防御層としての役割を果たすため基板10への損傷はない。また、分離した第1窒化膜12のトレンチ3の側壁を覆う部分は、犠牲酸化膜13に保護されているためエッチングによる損傷はない。次いで、等方性エッチングによって、異方性エッチングによって損傷した第2酸化膜13及びトレンチ3底部の第1酸化膜11を完全に除去する。次いで、プラズマ酸化やラジカル酸化等の酸化処理により、第3酸化膜14及びゲート酸化膜15が形成される。

(もっと読む)

半導体記憶装置

【課題】異なる階層に位置するメモリセル間の特性のばらつきを抑制できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置1は、半導体基板11と、半導体基板11上に設けられ、複数の絶縁層14と複数の導電層WL1〜WL4とが交互に積層された積層体と、積層体を貫通して形成された貫通ホールの内部に設けられ、絶縁層14と導電層WL1〜WL4との積層方向に延びる半導体層SPと、導電層WL1〜WL4と半導体層SPとの間に設けられた電荷蓄積層26と、を備え、半導体層SPにおける下部は上部よりも細く、導電層WL1〜WL4における少なくとも最下層は最上層よりも薄い。

(もっと読む)

不揮発性半導体記憶装置およびその制御方法

【課題】チャネルホットエレクトロン書き込み方式が適用されるメモリセルのゲート長を縮小することが可能な不揮発性半導体記憶装置およびその制御方法を提供する。

【解決手段】例えば、アクティブ領域AA0,AA1,AA2の相互間に対応する半導体基板10の表面部に、電荷蓄積用の窒化膜を介して、ワード線GC0,GC1を埋め込み形成する。また、ワード線GC0,GC1に対し、それぞれ斜め方向にチャネル電流が流れるように、ビット線BL0,BL1,BL2とそれぞれ交差するアクティブ領域AA0,AA1,AA2の各部位に、千鳥状に、ソースまたはドレインとなる拡散層領域14a,14b,14c,14d,14eを配置する構成となっている。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】ドレインディスターブ特性が満足でき、電子注入状態における電流の低下が抑制される半導体記憶装置の提供。

【解決手段】溝24を有するP型半導体基板2と、P型半導体基板2の溝24を有しない部分の表面に形成されたソース側N−拡散層44S、N+拡散層42S、ドレイン側N−拡散層44D、N+拡散層42Dと、溝24の側壁部、底部、N−拡散層44S、44D、N+拡散層42S、42Dの表面を覆うゲート酸化膜12と、溝24を埋め込むようゲート酸化膜12の表面に形成され、溝24が連続する方向に格子状に形成されたゲート電極14と、溝24の側壁部の表面のうち、少なくともゲート酸化膜12を介してN−拡散層44S、44Dと対向する領域に形成され、ゲート電極14との間に酸化膜12を介してスペーサ状に形成された窒化膜8と、ゲート電極14と直接接するように形成されたゲート裏打ち配線10と、を備える半導体記憶装置。

(もっと読む)

21 - 40 / 138

[ Back to top ]