Fターム[5F101BH14]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | エッチング (993) | ドライエッチング(方向性エッチング) (440)

Fターム[5F101BH14]に分類される特許

101 - 120 / 440

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のソース電極および第1のドレイン電極と、第1のソース電極および第1のドレイン電極と電気的に接続され、酸化物半導体材料が用いられている第1のチャネル形成領域と、第1のチャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、を有する第1のトランジスタと、容量素子と、を有し、第1のトランジスタの第1のソース電極または第1のドレイン電極の一方と、容量素子の電極の一方とは、電気的に接続された半導体装置である。

(もっと読む)

不揮発性半導体記憶装置

【課題】隣接するメモリセル間の寄生ゲート効果の改善が可能な不揮発性半導体装置を提供する。

【解決手段】不揮発性半導体記憶装置であって、メモリセルトランジスタは、素子領域上に形成されたトンネル絶縁膜111と、トンネル絶縁膜上に形成され、絶縁膜で形成された電荷蓄積層112と、電荷蓄積層上に形成されたブロック絶縁膜113と、ブロック絶縁膜上に形成されたゲート電極114とを含み、各メモリセルトランジスタのゲート電極は、ゲート長方向に隣接するメモリセルトランジスタのゲート電極と、埋込絶縁膜131により分離されており、ブロック絶縁膜は、ゲート長方向に伸びる素子領域上で、ゲート電極下の領域及びゲート電極間の領域R1,R2に連続して形成されており、ゲート電極間の領域に形成されたブロック絶縁膜は、ゲート電極下の領域に形成されたブロック絶縁膜よりも膜厚が薄い薄膜部分Pを有する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的とする。

【解決手段】チャネル形成領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極及び第1のドレイン電極と、を有する第1のトランジスタと、酸化物半導体層と、第2のソース電極及び第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、第2のソース電極または第2のドレイン電極の一方と、第2のゲート絶縁層と、第2のゲート絶縁層上に第2のソース電極または第2のドレイン電極の一方と重畳するように設けられた電極と、を有する容量素子と、を有し、第1のゲート電極と、第2のソース電極又は第2のドレイン電極の一方とは電気的に接続されている。

(もっと読む)

半導体装置およびその作製方法

【課題】本発明の一態様は、酸化物半導体を用いたデバイスにおいて高い移動度を達成し、信頼性の高い表示装置を提供する。

【解決手段】表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層を形成し、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加熱処理を行うことにより、酸化物半導体層に酸素を供給し、酸化物絶縁層上に、水素を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

不揮発性半導体記憶装置

【課題】従来に比してメモリセルの積層数を抑えながら記憶密度を高めることができる不揮発性半導体記憶装置を提供する。

【解決手段】柱状の半導体膜131の側面に形成される電荷蓄積層133、および電荷蓄積層133上に形成されるゲート電極膜134を備えるトランジスタが半導体膜131の高さ方向に複数設けられるメモリストリングスMSが、半導体基板101上に略垂直にマトリックス状に配置され、第1の方向に配置されたメモリストリングスMSの同じ高さのトランジスタのゲート電極膜134間が接続された不揮発性半導体記憶装置において、第1の方向に隣接するメモリストリングスMSの少なくとも最上層のトランジスタ形成位置における半導体膜131間の距離は、電荷蓄積層133の厚さの2倍よりも小さい。

(もっと読む)

半導体装置

【課題】本発明は、半導体基板とコンタクト部材との接触抵抗をより低減可能な半導体装置を提供する。

【解決手段】

第1の方向に延在し第1の方向と直交する第2の方向に所定の間隔で設けられた活性領域AAと、前記活性領域AAを分離する素子分離絶縁膜11とが設けられた半導体基板21aと、前記半導体基板21aの主表面上に形成された第2の層間絶縁膜24と、前記第2の層間絶縁膜24内に設けられ、前記半導体基板21a上方の配線と電気的に接続された第1の部分及び、前記第1の部分と接続され、上面視すると前記第1の部分から、はみ出した形状である第2の部分を有するコンタクト部材22とを備え、前記第1の方向における前記第2の部分最大幅は、前記第1の方向における前記第1の部分の幅よりも広く、前記第2の部分は、前記第1の部分を包囲する前記第2の層間絶縁膜24に接触していることを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトランジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置

【課題】電荷蓄積膜を用いる不揮発性記憶用MOS型トランジスタと、これを選択するMOS型トランジスタが隣接するスプリットゲート構造を有する不揮発性メモリセルにおいて、電荷保持特性を向上し、ゲート電極を低抵抗化する。

【解決手段】電荷蓄積膜のコーナー部の薄膜化を抑制して電荷保持特性を向上するために、選択ゲート電極15の側壁にテーパーを設ける。また、自己整合で形成するゲート電極を低抵抗化するシリサイドを安定に行うため、選択ゲート電極15の側壁をリセスさせる。もしくは、自己整合ゲート電極上部18と選択ゲート電極上部65の間に段差を設ける。

(もっと読む)

記憶装置

【課題】ロジック回路を増やすことなく、第三者がメモリセルにアクセスできずかつ必要な場合にはいつでもアクセス可能なメモリセルを有する記憶装置を提供する。

【解決手段】本実施形態は、第1のメモリセルと、第2のメモリセルと、を有し、第2のメモリセルに設けられた第2のトランジスタの第2のチャネルが酸化物半導体膜からなる記憶装置であって、第2のメモリセルからのデータの読み出しは第2のトランジスタに紫外線を照射している時に行われる記憶装置によって解決する。

(もっと読む)

半導体装置の製造方法、フラッシュメモリの製造方法、およびスタティックランダムアクセスメモリの製造方法ならびにフラッシュメモリ

【課題】同一のレジストパターンにより、ドライエッチングおよびウエットエッチングを連続的に行なう際に、変質したレジスト表面層を剥がれなくするように改良された、半導体装置の製造方法を提供することを主要な目的とする。

【解決手段】半導体基板1の上に、絶縁膜2と導電層3を順次形成する。導電層3の上にレジストパターン4を形成する。レジストパターン4をマスクに用いて、導電層3をドライエッチングする。レジストパターン4の表層部を一部削る。レジストパターン4をマスクに用いて、絶縁膜2をウエットエッチングする。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】 埋め込み配線を形成する時に、埋め込み不良が生じにくい半導体装置の製造方法を提供する。

【解決手段】

(a)コンタクトプラグ25を有する第1層間絶縁膜24上に第2層間絶縁膜27を積層する工程と、(b)前記第2層間絶縁膜27に前記コンタクトプラグ25の上面を露出するトレンチ28aを形成する工程と、(c)前記トレンチ28a内で、開口端側に空間部を形成し、前記コンタクトプラグ側に、レジスト29cを埋め込む工程と、(d)等方性エッチングにより、前記第2層間絶縁膜27bのうち前記トレンチ28aの空間部で挟まれる前記第2層間絶縁膜27b部分の側壁を側方に後退させて、前記トレンチ28aの開口端側の幅よりも開口端側の幅が大きな加工トレンチ28bを形成する工程と、(e)前記レジスト29cを除去し、前記加工トレンチ28b内に配線金属層を埋め込む工程と、を含むことを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】半導体材料を含む基板に設けられたチャネル形成領域と、チャネル形成領域を挟むように設けられた不純物領域と、チャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、不純物領域と電気的に接続する第1のソース電極および第1のドレイン電極と、を有する第1のトランジスタと、半導体材料を含む基板上の第2のゲート電極と、第2のゲート電極上の第2のゲート絶縁層と、第2のゲート絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続する第2のソース電極および第2のドレイン電極と、を有する第2のトランジスタと、を有する半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】階段状に加工された複数の導電層と、各導電層に達し深さの異なる複数のコンタクトホールとの接続構造の信頼性を高めた半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基板10の第2のコンタクト領域5上に設けられ、第2のコンタクト領域5と第1のコンタクト領域4との間に段差を形成する下地層45bと、下地層45bを覆って基板10上に設けられ、下地層45b上に積層された上段部81が階段状に加工された下層側積層体91と、下層側積層体91における第1のコンタクト領域4上に積層された下段部82の上に設けられ、階段状に加工された上層側積層体92と、階段状に加工された部分を覆う層間絶縁層62と、層間絶縁層62を貫通し階段状に加工された部分の各々の導電層WLに達して形成されたコンタクトホール内に設けられたコンタクト電極51と、を備えた。

(もっと読む)

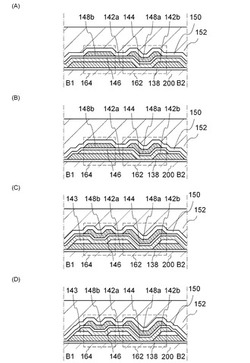

配線パターン形成方法および半導体装置の製造方法、半導体装置、データ処理システム

【課題】2回のリソグラフィ工程によるSADP法(Self Align Double Patterning)を用いて、第1配線パターン形成領域には解像限界未満のパターンを含む第1配線パターンを形成し、第2配線パターン形成領域には解像限界以上の通常パターンからなる第2配線パターンを簡便に形成する方法を提供する。

【解決手段】解像限界未満の寸法を有する複数の配線を含む第1配線パターンを、第1リソグラフィ工程と第1リソグラフィ工程の後に実施される第2リソグラフィ工程を用いて形成し、第1のリソグラフィ工程で形成されたパターンに対してのみサイドウォールの形成および除去処理を行い、その後、解像限界以上のパターンを生成する第2リソグラフィ工程を実施する。第2のリソグラフィ工程で形成される解像限界以上の通常パターンに対しては、単純なリソグラフィ工程とすることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】深さの異なる複数のコンタクトホールの底部径のばらつきを抑制する半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、複数の導電層WL1〜WL4が階段状に加工された階段構造部を有する積層体と、階段構造部を覆って設けられた層間絶縁層43と、層間絶縁層43を貫通し、それぞれが対応する各段の導電層WL1〜WL4に達して形成された複数のコンタクトホール61〜64の内部に設けられたコンタクト電極60とを備え、複数のコンタクトホール61〜64の底部の孔径は略同じであり、下段側の導電層に達するコンタクトホールは、上段側の導電層に達するコンタクトホールよりも深く、上端部の孔径が大きい。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】ワードゲートとコントロールゲートの間の高低差を大きくすることなく、シリサイドショートを防止することが可能な不揮発性半導体記憶装置、及びその製造方法を提供すること。

【解決手段】本発明にかかる不揮発性半導体記憶装置は、半導体基板1上にゲート絶縁膜2を介して形成され、一定の幅を有する部分が上に突出した突出部3bが設けられているワードゲート3と、ワードゲート3の側壁面にONO膜4を介して設けられたコントロールゲート5と、コントロールゲート5の側壁面と、ワードゲート3の突出部3bの側壁面とに形成された絶縁性のサイドウォール7と、ワードゲート3の突出部3bの上面と、コントロールゲート5の表面の一部とに形成されたシリサイド層9と、を備え、突出部3bの幅は、突出部3bよりも下側の部分のワードゲート3の幅よりも狭いものである。

(もっと読む)

不揮発性メモリセル及びその製造方法

【課題】同一の基板上に形成されたメモリトランジスタ及び駆動トランジスタを備える透明不揮発性メモリセル及びその製造方法を提供する。

【解決手段】本発明による不揮発性メモリセルは、基板上に形成された半導体膜、バッファー膜、有機強誘電体膜及びゲート電極を含むメモリトランジスタと;前記基板上に形成された前記半導体膜、前記バッファー膜、ゲート絶縁膜及び前記ゲート電極を含む駆動トランジスタと;を備える。本発明によれば、同一の基板上に形成されたメモリトランジスタ及び駆動トランジスタを備え、可視光領域で透明な不揮発性メモリセルを提供することができる。

(もっと読む)

半導体装置の製造方法

【課題】電荷蓄積膜を用いる不揮発性記憶用MOS型トランジスタと、これを選択するMOS型トランジスタが隣接するスプリットゲート構造を有する不揮発性メモリセルにおいて、電荷保持特性を向上し、ゲート電極を低抵抗化する。

【解決手段】電荷蓄積膜のコーナー部20の薄膜化を抑制して電荷保持特性を向上するために、選択ゲート電極15の側壁にテーパーを設ける。また、自己整合で形成するゲート電極を低抵抗化するシリサイドを安定に行うため、選択ゲート電極15の側壁をリセスさせる。もしくは、自己整合ゲート電極上部18と選択ゲート電極上部65の間に段差を設ける。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極から電荷蓄積層に電荷を注入する不揮発性メモリにおいて、従来のゲート構造に比べて電荷の注入効率、電荷保持特性および信頼性を共に向上させる。

【解決手段】電荷蓄積層を構成する窒化シリコン膜に電子および正孔を注入し、トータルの電荷量を変えることによって書き込み・消去を行う不揮発性メモリにおいて、ゲート電極からの電荷注入を高効率で行うために、メモリセルのゲート電極を、ノンドープのポリシリコン層54とメタル材料電極層59の2層膜で構成する。

(もっと読む)

101 - 120 / 440

[ Back to top ]