Fターム[5F101BH14]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | エッチング (993) | ドライエッチング(方向性エッチング) (440)

Fターム[5F101BH14]に分類される特許

61 - 80 / 440

半導体素子及びその製造方法

【課題】絶縁膜を貫通するコンタクトプラグの抵抗を改善させられる半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグと、前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、を含む。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】コントロールゲートの低抵抗化とボイドの抑制とを両立させることができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板の上方に設けられ電荷を蓄積可能なフローティングゲートと、フローティングゲートの上方に設けられ該フローティングゲートに蓄積された電荷量を制御するコントロールゲートとを含むメモリセルを備えている。コントロールゲートは、エッチングで加工可能な金属または金属シリサイドから成る下層コントロールゲート部分と、下層コントロールゲート部分とは異なる材料を用いた上層コントロールゲート部分とを備えている。

(もっと読む)

半導体メモリ装置及びその動作方法

【課題】不揮発性メモリ装置及びその製造方法を提供すること。

【解決手段】本発明の不揮発性メモリ装置の製造方法は、セル領域及び周辺回路領域を有する基板上に層間絶縁膜及びゲート電極膜が交互に積層されたゲート構造物を形成するステップと、前記セル領域の前記ゲート構造物を選択的にエッチングして、複数層の前記ゲート電極膜を一方向から分離させる第1トレンチを形成するステップと、前記周辺回路領域のコンタクト予定領域に対応する前記ゲート構造物を選択的にエッチングして、第2トレンチを形成するステップと、を含む。

(もっと読む)

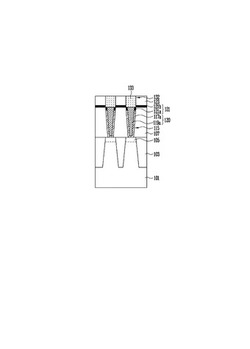

不揮発性記憶素子及びその製造方法

【課題】 信頼性を向上可能な不揮発性記憶素子及びその製造方法を提供する。

【解決手段】 不揮発性素子は、基板100、基板100の上に形成され、制御ベースゲート120a及び制御ベースゲート120aの上に形成される制御金属ゲート125anを有する制御ゲート電極137、制御ゲート電極137と基板100との間に形成される電荷格納領域110a、制御ゲート電極137の上に形成される制御ゲートマスクパターン130、及び制御ゲートマスクパターン130及び制御ベースゲート120aの間に形成された制御金属ゲート125aの側壁の上に形成される酸化防止スペーサ135aを備える。このとき、制御金属ゲート125anの幅は、制御ゲートマスクパターン130の幅より小さくなるように形成されている。これにより、制御金属ゲート125anが酸化工程又は酸化物等によって酸化されることを防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】パターン疎密差の影響を受けないハードマスク形成法を提供する。

【解決手段】基板101上に、第1から第3の膜111,112,113およびレジスト層114を形成した後、疎部R1と密部R2が存在するパターンを前記レジスト層に形成して前記第3の膜をエッチングする。次に、前記第3の膜及び前記レジスト層をマスクとして、密部R2内では前記第2の膜が残存するが、疎部R1内では前記第1の膜が露出するまで、前記第2の膜を除去する。その後CXFYHZガスを使用して、第5の膜115を、疎部R1内に露出した前記第1の膜上に第1の膜厚T1で形成し、密部R2内に残存する前記第2の膜上には膜厚T1よりも薄い第2の膜厚T2で形成する。膜厚T1の前記第5の膜で疎部R1内に露出した前記第1の膜を保護しながら密部R2内に残存する前記第2の膜を除去し、最後に、前記第3から第5の膜を除去して前記第2の膜をハードマスクとする。

(もっと読む)

3次元半導体素子及びその製造方法

【課題】工程不良を無くして収率を向上させることができる3次元半導体素子及びその製造方法が提供される。

【解決手段】3次元(3D)半導体メモリー素子は、基板に隣接する下段から上段まで伸張して、複数個のメモリーセルと連結された垂直チャンネルと、前記複数個のメモリーセルを有し、前記基板上に配置された階段形構造のゲートスタック形態にアレイされたセルアレイと、を含む。前記ゲートスタックは、前記下段に隣接する下部非メモリートランジスターに連結された下部選択ラインを含む下部膜と、前記上段に隣接する上部非メモリートランジスターに各々連結され、互いに連結されて単一の導電性ピースになって上部選択ラインをなす導電ラインを有する複数個の上部膜と、各々ワードラインを有し、セルトランジスターと連結され、前記下部選択ラインと前記上部選択ラインの間に配置される複数個の中間膜と、を含む。

(もっと読む)

半導体装置

【課題】配線の引き出し性が向上されているとともに、配線間の短絡などの電気的問題が生じるおそれが抑制されており、かつ、配線が形成される領域の省スペース化が図られた半導体装置を提供する。

【解決手段】半導体装置1が備える基板4上の所定の層内に、第1の配線3が複数本並べられて設けられている。各第1の配線3は、それらの並べられた方向に沿って一方の側から他方の側へ向かうに連れて長く延ばされて形成されているか、あるいは短く縮められて形成されている。それとともに、各第1の配線3は、隣接するそれぞれの一端部3aが並べられた方向と直交する方向において互いにずれた位置に配置されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】書き込み特性の向上を図る。

【解決手段】半導体記憶装置の製造方法は、基板10上に、トンネル絶縁膜11を形成し、前記トンネル絶縁膜上に、導電体で構成される電荷蓄積層12を形成し、前記電荷蓄積層、前記トンネル絶縁膜、および前記基板を加工して、前記基板内に、前記電荷蓄積層および前記トンネル絶縁膜を分離する素子分離溝22を形成し、前記素子分離溝内に、上面が前記電荷蓄積層の下面より高く上面より低くなるように素子分離絶縁膜13を埋め込み、前記電荷蓄積層の表面に形成された自然酸化膜30を除去し、前記素子分離絶縁膜および前記電荷蓄積層の表面に、絶縁膜14を形成し、前記自然酸化膜の除去から前記絶縁膜の形成までが、その内部の酸素濃度がコントロールされた製造装置内で行われる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】隣接セルとの容量を抑制することが可能な半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態の半導体記憶装置は、第1の方向および前記第1の方向と直交する第2の方向に配置される複数のメモリセルトランジスタを備える。前記メモリセルトランジスタのそれぞれは、半導体基板上に形成される第1の絶縁膜と、前記第1の絶縁膜上に形成される浮遊ゲート電極と、前記浮遊ゲート電極上に形成される第2の絶縁膜と、前記第2の絶縁膜上に形成される制御ゲート電極と、を有する。前記第1および第2の方向に隣接する2つの前記メモリセルトランジスタの前記浮遊ゲート電極は、前記隣接する方向の側面に括れた領域を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】サイドウォール間に層間絶縁膜を埋め込むときに埋め込み不良の発生を防止できる半導体装置の製造方法を提供する。

【解決手段】シリコン基板2の表面上に、ゲート酸化膜6、ポリシリコン層(第1ゲート層)9、タングステンシリサイド層(第2ゲート層)10および絶縁層8が形成される。絶縁層8が所定のゲートパターンにエッチングされる。タングステンシリサイド層10が前記所定のゲートパターンにエッチングされる。タングステンシリサイド層10の側壁が後退される。この後、ポリシリコン層9が前記所定のゲートパターンにエッチングされる。ゲート酸化膜6が前記所定のゲートパターンにエッチングされる。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

不揮発性半導体記憶装置

【課題】ゲート電極間絶縁膜のリーク電流を抑制し、電気的信頼性を向上した不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板上に行列状に形成された複数のメモリ素子と、同一列方向のメモリ素子に選択的に接続される複数のビット線と、同一行方向のメモリ素子に接続される複数のワード線とを具備し、各メモリ素子は、半導体基板上に順次形成された第1のゲート絶縁膜、電荷蓄積層、第2のゲート絶縁膜、制御電極と、電荷蓄積層の対向する側面に沿って、前記シリコン基板上面に形成された1対の不純物注入層とを具備し、ビット線に垂直な方向に沿った断面における電荷蓄積層の上部コーナー部が曲面を有し、上部コーナー部が前記第1のゲート絶縁膜の上方にある。

(もっと読む)

半導体装置の製造方法

【課題】エッチングレートを上昇でき、生産性を向上できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に交互に積層されたシリコン層とシリコン酸化膜とを備える多層膜に対して、一括してエッチングを行う工程を含み、前記エッチングの際のエッチングガスは、少なくとも2種類以上の第7族元素と、第3族元素,第4族元素,第5族元素,または第6族元素とを含有し、前記エッチング工程の際の前記半導体基板に入射するイオンのエネルギーは、100eV以上であり、前記第7族元素に対する、前記第3族乃至前記7族元素の添加比率は、0.5以上3.0以下である。

(もっと読む)

フラッシュメモリアレイのワード線構造を保護するためのワード線保護装置およびフラッシュメモリアレイのためのワード線構造

【課題】製造中に、プロセスに関連する帯電からフラッシュメモリのワード線およびメモリセルを保護するための方法と構造とを与える。

【解決手段】ドープされたポリシリコンのワード線110aの端部にドープされていないポリシリコン110bが形成され、抵抗110bが生成される。これを通じて、プロセスにより生じる電荷が、基板に結合された、ドープされたポリシリコン放電構造110cへ放電される。ワード線抵抗110b、および、放電構造110cは、単一のパターニングされたポリシリコン構造として形成される。ワード線110aおよび放電部分110cは導電性になるように選択的にドープされ、また、抵抗部分110bは、製造後に通常のセル動作が可能なほどに十分高い抵抗が与えられる一方で、製造中にプロセスに関連する電荷に対しては放電路を供給するように、実質的にドープされない。

(もっと読む)

半導体素子のパターン形成方法

【課題】互いに異なる幅のパターンを同一層で形成するにあたり、パターン間の間隔の均一度を改善することができる半導体素子のパターン形成方法を提供する。

【解決手段】セル領域及びセレクトトランジスタ領域を含む下部膜上に補助膜を形成する段階と、前記セレクトトランジスタ領域の前記補助膜上部に第1保護膜を形成する段階と、前記セレクトトランジスタ領域の前記第1保護膜上部には、前記第1保護膜の幅より狭い第1フォトレジストパターンが、前記セル領域の前記補助膜上部には前記第1フォトレジストパターンの幅より狭い第2フォトレジストパターンが形成され、前記第1及び第2フォトレジストパターン間の間隔を前記第2フォトレジストパターン間の間隔と同一に形成する段階と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】周期的に配列された複数本の配線と導電部材が設けられ、導電部材に配線よりも高い電圧を印加することができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、一方向に延び、周期的に配列された複数本の第1配線と、前記複数本の第1配線からなる群の外側に配置され、前記一方向に延びる第2配線と、前記群と前記第2配線との間に設けられた第3配線と、前記第2配線から見て前記群の反対側に配置された複数の導電部材と、を備える。そして、前記第1配線と前記第3配線との最短距離、及び前記第3配線と前記第2配線との最短距離は、前記第1配線間の最短距離と等しく、前記第2配線と前記導電部材との最短距離は、前記第1配線間の最短距離よりも長い。

(もっと読む)

61 - 80 / 440

[ Back to top ]