Fターム[5F102GC08]の内容

接合型電界効果トランジスタ (42,929) | ゲート配置 (2,808) | 縦型FETの埋込みゲート (155)

Fターム[5F102GC08]に分類される特許

21 - 40 / 155

半導体装置およびその製造方法

【課題】低いオン抵抗を得ながら、優れた耐圧性能を持つ、縦型の半導体装置およびその製造方法を提供する。

【解決手段】開口部28はn−型GaNドリフト層4にまで届いており、開口部の壁面を覆うように位置する再成長層27と、p型GaNバリア層6と、ゲート電極Gと、ソース電極Sとを備え、チャネルが電子走行層22内の電子供給層26との界面に生じる二次元電子ガスにより形成され、p型GaNバリア層6がGaN系積層体15の表層をなし、かつソース電極Sが、再成長層27およびp型GaNバリア層6に接して位置することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 p型GaNバリア層の電位を確実に固定することでピンチオフ特性、耐圧性能の向上を安定して得ることができる縦型の半導体装置を提供する。

【解決手段】 GaN系積層体15に開口部28が設けられており、開口部の壁面を覆うように位置するチャネルを含む再成長層27と、ソース電極Sとオーミック接触するn+型ソース層8と、p型GaNバリア層6と、その間に位置するp+型GaN補助層7とを含み、p型GaNバリア6の電位をソース電位に固定するために、p+型GaN補助層7が、n+型ソース層8とトンネル接合を形成することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 縦型GaN系半導体装置において、p型GaNバリア層による耐圧性能の向上を得ながら、オン抵抗を低くできる半導体装置を提供する。

【解決手段】 開口部28壁面に位置するチャネルを含む再成長層27と、端面が被覆されるp型バリア層6と、p型バリア層上に接するソース層7と、再成長層の上に位置するゲート電極Gと、開口部の周囲に位置するソース電極Sとを備え、ソース層が超格子構造で構成され、該超格子構造が、p型バリア層よりも小さい格子定数を持つ第1の層(a層)と、該第1の層よりも格子定数が大きい第2の層(b層)との積層体である、ことを特徴とする。

(もっと読む)

接合型電界効果トランジスタを備えた半導体装置およびその製造方法

【課題】埋込ゲート層とゲート配線とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置を提供する。

【解決手段】埋込ゲート層10とゲート配線12との電気的な接続をトレンチ13内に形成したp+型コンタクト埋込層14によって行うようにする。これにより、p+型コンタクト埋込層14のみしか配置されないトレンチ13の幅を、従来の半導体装置のように層間絶縁膜やゲート配線などが配置されるトレンチと比較して、狭くすることが可能となる。したがって、埋込ゲート層10とゲート配線12とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置とすることが可能となる。

(もっと読む)

有機半導体素子及びその製造方法

【課題】より信頼性の高い有機半導体素子及びその製造方法を提供する。

【解決手段】連続的な第一の電極と、多数の孔が形成された絶縁層及び第二の電極と、連続的な有機半導体層と、連続的な第三の電極と、を有する有機半導体素子とする。また、基板に連続的な第一の電極を形成する工程、第一の電極上に荷電微粒子を分散付着させる工程、第一の電極及び前記分散付着した荷電微粒子上に絶縁層及び第二の電極を形成する工程、荷電微粒子を除去する工程、連続した有機半導体層を形成する工程、有機半導体層上に第三の電極を形成する工程、を有する有機半導体素子の製造方法とする。

(もっと読む)

ジチエノベンゾジチオフェン誘導体からなる有機半導体材料前駆体、インク、絶縁部材、電荷輸送性部材、有機電子デバイス

【課題】印刷等の簡便なプロセスで成膜できる溶解性を有し、成膜後は簡単な処理により不溶化し、後工程でのダメージを軽減できると共に、不溶化処理後は良好な半導体特性を示すジチエノベンゾジチオフェン誘導体からなる有機半導体材料前駆体、該前駆体を含有するインク、該インクを用いて作製された絶縁部材、電荷輸送性部材、有機電子デバイスの提供。

【解決手段】下記一般式(I)で表されるジチエノベンゾジチオフェン誘導体からなることを特徴とする有機半導体材料前駆体。

〔上記式中、X及びYは、外部刺激によりXとYが結合してX−Yとして一般式(I)の化合物から脱離する基を表し、R1及びR2はそれぞれ独立に、アルキル基、又はアリール基を表し、R3〜R10はそれぞれ独立に、水素、アルキル基、アルコキシ基、アルキルチオ基、又はアリール基を表す。〕

(もっと読む)

置換基脱離化合物とそれから得られる有機半導体材料、それを用いた有機電子デバイス、有機薄膜トランジスタおよびディスプレイ装置

【課題】高い有機溶媒溶解性を有し、低いエネルギー付与で有機半導体化合物に変換可能な置換基脱離化合物と、これを用いた有機電子デバイスを提供する。

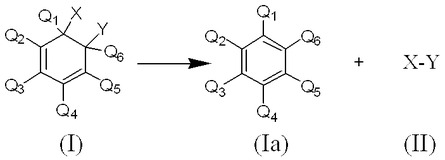

【解決手段】一般式(I)で表され、エネルギー付与により一般式(Ia)で表される化合物と一般式(II)で表される化合物に変換可能なことを特徴とする置換基脱離化合物。

[式(I)、(Ia)、(II)中、XおよびYは水素原子もしくは脱離性置換基を表し、該XおよびYのうち一方は脱離性置換基であり、他方は水素原子である。Q1乃至Q6は水素原子、ハロゲン原子または、一価の有機基である。]

(もっと読む)

炭化珪素トランジスタ装置の製造方法

【課題】微細化と、オン特性を改善する、炭化珪素トランジスタ装置の製造方法の提供。

【解決手段】高濃度n型炭化珪素基板2上に、低濃度n型ドリフト層3と高濃度p型層10をエピタキシャル成長する工程と、高濃度p型層10の一部を除去離間した複数の高濃度p型ゲート領域4を形成する工程と、互いに隣り合った高濃度p型ゲート領域4の間に位置するチャネル領域7、高濃度p型ゲート領域4及びゲート電極領域10の全面を覆う低濃度n型ドリフト層3よりも低い不純物濃度の低濃度n型領域11をエピタキシャル成長する工程と、低濃度n型領域11の一部を除去する工程と、低濃度n型領域11の表面にイオン注入し高濃度n型ソース領域5を形成する工程と、高濃度n型ソース領域5上にソース電極6を、高濃度n型炭化珪素基板2の裏面にドレイン電極1を、ゲート電極領域10にゲート電極8を形成する工程を含む炭化珪素トランジスタ装置の製造方法。

(もっと読む)

半導体装置

【課題】 立ち上がり電圧低減と高耐圧実現の両立を可能とする構造を提案する。

【解決手段】 SiC縦型ダイオードにおいて、カソード電極21と、n++カソード層10と、n++カソード層上のn−ドリフト層11と、一対のp+領域12と、n−ドリフト層11とp+領域12の間に形成され、且つ一対のp+領域12に挟まれたn+チャネル領域16と、n++アノード領域14と、n++アノード領域14とp+領域12に形成されたアノード電極22を備える。

(もっと読む)

縦型AlGaN/GaN−HEMTおよびその製造方法

【課題】確実なノーマリオフ動作する縦型AlGaN/GaN-HEMTおよびその製造方法を提供する。

【解決手段】n+-GaN基板11の表面にn-GaNバッファ層12、UID-GaN層13、UID-AlGaN層14が順次積層され、UID-AlGaN層の表面に形成されたSiN表面保護膜16と、この表面保護膜の開口部を覆うSiN第1ゲート絶縁膜18と、アパーチャ形成用リセス19内に埋め込まれたn-GaNアパーチャ20と、このアパーチャのn+-GaN基板とは反対側表面と第1ゲート絶縁膜とを少なくとも覆うSiN第2ゲート絶縁膜21と、第1ゲートリセス内の第2ゲート絶縁膜の表面に形成されたゲート電極22と、第1ゲートリセスを挟み、UID-AlGaN層の表面に離間して形成されたソース電極23と、n+-GaN基板のUID-AlGaN層とは反対側の表面に形成されたドレイン電極24とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】縦型半導体装置の電流経路の低抵抗化を図る。

【解決手段】半導体装置1は、基板2の上方に形成された、電子ドリフト層4、電子ブロック層5、電子走行層6及び電子供給層7を含む。電子走行層6及び電子供給層7には、電子走行層6内に2DEG16が生成される材料が用いられる。電子ブロック層5には、その開口部9に、絶縁膜10を介してゲート電極11が形成され、電子供給層7には、ソース電極13が接続される。基板2の裏面には、ドレイン電極15が接続される。

(もっと読む)

芳香族化合物、及びこれを用いた有機薄膜、並びにこの有機薄膜を備える有機薄膜素子

【課題】電荷輸送性、安定性に優れた有機半導体材料として有用な芳香族化合物の提供。

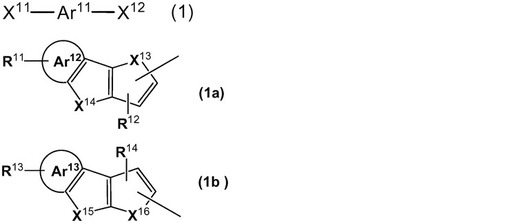

【解決手段】式(1)

[式中、Ar11は、芳香環を含む基を示し、X11及びX12は、式(1a)又は式(1b)で表される基を示す。]で表される芳香族化合物。

(もっと読む)

電子回路装置

【課題】ノーマリオフ型の炭化珪素接合FETはゲートの特性が、使い勝手が悪いという問題がある。これは、ノーマリオフを実現するためにゲート電圧が0Vでオフしていなければならず、かつ、ゲート・ソース間のpn接合に電流が流れないようにオン状態としてはゲート電圧を2.5V程度に抑える必要があるため、実質的にゲート電圧を0Vから2.5Vの間で制御しなければならないためである。従って、閾値電圧からオン状態のゲート電圧までが1Vから2V程度しかなく、ドレイン電流がゲート電圧の変化に非常に敏感であるため、ゲートの制御が難しい。

【解決手段】本願発明は、ノーマリオフ型の炭化珪素接合FETのゲートに、接合FETのゲート容量と同等か少し小さな容量を持つ素子を接続したものである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能で、性能のばらつきが抑制された半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたドレインパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたソースパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下方から上方に向かって径が連続的に拡大された形状であるとともに、下から順にドレイン領域17、ゲート領域18、ドレイン領域17よりも短いソース領域19からなり、ドレイン領域17の周囲には第1の絶縁膜20、ゲート領域18の周囲にはゲート電極21、ソース領域19の周囲には第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能で、性能のばらつきが抑制された半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下方から上方に向かって径が連続的に拡大された形状であるとともに、下から順にソース領域17、ゲート領域18、ドレイン領域19からなるとともに、ドレイン領域19は、ソース領域17よりも長く形成され、ソース領域17の周囲には第1の絶縁膜20、ゲート領域18の周囲にはゲート電極21、ドレイン領域19の周囲には第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

窒化物電子デバイスを作製する方法

【課題】ゲートリーク電流を低減できる、窒化物電子デバイスを作製する方法を提供する。

【解決手段】時刻t0で基板生産物を成長炉に配置した後に、摂氏950度まで基板温度を上昇する。基板温度が十分に安定した時刻t3でトリメチルガリウム及びアンモニアを成長炉に供給して、i−GaN膜を成長する。時刻t5で基板温度が摂氏1080度に到達する。基板温度が十分に安定した時刻t6でトリメチルガリウム、トリメチルアルミニウム及びアンモニアを成長炉に供給して、i−AlGaN膜を成長する。時刻t7でトリメチルガリウム及びトリメチルアルミニウムの供給を停止して成膜を停止した後に、速やかに、成長炉へアンモニア及び水素の供給を停止すると共に窒素の供給を開始して、成長炉のチャンバ中においてアンモニア及び水素の雰囲気を窒素の雰囲気に変更する。窒素の雰囲気が形成された後に、時刻t8で基板温度の降下を開始する。

(もっと読む)

電界効果トランジスタ

【課題】 第1半導体層と第2半導体層とのヘテロ接合により第1半導体層に二次電子ガス層を生じさせつつ、ソース電極とドレイン電極との間の通電状態を切り換えるためのゲート電圧のしきい値を所定の値に調整することができる電界効果トランジスタを提供する。

【解決手段】 電界効果トランジスタ10では、サファイア基板11上に、i型のGaNからなるGaN層13と、i型のGaNと格子定数が異なるi型のAlGaNからなるAlGaN層14と、i型のAlGaNよりもエッチングレートが小さいi型のAlInNからなるAlInN層15とが順に形成されている。AlInN層15の上端から途中まで伸びている溝25が形成されており、その溝25の底部の少なくとも一部にゲート電極26がショットキー接続されている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部の周辺を含めてn+型SiC基板1の外縁部においてn+型ソース領域4が除去されると共に、トレンチ6の先端部においてn-型チャネル層7および第2ゲート領域8が除去された凹形状とする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】高耐圧および高電流のスイッチング動作が可能で、かつ製造が容易なFETを提供する。

【解決手段】半導体薄体の一の主表面に設けられた、第1導電型のソース領域(1)と、第1導電型のチャネル領域(10)と、チャネル領域を限定する第2導電型の限定領域(5)と、他の主表面に設けられた第1導電型のドレイン領域(3)と、厚さ方向に連続する第1導電型のドリフト領域(4)とを備え、ドリフト領域(4)およびチャネル領域(10)の不純物濃度は、ソース領域(1)、ドレイン領域(3)および限定領域(5)の不純物濃度よりも低く、チャネル領域(10)の不純物濃度はドリフト領域(4)の不純物濃度よりも低い。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能な半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下から順にソース領域18、ゲート領域19、ソース領域よりも径が細いドレイン領域17からなり、ソース領域18の周囲には第1の絶縁膜20、ゲート領域19の周囲にはゲート電極21、ドレイン領域17の周囲には所定の空間を介して第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

21 - 40 / 155

[ Back to top ]