Fターム[5F102GC08]の内容

接合型電界効果トランジスタ (42,929) | ゲート配置 (2,808) | 縦型FETの埋込みゲート (155)

Fターム[5F102GC08]に分類される特許

61 - 80 / 155

半導体装置

【課題】縦型のGaN系半導体装置の耐圧性能を向上する。

【解決手段】 n−型のGaN層6にp型のGaN層10が積層されており、p型のGaN層10にp型のGaN層10を貫通するアパーチャー28が形成されており、そのアパーチャー28にn型のGaN層26が充填されている。n型のGaN層6の一部に浮遊電流ブロック領域8が形成されている。半導体装置のオフ時に、浮遊電流ブロック領域8からn型のGaN層6に向かって空乏層が広がり、アパーチャー28を充填しているn型のGaN層26の電位が低下し、ゲート絶縁膜20の表面と裏面の間にかかる電位差が減少する。半導体装置の耐圧性能が改善される。浮遊電流ブロック領域8は、p型領域であってもよく、深い準位をもった領域であってもよい。

(もっと読む)

窒化物半導体装置

【課題】 ノーマリオフ特性を備えている窒化物半導体装置2を提供する。

【解決手段】 窒化物半導体装置2では、アンドープのGaNを材料とする窒化物半導体下層8の表面に、アンドープのAlGaNを材料とする窒化物半導体層10が積層されている。窒化物半導体層10は、窒化物半導体下層8よりも大きなバンドギャップを備えており、窒化物半導体下層8に対してヘテロ接合している。窒化物半導体層10の表面にはゲート絶縁膜16が形成されている。ゲート絶縁膜16は、窒化アルミニウム膜15で形成されている部分と、酸素又はシリコンを含む絶縁物質14で形成されている部分を含んでいる。窒化アルミニウム膜15が形成されている範囲W2はゲート電極18が形成されている範囲W1に含まれる関係にある。

(もっと読む)

トランジスタ

【課題】 ノーマリーオフ型であるとともに、ゲート閾値電圧のばらつきが小さいHEMT型のトランジスタを提供する。

【解決手段】 このトランジスタは、p型領域と、チャネル領域と、バリア領域と、絶縁膜と、ゲート電極を備えている。チャネル領域は、n型またはi型であり、p型領域の表面に接しており、第1チャネル領域と第2チャネル領域を有している。バリア領域は、第1チャネル領域の表面とヘテロ接合している。絶縁膜は、第2チャネル領域の表面、及び、バリア領域の表面に接している。ゲート電極は、絶縁膜を介して第2チャネル領域及びバリア領域に対向している。第1チャネル領域と第2チャネル領域は、電流経路において直列に配置されている。

(もっと読む)

電界効果トランジスタ

【課題】電流容量および耐電圧を大きくしたノーマリオフの縦型構成の電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ1は、半導体基板10と、半導体基板10に積層された窒化物系III−V族化合物半導体層20と、窒化物系III−V族化合物半導体層20から積層方向に交差する横方向へ成長した横方向成長領域22と、半導体基板10の裏面に形成されオーミック性を有する第1電極31(ドレイン電極)と、窒化物系III−V族化合物半導体層20の表面に形成されオーミック性を有する第2電極32(ソース電極)と、窒化物系III−V族化合物半導体層20の積層方向で第1電極31と第2電極32との間での電流路となる通電領域21と、横方向成長領域22に接触させて形成され通電領域21での通電状態を制御する第3電極33(ゲート電極)とを備える。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】p型コンタクト抵抗を低減でき、素子のスイッチングスピードを下げないようにすることができる炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】半導体基板6のうち第1〜第3コンタクトホール12〜14から露出した部位に、炭化珪素とAlとNiとが反応してそれぞれ形成された合金層15が設けられている。この合金層15におけるAlとNiとの元素組成比は1:4.6〜1:10.6であり、合金層15の厚さは20nm以上100nm以下になっている。これにより、合金層15と半導体基板6とがオーミック接触となり、低いコンタクト抵抗率を得ることが可能となる。

(もっと読む)

ワイドバンドギャップ半導体装置

【課題】JFETが形成されるセル領域とダイオード形成領域との間の絶縁耐圧を向上でき、耐圧の最適設計が行える構造のSiC半導体装置を提供する。

【解決手段】電界緩和領域R3に備えたp型領域9bとn型領域8bとにより構成されるPN分離部により、セル領域R1とダイオード形成領域R2の間の素子分離を行う。これにより、トレンチ内に酸化膜を配置して素子分離を行う場合と比べて、素子分離用の酸化膜が絶縁破壊されることが無いため、JFETが形成されるセル領域R1とダイオード形成領域R2との間の絶縁耐圧を向上できる。このため、素子分離に酸化膜を用いる場合と比べて耐圧の最適設計を行うことが可能となる。

(もっと読む)

半導体装置

【課題】 一対の主電極の間に設けられたゲート電極を有する半導体装置において、高い耐圧を確保しながらオン抵抗を低くする技術を提供する。

【解決手段】 半導体装置100は、一対の主電極2,22間に設けられたゲート電極10を備えている。ゲート部10は絶縁ゲート電極部10aとショットキー電極部10bを有している。半導体装置100は、主電極2に接続するコンタクト領域18と、コンタクト領域18に隣接するチャネル半導体領域8と、チャネル半導体領域8の裏面に接しているp型半導体領域20と、チャネル半導体領域8とp型半導体領域20の両者に隣接するドリフト半導体領域12を備えている。絶縁ゲート電極部10aは、ゲート絶縁膜4を介してコンタクト領域18の表面に対向している。ショットキー電極部10bは、ドリフト半導体領域12の表面に直接的に接触している。

(もっと読む)

へテロ接合を有する半導体装置とその製造方法

【課題】 オン抵抗が低減されたヘテロ接合を有する半導体装置を提供すること。

【解決手段】 半導体装置10は、窒化ガリウムの半導体下層30と、半導体下層30の表面に設けられている窒化ガリウムアルミニウムの半導体上層40と、半導体上層40の表面に設けられている絶縁ゲート部55を備えている。半導体下層30と半導体上層40は、ヘテロ接合72を構成している。半導体上層40は、マグネシウムを含むp型であることを特徴としている。

(もっと読む)

へテロ接合を有する半導体装置とその製造方法

【課題】 ノーマリオフ動作を実現するとともに、電流コラプス現象が抑制されたヘテロ接合を有する半導体装置を提供すること。

【解決手段】 半導体装置10は、窒化ガリウムの半導体下層30と、半導体下層30の表面に設けられている窒化ガリウムアルミニウムの半導体上層40と、半導体上層40の表面に設けられている絶縁ゲート部55を備えている。半導体下層30と半導体上層40は、ヘテロ接合72を構成している。半導体上層40は、中間領域にマグネシウムを含むδドープ層44を有する。

(もっと読む)

有機半導体材料及びその製造方法、並びに有機電子デバイス

【課題】高いキャリア移動度と安定性を有し、容易なプロセスで作製可能な有機半導体材料及び有機デバイスを提供する。

【解決手段】下記一般式で表されるポルフィリン2量体を含む有機半導体材料、及び、ビシクロ構造を有する前駆体としてのポルフィリン2量体を溶媒に溶解した溶液を基板上に塗布し、加熱することにより、上記ポルフィリン2量体に変換する有機半導体材料の製造方法、並びに、半導体層と2以上の電極とを有する有機電子デバイスにおいて、該半導体層が上記有機半導体材料を含む有機電子デバイス。 (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】導電型が異なる不純物層を順に形成する場合に、先に形成した不純物層へのドーピング用の不純物が後に形成する不純物層に混入されることを抑制する。

【解決手段】p+型第2ゲート層8を形成してから次のロットでn-型チャネル層7を形成する工程に移行する前の工程として、n-型チャネル層7の成長温度よりも高い温度においてCVD装置内のSiCコーティングの表面をエッチングするエッチング処理と、エッチング処理後にCVD装置内をn-型チャネル層7の成長温度よりも高い温度で加熱する加熱処理とを行う第1の残留不純物除去工程と、n-型チャネル層7の成長レートよりも早い成長レートにて、後工程で成長させるn-型チャネル層7と同じ導電型の不純物層をカーボン容器の内壁面のSiCコーティングの表面にデポジションするデポジション工程を行う第2の残留不純物除去工程を行う。

(もっと読む)

フルオレン系高分子化合物及び有機薄膜素子

【課題】電荷輸送性が優れた高分子化合物、及びその製造方法を提供する。

【解決手段】下記式(1)で示される繰り返し単位を有する高分子化合物

〔式中、R1は、置換基を有していてもよいアリール基又は置換基を有していてもよいヘテロアリール基を表す。aは1〜3の整数を表す。R1が複数存在する場合、それらは同一でも異なっていてもよい。〕;特定の化合物を縮合重合させる工程を有する前記高分子化合物の製造方法。

(もっと読む)

スイッチング回路

【課題】、接合型電界効果トランジスタ(JFET)の高温動作時のオン抵抗を低減して、高温時の動作特性を改善すること。

【解決手段】出力切替回路34は、温度検出装置33によって検出された温度が所定の閾値温度以上であるとき、第2の駆動回路32に出力切替指示を与える。これにより、第2の駆動回路は、MOSFET35を駆動して、JFET10に立ち上がり電圧(順方向降下電圧)VF以上のゲート電圧VGSが印加され、JFETはバイポーラ動作される。これにより、高温時のJFET10のオン抵抗の増加を抑制できる。

(もっと読む)

III族窒化物半導体装置とその製造方法

【課題】 縦型のIII族窒化物半導体の製造過程において、半導体構造の表面を平坦化する処理を利用することができるとともに、その後の工程で電極等を形成する際に半導体構造に対して高い精度で位置合わせできる製造方法を提供する。

【解決手段】 n型の窒化ガリウム基板2の表面の一部にアライメントマーク4を形成する。次に、窒化ガリウム基板2の表面とアライメントマーク4を覆うようにn型の第1の窒化ガリウム層6を結晶成長させる。次に、第1の窒化ガリウム層6の一部をアライメントマーク4に達しない深さまでエッチングする。次に、第1の窒化ガリウム層6の表面にp型の第2の窒化ガリウム層8を形成する。次に、第1の窒化ガリウム層6の凸部6aが露出するまで表面を平坦化する。第1の窒化ガリウム層6の表面を平坦化した後の工程でも、アライメントマークを認識することができる。

(もっと読む)

多環縮環化合物、多環縮環重合体及びこれらを含む有機薄膜

【課題】高い電荷輸送性と、溶媒への溶解性に優れる多環縮環重合体を提供する。

【解決手段】式(1)及び又は式(2)の構造単位を有する多環縮環重合体。

[式中、X1及びX2は、酸素原子、硫黄原子又はセレン原子を示す。]

(もっと読む)

分岐型化合物、これを用いた有機薄膜及び有機薄膜素子

【課題】電荷輸送性に優れる両極性の有機半導体として利用可能な分岐型化合物の提供。

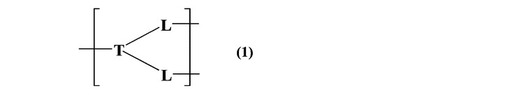

【解決手段】コア部と、該コア部に結合した少なくとも1つの側鎖部と、末端と、から構成される分岐型化合物であって、上記側鎖部の少なくとも1つは、下記一般式(1)で表される繰返し単位が1又は2以上繰り返しており(但し、コア部と結合する前記繰返し単位においては、Tがコア部に結合しており、2以上繰り返す前記繰返し単位においては、LがTに結合している。)、Lは、共役形成単位が複数連結して構成され、上記共役形成単位として少なくとも一つのチエニレン単位を含み、Lの末端(Tと結合していない側のLの末端)に存在する基は、少なくとも2つがアクセプター性の基である、分岐型化合物。

(式中、Lは置換基を有していてもよい2価の有機基を示し、Tは置換基を有していてもよい3価の有機基を示す。)

(もっと読む)

チップ内隣接構成デュアル静電誘導トランジスタ及びこれを用いたオーディオ用パワーアンプ回路

【課題】解決しようとする課題は、差動増幅器の入力段の対構成の差動トランジスタに最適な特性の揃ったディュアル静電誘導トランジスタを提供して、トランジスタ製造上の選別を容易にし、対形成不良を少なくし、回路製作上の調整作業を容易にすることである。

【解決手段】本発明では、半導体の1ウェーハ内の隣同士に隣接して、対構成の同一導電型、同一サイズの静電誘導トランジスタを構成して、差動増幅器の入力段用には、1チップとして組立し提供したものである。

(もっと読む)

有機電子デバイス及びその作製方法

【課題】高い移動度を有し光起電力を利用する有機電子デバイス、該デバイスを容易なプロセスで作製する方法を提供する。

【解決手段】従来とは異なる特定の環状構造のビシクロ化合物を溶媒に溶解した溶液を基板上に塗布することにより膜を製膜し、次いで加熱等の外部作用を加えることで、該ビシクロ化合物からエチレン誘導体を脱離させることにより基板上で変換された化合物を有機半導体として用いてなる光起電力を利用する有機電子デバイス、及びその作製方法。

(もっと読む)

電界効果トランジスタ

実施の形態に係る自己修復型電界効果トランジスタ(FET)装置は、各々がヒューズリンクを有する複数のFETセルを含む。ヒューズリンクは、対応するセルにおける高電流イベント時に飛ぶように調節される。 (もっと読む)

接合型FET

【課題】 従来の接合型FETにおいては、分離領域で囲まれたチャネル領域は1つの連続した領域であった。このため、ゲート領域の周囲において所望の相互コンダクタンスgmが得られ、且つオフ時のピンチオフが十分な不純物濃度を選択すると、チャネル領域とp−型半導体層とのpn接合耐圧が、静電エネルギーを逃がすには高すぎて、pn接合がブレークダウンする以前に素子領域が破壊する問題があった。

【解決手段】 本発明では、ゲート領域を第1n型不純物領域に設け、ソース領域およびドレイン領域をそれぞれ第2n型不純物領域に設ける。第1n型不純物領域と第2n型不純物領域は独立して不純物濃度を選択できる。これにより、互いに影響を与えることなく、所望の相互コンダクタンスgmと、所望の静電耐圧が得られるように、これらを独立して制御することができる。

(もっと読む)

61 - 80 / 155

[ Back to top ]