Fターム[5F102GJ02]の内容

接合型電界効果トランジスタ (42,929) | 基板 (5,097) | 半導体材料(半絶縁性材料も含む) (3,925) | 4族 (2,421)

Fターム[5F102GJ02]の下位に属するFターム

Si (1,156)

Fターム[5F102GJ02]に分類される特許

201 - 220 / 1,265

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体層とゲート電極との間に絶縁膜が形成された半導体装置の信頼性を高める。

【解決手段】基板の上方に形成された半導体層と、前記半導体層上に形成された絶縁膜と、前記絶縁膜上に形成された電極と、を有し、前記絶縁膜は炭素を主成分とするアモルファス膜を含むものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート動作に関与する結晶表面における表面電荷蓄積を大幅に低減し、ピンチオフ特性が得られる、高性能のInN系FETを提供すること。

【解決手段】チャネル層としてInN系半導体を含む電界効果トランジスタである半導体装置であって、InN系半導体でなるチャネル層2の表面(c面)に、段差を形成して窒化物半導体の六方晶結晶のa面もしくはm面でなる側壁面2aを形成し、この側壁面2aにゲート電極6が配置され、ゲート電極6を挟むようにソース電極3とドレイン電極4がc面上に形成されている。

(もっと読む)

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、トランジスタの特性を低下させることなく高い密度のドレイン電流が実現できるようにする。

【解決手段】主表面を(0001)面とした第1窒化物半導体からなるチャネル層101と、チャネル層101の上に形成された第1窒化物半導体より大きなバンドギャップエネルギーの窒化物半導体からなる第1障壁層102と、ゲート電極104が形成されたゲート形成領域121を挟んだソース形成領域122およびドレイン形成領域123の第1障壁層102の上に形成され、第2窒化物半導体より大きなバンドギャップエネルギーの第3窒化物半導体からなる第2障壁層105および第3障壁層106と、第2障壁層105および第3障壁層106の上に形成された第2窒化物半導体からなる第4障壁層107および第5障壁層108とを備える。

(もっと読む)

エネルギー障壁を有するヘテロ接合トランジスタおよび関連する方法

【課題】チャネル内へのキャリアの閉じ込めを改善すること。

【解決手段】へテロ接合トランジスタは、III族窒化物を含むチャネル層14と、チャネル層の上のIII族窒化物を含む障壁層16と、チャネル層14が障壁層16とエネルギー障壁38との間にあるようにした、チャネル層14の上のインジウムを有するIII族窒化物の層を含むエネルギー障壁とを備えることができる。障壁層16は、チャネル層よりも大きなバンドギャップを有することができ、エネルギー障壁38のインジウム(In)の濃度はチャネル層14のインジウム(In)の濃度よりも高い可能性がある。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】所望の不純物濃度と、高い結晶性とを有するドリフト層を有する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】バッファ層31は、基板30上に設けられ、不純物を含有する炭化珪素から作られ、1μmより大きく7μmより小さい厚さを有する。ドリフト層32は、バッファ層31上に設けられ、バッファ層31の不純物濃度よりも小さい不純物濃度を有する炭化珪素から作られている。

(もっと読む)

シングルゲートまたはマルチゲートフィールドプレート製造

【課題】誘電性材料に与えるダメージの少ない乾式または湿式エッチングプロセスを用いることなく、フィールドプレートされたデバイスを実現できるシングルゲートまたはマルチゲートフィールドプレートの製造方法を提供する。

【解決手段】電界効果トランジスタ10は、ソースオーミックコンタクト12と、ドレインオーミックコンタクト14、ゲートコンタクト16、および活性領域18を含む。(1)デバイスの真性および外因性領域に誘電性材料を堆積または成長させ、(2)乾式または湿式エッチングプロセス、あるいはリフトオフプロセスで誘電性材料をパターニングし、(3)パターニングされた誘電性材料上にフィールドプレートを蒸着させるステップを包含する方法。

(もっと読む)

III族窒化物半導体電子デバイス、エピタキシャル基板、及びIII族窒化物半導体電子デバイスを作製する方法

【課題】半導体積層内の電流経路からゲート電極を隔てる半導体層を厚くできるIII族窒化物半導体電子デバイスを提供する。

【解決手段】第2の半導体層15は第1の半導体層13上に設けられる。ゲート電極17は第2の半導体層15の上に設けられる。第1の半導体層13は、AlXGa1−XN(0<X≦1)からなる半導体表面21aの上に設けられる。第2のIII族窒化物半導体材料のバンドギャップE15は第1のIII族窒化物半導体材料のバンドギャップE13より大きい。第1の半導体層13の第1のIII族窒化物半導体材料はAlXGa1−XNと異なり、第1の半導体層13は歪みを内包する。また、第2の半導体層15の厚さT15は、無歪みの第1のIII族窒化物半導体材料の組成と、第2のIII族窒化物半導体の組成により規定される臨界膜厚より大きい。また、第1の半導体層13は、歪みを内包すると共に、半導体表面21aのAlXGa1−XNの上において格子緩和している。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

ノーマリオフ型パワーJFETの製造方法

【課題】SiC系JFETにおいて、トレンチゲート領域間を高精度に制御するため、ソース領域内にゲート領域を形成する必要がある。これにより増加するソース領域、ゲート領域間高濃度PN接合による接合電流を削減できる半導体装置を提供する。

【解決手段】ノーマリオフ型パワーJFETの製造方法であって、N型SiC1sの表面に、Nエピタキシャル下層1ea、中層1eb、上層1ec等複数層を形成し、表面には複数のソース層9、及びPゲート領域4が設けられる。ゲート領域はアクティブ領域3の外端部に接するように、下層、中層、上層のPエッジターミネーション領域7a、7b、7cが設けられる。裏側種面には、高濃度ドレイン層8が形成される。

(もっと読む)

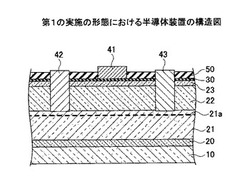

高電子移動度トランジスタ(HEMT)

【課題】高周波特性を改善する。

【解決手段】III族窒化物系高電子移動度トランジスタ(HEMT)20は、GaNバッファ層26を備えており、Ganバッファ層26上にAlyGa1−yN(y=1又は≒1)層28がある。AlxGa1−xN(0≦x≦0.5)バリア層30が、GaNバッファ層26の反対側でAlyGa1−yN層28上にあり、該層28のAl濃度は、バリア層30よりも高い。GaNバッファ層26とAlyGa1−yN層28との間の界面に2DEG38が形成されている。バリア層30上に、ソース、ドレイン、及びゲート・コンタクト32、34、36が形成されている。また、AlyGa1−yN層28の反対側において、バッファ層26に隣接する基板22も含み、GaNバッファ層26と基板22との間に、核生成層24を含むことができる。

(もっと読む)

半導体素子

【課題】低オン抵抗で、ノーマリーオフ動作を有し、高信頼性の半導体素子を提供する。

【解決手段】半導体素子1Aは、支持基板10上にN面成長されたAlXGa1−XN(0≦X<1)を含む第1半導体層11と、前記第1半導体層上に形成されたノンドープもしくは第1導電形のAlYGa1−YN(0<Y≦1、X<Y)を含む第2半導体層15と、前記第2半導体層上に形成されたAlZGa1−ZN(0≦Z<1、Z<Y)を含む第3半導体層16と、を備える。半導体素子1Aは、第3半導体層16に接続された第1主電極20と、第3半導体層16に接続された第2主電極21と、第1主電極と第2主電極とのあいだの第3半導体層16の上に設けられたゲート電極31と、を備える。第3半導体層16の厚さは、ゲート電極31下において選択的に薄い。

(もっと読む)

半導体素子

【課題】低オン抵抗および高信頼性を有する半導体素子を提供する。

【解決手段】半導体素子1Aは、第1導電形層11が表面に選択的に設けられた半絶縁性基板10と、前記半絶縁性基板および前記第1導電形層の上に設けられたノンドープAlXGa1−XN(0≦X<1)を含む第1半導体層15と、前記第1半導体層上に設けられたノンドープもしくは第2導電形のAlYGa1−YN(0<Y≦1、X<Y)を含む第2半導体層16とを備える。半導体素子は、前記第2導電形層11に接続された第1主電極20と、前記第2半導体層16に接続された第2主電極と21、前記第1主電極と、前記第2主電極と、のあいだの前記第2半導体層の上に設けられた制御電極30とを備える。前記第1導電形層11は、前記制御電極30の下に設けられている。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置

【課題】素子温度の上昇を抑制する半導体装置を提供する。

【解決手段】動作周波数fで動作可能な半導体装置であって、熱拡散率Dの基板と、基板上に形成され、ワイドギャップ半導体素子で横型素子の第1のトランジスタで構成される第1の素子ユニット12と、基板上に第1の素子ユニット12に隣接して形成され、第1のトランジスタと異なるタイミングで動作するワイドギャップ半導体素子で横型素子の第2のトランジスタで構成される第2の素子ユニット14とを備え、第1の素子ユニット12の重心と、第2の素子ユニット14の重心との距離が熱拡散長(D/πf)1/2の2倍以下であることを特徴とする半導体装置。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】特性の安定化を達成できる窒化物半導体装置及びその製造方法を提供する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第3半導体層5、第4半導体層6、第1電極10、第2電極8及び第3電極9を備える。第1半導体層3、第2半導体層4、第3半導体層5及び第4半導体層6は、窒化物半導体を含む。第2半導体層4は、第1半導体層3の禁制帯幅以上の禁制帯幅を有する。第3半導体層5は、GaNである。第4半導体層6は、第3半導体層5の上において一部に隙間を有して設けられ、第2半導体層4の禁制帯幅以上の禁制帯幅を有する。第1電極10は、第3半導体層5の上において第4半導体層6が設けられていない部分に設けられる。第2電極8及び第3電極9は、第4半導体層6の上において、第1電極10の一方側及び他方側にそれぞれ設けられ、第4半導体層6とオーミック接合している。

(もっと読む)

半導体装置の製造方法

【課題】半導体の表面の酸化物を含む不純物を、エッチングあるいは、他の層を積層する前に除去する。

【解決手段】第1の半導体層110の少なくとも一部に接し、第1の半導体層110に含まれる不純物の固溶度が、第1の半導体層110より高い第1の犠牲層を形成する第1犠牲層形成工程と、第1の犠牲層および第1の半導体層をアニールするアニール工程と、第1の犠牲層をウェットプロセスで除去する除去工程と、第1の半導体層の少なくとも一部を覆う絶縁層120を形成する工程および第1の半導体層の一部をエッチングする工程の少なくとも一の工程と、第1の半導体層に電気的に接続された電極層126を形成する電極形成工程とを備える。

(もっと読む)

電界効果型トランジスタ

【課題】耐圧向上を図った電界効果型トランジスタを提供する。

【解決手段】電界効果型トランジスタは、基板101上に、核形成層として機能する第一の窒化物半導体層102と、第一の窒化物半導体層102よりも電子親和力の大きい第二の窒化物半導体層103と、第二の窒化物半導体層103よりも電子親和力の小さい第三の窒化物半導体層104とを順に積層して形成されている。第三の窒化物半導体層104上には中間層106を介して形成されたソース電極107、ドレイン電極108、ゲート電極109が設けられている。第一の窒化物半導体層102には、ホウ素が不純物としてドーピングされている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部をp+型領域20にて埋め尽くすようにする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

多重フィールドプレートトランジスタ

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能

するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース、ドレ

イン、およびゲートを含む。第1のスペーサ層が、活性領域の上方でソースとゲートの間

にあり、第2のスペーサ層が、活性領域の上方でドレインとゲートの間にある。第1のス

ペーサ層上の第1のフィールドプレート、及び第2のスペーサ層上の第2のフィールドプ

レートが、ゲートに接続される。第3のスペーサ層が、第1のスペーサ層、第2のスペー

サ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、

第3のフィールドプレートが、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

炭化ケイ素金属半導体電界効果トランジスタ及び炭化ケイ素の金属半導体電界効果トランジスタを製造する方法

【課題】深いレベルのドーパントがほとんど存在しない半絶縁性のSiC基板上にMESFETを形成することにより、バックゲート効果が減少された、SiCのMESFETを提供する。

【解決手段】半絶縁性の基板上10に選択的にドープされたP型の炭化珪素の層13、及びN型のエピタキシャル層14を積層し、背面ゲート効果を減少させる。また2つの凹部を有するゲート構造体も備える。これにより、出力コンダクタンスを1/3に減少することができ、また電力のゲインを3db増加することができる。クロム42をショットキーゲート接点として利用することもでき、酸化物−窒化物−酸化物(ONO)の保護層60を利用して、MESFET内の表面効果を減少させる。また、ソース及びドレインのオーム接点をn型チャネル層上に直接形成して、これにより、n+領域を製造する必要がなくなる。

(もっと読む)

201 - 220 / 1,265

[ Back to top ]