Fターム[5F102GJ02]の内容

接合型電界効果トランジスタ (42,929) | 基板 (5,097) | 半導体材料(半絶縁性材料も含む) (3,925) | 4族 (2,421)

Fターム[5F102GJ02]の下位に属するFターム

Si (1,156)

Fターム[5F102GJ02]に分類される特許

161 - 180 / 1,265

半導体装置およびその製造方法

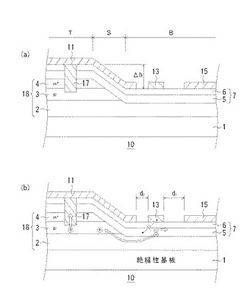

【課題】 高周波特性を確保し、サイズを小型化し、かつ製造が容易な、正孔の蓄積を解消できる、耐圧性に優れた、半導体装置等を提供する。

【解決手段】 ヘテロ接合電界効果トランジスタ(HFET:Hetero-junction Field Effect Transistor)であって、非導電性基板1上に位置する、チャネルとなる二次元電子ガス(2DEG:2 Dimensional Electron Gas)を形成する再成長層7(5,6)と、再成長層に接して位置する、ソース電極11、ゲート電極13およびドレイン電極15を備え、ソース電極11が、ゲート電極13に比べて、非導電性基板1から遠い位置に位置することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】膜の形成によって生じる半導体基板の反りを緩和できる、半導体装置の製造方法を提供する。

【解決手段】SiC半導体基板10の主面上にイオン注入用マスク材18を形成する。マスク材は半導体基板とは異なる熱膨張係数を有する。レジスト膜20をマスクとしてドライエッチングにより複数の装置形成領域の間の領域上(ダイシングライン)14に切欠き部16aを有するマスク用膜16を形成する。イオン注入などの工程を経て半導体装置を形成後、ダイシングラインに沿って各装置形成領域に分離する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ピンチオフ特性を維持しながら動作効率を向上することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板11と、基板11上方に形成された電子走行層12と、電子走行層12上方に形成された電子供給層13と、電子供給層13上方に形成されたソース電極15s及びドレイン電極15dと、電子供給層13上方で、ソース電極15s及びドレイン電極15dの間に形成された第1のゲート電極15g−1及び第2のゲート電極15g−2と、が設けられている。ゲート電極15g−1の仕事関数は、第2のゲート電極15g−2の仕事関数よりも低い。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

半導体装置

【課題】窒化物半導体により、反転型のHEMTが構成された半導体装置において、半導体装置の形成を容易としつつ2DEGを効果的に形成する。

【解決手段】窒化物半導体からなる下地層15の(0001)面上に、窒化物半導体からなる電子供給層17、窒化物半導体からなる電子走行層19の順に積層され、電子走行層19における電子供給層17と反対の面上に、ゲート電極21、ソース電極23、及びドレイン電極25が設けられている。そして、電子走行層19における電子供給層17側に、二次元電子ガスが形成される。このような反転型のHEMTが構成された半導体装置10において、分極の正方向を[0001]方向とした場合、電子供給層17の自発分極とピエゾ分極の和P2が、電子走行層19の自発分極とピエゾ分極の和P1よりも大きくなっている。

(もっと読む)

パッシブ発振防止用のIII族窒化物トランジスタ

【課題】パッシブ発振制御を有する半導体素子を提供する。

【解決手段】ソース電極202、ゲート電極208およびドレイン電極204を有するIII族窒化物トランジスタ200を含む。ダンピング抵抗器270がパッシブ発振制御をIII族窒化物トランジスタ200に提供するように構成される。ダンピング抵抗器270が少なくとも一つの集中抵抗器R1を含む。

(もっと読む)

半導体基板、電界効果トランジスタ、半導体基板の製造方法および電界効果トランジスタの製造方法

【課題】DWB法における貼り合わせ時にIII-V族化合物半導体層が受けるダメージを小さくするとともに、受けたダメージの影響および界面準位の影響を低く抑え、高いキャリアの移動度を有するIII-V族MISFETを提供する。

【解決手段】ベース基板102と第1絶縁体層104と半導体層106とを有し、ベース基板102、第1絶縁体層104および半導体層106が、ベース基板102、第1絶縁体層104、半導体層106の順に位置し、第1絶縁体層104が、アモルファス状金属酸化物またはアモルファス状金属窒化物からなり、半導体層が、第1結晶層108および第2結晶層110を含み、第1結晶層108および第2結晶層110が、ベース基板102の側から、第1結晶層108、第2結晶層110の順に位置し、第1結晶層108の電子親和力Ea1が、第2結晶層110の電子親和力Ea2より大きい半導体基板を提供する。

(もっと読む)

III族窒化物半導体電子デバイス、エピタキシャル基板、及びIII族窒化物半導体電子デバイスを作製する方法

【課題】チャネル層及びバリア層のAl組成差を増大させてトランジスタ特性を改善可能な構造を有するIII族窒化物半導体電子デバイスを提供する。

【解決手段】第1の半導体層13は、歪みを含む。第1の半導体層13の歪んだAlYGa1−YNの格子定数d(13)は、無歪みのAlYGa1−YNに固有の格子定数d0(13)とAlXGa1−XNの格子定数d(21)との間の中間値を有する。歪んだAlYGa1−YNの格子定数d(13)と無歪みのAlZGa1−ZNに固有の格子定数d0(15)との差△1は、格子定数d0(15)と格子定数d0(13)との差△2より小さくなる。差分(△2−△1)に応じて、歪んだAlYGa1−YN上に成長可能な歪んだAlZGa1−ZNのAl組成を増加でき、AlYGa1−YNとAlZGa1−ZNのAl組成差を0.5以上にできる。

(もっと読む)

半導体装置及びその製造方法

【課題】オン抵抗が小さく、またオフ容量が低い、デュアルゲートを備えた電界効果トランジスタを提供する。

【解決手段】第1又は第2のゲート電極8は、ソース電極4側又は前記ドレイン電極5側に延びる第1のひさし部61と、第2又は第1のゲート電極8側に延びる第2のひさし部62とを有し、第2のひさし部62の長さが第1のひさし部61の長さより短い。

(もっと読む)

トランジスタデバイスおよび高電子移動度トランジスタ(HEMT)

【課題】デバイス利得、帯域幅、および動作周波数が増加するトランジスタを提供する。

【解決手段】第1のスペーサ層28が、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間の活性領域の表面の少なくとも一部の上にある。ゲート電極24は、ソース電極20とドレイン電極22に向かって延在する一般的にT字型の頂部34を備える。フィールドプレート32は、スペーサ層28の上であって、ゲート頂部34の少なくとも1つの区域のオーバーハングの下にある。第2のスペーサ層30は、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間にある第1のスペーサ層28の少なくとも一部の上と、フィールドプレート32の少なくとも一部の上に形成される。少なくとも1つの導電性経路が、フィールドプレート32をソース電極20またはゲート電極24に電気的に接続する。

(もっと読む)

パッケージ

【課題】電流容量が高く、かつ生じる応力が低減されてクラックの発生が抑制され、信頼性の高いパッケージを提供する。

【解決手段】パッケージ外壁16と、パッケージ外壁16を貫通する貫通孔と、貫通孔にはめ込まれた凸状フィードスルー25と、凸状フィードスルー25に固定され端子電極21bとを備え、端子電極21bは、相対的に線熱膨張率は低いが抵抗率が高い第1の金属層90と、相対的に線熱膨張率は高いが抵抗率が低い第2の金属層80a,80bとを備える。

(もっと読む)

半導体装置の製造方法

【課題】製造工程の効率化とパッシベーション膜の剥離の抑制とが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、金を含む配線30a及び配線30bを形成する工程と、配線30a及び配線30bに接して、窒化シリコン膜32をプラズマ気相成長する工程と、窒化シリコン膜32の製膜レートよりも大きな製膜レートのもと、窒化シリコン膜32に接し、窒化シリコン膜32よりもシリコン組成比が小さい窒化シリコン膜22をプラズマ気相成長する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置

【課題】マルチフィンガーFETセル内のループ発振を抑制させ、かつチップ面積の増大を抑制する。

【解決手段】ユニットフィンガーの並列接続からなるマルチフィンガー単位FETセルと、マルチフィンガー単位FETセルのゲートフィンガーを並列接続する指定ゲートバスラインと、指定ゲートバスラインに接続されたゲート引き出しラインとを備え、ゲート引き出しラインと指定ゲートバスラインの接続点をマルチフィンガー単位FETセル内の中心からずらすことによって、接続点の一方に接続されたゲートフィンガー数が、他方に接続されたゲートフィンガー数よりも多くする。

(もっと読む)

MMIC用パッケージ

【課題】チップサイズの大きい高周波部品(MMIC)とパッケージ端子間を接続するインダクタンス成分を抑制し、高周波特性を改善したMMIC用パッケージを提供する。

【解決手段】導体ベースプレート200と、導体ベースプレート200上に配置され、入力端子24aおよび出力端子24bを有するMMIC基板24と、導体ベースプレート200上に配置され、MMIC基板24を囲むセラミック枠体180と、セラミック枠体180上に配置されたパッケージ入力端子21aおよびパッケージ出力端子21bと、MMIC基板24とセラミック枠体180との間の導体ベースプレート200上に配置された結合用基板25と、結合用基板25上に配置された結合ライン25aとを備え、パッケージ入力端子21aと結合ライン25a間、および結合ライン25aと入力端子24a間とが接続されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】バッファ層の結晶成長時に高抵抗化の不純物をドーピングすることなく上層の化合物半導体の結晶品質を保持するも、バッファ層を高抵抗化してオフリーク電流を確実に抑制し、信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2の裏面から、化合物半導体積層構造2の少なくともバッファ層2aに不純物、例えばFe,C,B,Ti,Crのうちから選ばれた少なくとも1種類を導入し、バッファ層2aの抵抗値を高くする。

(もっと読む)

半導体装置の製造方法及び半導体基板の洗浄方法

【課題】半導体基板の洗浄をより効率的に行うことができる半導体装置の製造方法及び半導体基板の洗浄方法等を提供する。

【解決手段】半導体基板20をその主面を鉛直方向及び水平方向から傾斜させて保持し、酸を含む洗浄液26に半導体基板20を浸漬する。

(もっと読む)

エピタキシャル基板のシート抵抗評価方法

【課題】下地基板の導電性を問わずに非破壊でHEMT構造のシート抵抗を評価する方法を提供する。

【解決手段】HEMT構造を備えるエピタキシャル基板のシート抵抗評価方法が、障壁層におけるIII族元素の組成比を除いて評価対象エピタキシャル基板と同一の構造を有する複数のエピタキシャル基板のそれぞれについてフォトルミネッセンス測定を行い、得られたスペクトルからバンド端ピーク強度値を取得する第1予備測定工程と、複数のエピタキシャル基板のそれぞれについてシート抵抗値を測定する第2予備測定工程と、取得したバンド端ピーク強度値とシート抵抗値とから検量線を作成する検量線作成工程と、評価対象エピタキシャル基板についてフォトルミネッセンス測定を行ってバンド端ピーク強度値を取得する実測工程と、得られたバンド端ピーク強度値と検量線とに基づいて評価対象エピタキシャル基板のシート抵抗値を算出する工程と、を備える。

(もっと読む)

トランジスタ装置

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース18、ドレイン20、およびゲート22を含む。第1のスペーサ層26が、活性領域の上方でソースとゲートの間にあり、第2のスペーサ層28が、活性領域の上方でドレインとゲートの間にある。第1のスペーサ層上の第1のフィールドプレート30、及び第2のスペーサ層上の第2のフィールドプレート32が、ゲートに接続される。第3のスペーサ層34が、第1のスペーサ層、第2のスペーサ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、第3のフィールドプレート36が、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】比較的簡易な構成で、化合物半導体素子の低抵抗伝送を達成すると共に、半導体素子の十分な高放熱性を低コストで実現する半導体装置を得る。

【解決手段】表面に接続電極11が形成された化合物半導体素子10と、表面に接続電極28a及び凹部21が形成された樹脂回路基板20と、凹部21内で化合物半導体素子10を固定する金属材料32,33とを有する半導体パッケージであり、化合物半導体素子10は、凹部21内において、接続電極11,28aが近接するように偏倚した位置に固定されており、接続電極11,28aがワイヤ接続されており、金属材料32は、化合物半導体素子10の底面から側面の少なくとも一部まで被覆する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

161 - 180 / 1,265

[ Back to top ]