Fターム[5F102GJ02]の内容

接合型電界効果トランジスタ (42,929) | 基板 (5,097) | 半導体材料(半絶縁性材料も含む) (3,925) | 4族 (2,421)

Fターム[5F102GJ02]の下位に属するFターム

Si (1,156)

Fターム[5F102GJ02]に分類される特許

141 - 160 / 1,265

トランジスタ

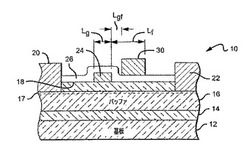

【課題】耐圧特性に優れた高電子移動度トランジスタ(HEMT)を提供する。

【解決手段】基板12上に形成された複数の活性半導体層16、18を含むHEMT10。ソース電極20、ドレイン電極22、およびゲート24は、複数の活性層16、18と電気的に接触して形成される。スペーサ層26は、複数の活性層16、18の表面の少なくとも一部の上に形成され、ゲート24を覆っている。フィールドプレート30が、スペーサ層26上に形成されて、ソース電極22に電気的に接続され、このフィールドプレート30はHEMT10内の最高動作電界を低減する。

(もっと読む)

半導体装置

【課題】電流コラプスを低減し、ドレイン電流を増大しながら、ゲートリーク電流を減少できるようにする。

【解決手段】半導体装置は、基板1と、基板1の上に形成されたIII族窒化物からなる半導体層2、3と、半導体層2、3の上に、それぞれ形成されたソース電極5、ゲート電極7及びドレイン電極6と、半導体層2、3の上に、ゲート電極7の下部及び半導体層2、3と接し、且つ、ソース電極5及びドレイン電極6と離間するように形成されたシリコンを含まない第1保護膜8と、半導体層2、3の上に、半導体層2、3と接し且つゲート電極7の下部と離間するように形成され、第1保護膜8と組成が異なり且つ窒素を含む第2保護膜9とを備えている。

(もっと読む)

半導体装置

【課題】電流コラプスが抑制され、耐圧の高い半導体装置を提供する。

【解決手段】基板110と、基板110の上方に形成された窒化物系化合物半導体からなるバッファ層120と、バッファ層120上に形成された窒化物系化合物半導体からなるチャネル層130と、チャネル層130の上方に形成された窒化物系化合物半導体からなる電子供給層132と、電子供給層132の上方に形成された第1の電極136と、電子供給層132の上方に形成された第2の電極138と、を備え、第2の電極138の電位に対して、基板110の電位および第1の電極136の電位が同じ側であり、第2の電極138の下の領域のバッファ層120の厚さおよびチャネル層130の厚さの合計が、第1の電極136の下の領域のバッファ層120の厚さおよびチャネル層130の厚さの合計より、大きい半導体装置。

(もっと読む)

III−V族トランジスタとIV族ダイオードを含む積層複合デバイス

【課題】III−V族トランジスタとIV族ダイオードからなる積層複合デバイスを提供する。

【解決手段】積層複合デバイスはIV族ダイオードと該IV族ダイオードの上に積層されたIII−V族トランジスタとを備える。IV族ダイオードのカソードがIII−V族トランジスタのソースと接触され、IV族ダイオードのアノードがIII−V族トランジスタのゲートに結合されて前記複合デバイスパッケージの底面上の複合アノードを与え、III−V族トランジスタのドレインが複合デバイスパッケージの底面に対向する上面上の複合カソードを与える。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成し、ドレイン電極と該ソース電極との間にフローティングガードリングを設けることによって、ノーマリ−オフで動作する半導体素子を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間で窒化物半導体層30にショットキー接合されたフローティングガードリング75と、ドレイン電極50とソース電極60との間及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、誘電層40上に形成され、一部が、誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置の製造方法

【課題】水素を用いた熱分解において、水素濃度を規定してエッチング速度を制御することで、半導体装置の製造方法の加工精度を向上させる。

【解決手段】半導体装置1の製造方法は、基板10に窒化物半導体で形成された第1層(障壁層25)および第2層(キャップ層26)を順に堆積させる堆積工程と、窒素および水素の混合雰囲気中で加熱して第2層をエッチングする熱エッチング工程とを備える。熱エッチング工程では、水素濃度が1%以上20%以下であることが望ましい。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置

【課題】窒化物半導体を用いた半導体装置のオン抵抗を低減できるようにする。

【解決手段】半導体装置は、アンドープのAlGaN層104と、該AlGaN層104の上に形成され、AlGaN層104とオーミック接触するソース電極107及びドレイン電極108とを有している。AlGaN層104の上部における少なくとも各電極107、108と接触する部分には、不純物拡散層110が形成されている。不純物拡散層110は、AlGaN層104に対しアクセプタ性を示す不純物が拡散し、且つ、AlGaN層104における窒素空孔と不純物とが結合してなる不純物準位が、AlGaN層104の伝導帯端の近傍に形成される。

(もっと読む)

半導体装置

【課題】基板の反りを抑制しつつ、バッファ層及び化合物半導体の厚さを稼ぐことができ、素子耐圧を向上することができる半導体装置を提供する。

【解決手段】半導体装置は、基板2と、バッファ層3と、窒化物系化合物半導体4とを備える。バッファ層3は、AlN層とGaN層とを積層した第1のバッファ領域321,331と、GaN層を有する第2のバッファ領域322,332とを交互に積層して構成される。バッファ層3において窒化物系化合物半導体4側の第1のバッファ領域331とそれに隣接する第2のバッファ領域332との1組の全体のAl組成は基板側の1組のAl組成に対して大きく設定されている。

(もっと読む)

半導体装置とその製造方法

【課題】 エッチングによるダメージを抑制しながら、ヘテロ接合面の近傍に負イオンを導入する技術を提供する。

【解決手段】 導入領域8上に保護膜30を形成する保護膜形成工程と、保護膜形成工程の後に、導入領域8を負イオンを含むプラズマに曝すプラズマ工程を備えている。保護膜30は、プラズマに対するエッチング速度が導入領域8よりも小さい。保護膜30には、負イオンを通過させることが可能な材料が用いられている。プラズマ中の負イオンは、保護膜30を通過し、導入領域8に導入される。

(もっと読む)

半導体デバイス

【課題】低シート抵抗化、リーク電流の低減、および、オーミック電極の接触抵抗の低減を実現する。

【解決手段】基板と、基板上に設けられ第1の窒化物系化合物半導体からなるチャネル層と、チャネル層上に設けられたバリア層と、バリア層上に設けられた第1電極と、チャネル層の上方に設けられた第2電極とを備え、バリア層は、チャネル層上に設けられ第1の窒化物系化合物半導体よりバンドギャップエネルギーが大きい第2の窒化物系化合物半導体からなる障壁層と、第2の窒化物系化合物半導体よりバンドギャップエネルギーが小さい第3の窒化物系化合物半導体からなり量子準位が形成された量子準位層とを有する半導体デバイスを提供する。

(もっと読む)

半導体デバイスおよび方法

【課題】光照射に適合した、少なくとも1つの電位障壁、又は表面障壁を持つ半導体デバイスの製造または処理に関し、高い絶縁破壊電圧と、大電流で低いキヤリア密度を有するデバイスの製造方法を提供する。

【解決手段】a)基板1を用意するステップと、b)第1エピタキシャル半導体層3を基板1の上に設けるステップと、c)1次元または2次元の繰り返しパターンを形成するステップと、を含み、パターンの各部分が、0.1〜50の範囲のアスペクト比を有するようにした方法を開示する。対応する半導体デバイス、電子回路および装置も開示している。

(もっと読む)

高電力マイクロ電子デバイスのための金属化構造

【課題】高電力で高性能なデバイスによって生成される熱応力に耐えることができる金属相互接続システムを提供する。

【解決手段】半導体デバイス構造であって、炭化ケイ素およびIII族窒化物からなる群から選択される広バンドギャップの半導体部分と、該半導体部分に対する相互接続構造であって、それぞれ2つの高導電性層と互い違いに、少なくとも2つの拡散バリア層を含む、相互接続構造とを備え、該拡散バリア層は、該高導電性層とは異なる熱膨張係数を有し、該高導電性層よりも低い熱膨張係数を有し、該それぞれの熱膨張係数の差異は、該高導電性層の膨張を抑えるために十分な大きさであるが、層間の接着強度を超える歪みを隣接層間に生じさせる差異よりも小さい、半導体デバイス構造。

(もっと読む)

歪み、反り、及びTTVが少ない75ミリメートル炭化珪素ウェハ

【課題】薄切りしたSiCウェハの歪み、反り、全厚さ変動(TTV)を低減する。

【解決手段】直径が少なくとも約75ミリメートル(3インチ)のSiCブールを、SiCの種結晶使用昇華成長により成長させ、該SiCブールを薄切りにして少なくとも1つのウェハを得る。その後、内層面損傷がウェハの各側において同一となるように、ラッピング下方力を、前記ウェハを折り曲げる下方力未満の量に制限しつつ、SiCウェハをラッピングし、SiCウェハを研磨する。これにより、高品質のSiC単結晶ウェハ16が得られる。該ウェハ16上には複数の窒化物エピタキシャル層18等が形成される。

(もっと読む)

低1cらせん転位の3インチ炭化珪素ウェハ

【課題】製造された結晶にある欠陥総数を低減するために、種結晶を用いた昇華システムにおいて形成された結晶の1cらせん転位欠陥レベルが低く、より大きく、高品質の炭化珪素バルク単結晶を製造する方法を提供する。

【解決手段】3C、4H、6H、2H、および15Rポリタイプからなる群から選択されるポリタイプであって、少なくとも75mm(3インチ)の直径と、約2000cm−2未満の1cらせん転位密度とを有する高品質のSiC単結晶ウェハ。

(もっと読む)

ワイドバンドギャップ半導体における常時オフ集積JFET電源スイッチおよび作成方法

【課題】常時オフVJFET集積電源スイッチを含むワイドバンドギャップ半導体デバイスの提供。

【解決手段】電源スイッチは、モノリシックまたはハイブリッドに実装され得、シングルまたはマルチチップのワイドバンドギャップ電源半導体モジュールにビルトインされた制御回路と一体化され得る。該デバイスは、高電力で温度に対する許容性があり、耐放熱性のエレクトロニクスコンポーネントにおいて用いられ得る。該デバイスを作成する方法もまた、記述される。

(もっと読む)

半導体装置およびその製造方法

【課題】電子移動度の低下が抑制され、かつ二次元電子ガスの閉じ込めが高められた半導体装置およびその製造方法を提供する。

【解決手段】AlaInbGa1-(a+b)N(0≦a,b≦1、0≦a+b≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが大きい第1の窒化物半導体層2、AlcIndGa1-(c+d)N(0≦c,d≦1、0≦c+d≦1)から成る第2の窒化物半導体層3、IneGa1-eN(0<e≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが小さいバックバリア層4、AlfIngGa1-(f+g)N(0≦f,g≦1、0≦f+g≦1)から成り、第2の窒化物半導体層3とバンドギャップが等しいチャネル層5、AlhIniGa1-(h+i)N(0≦h,i≦1、0≦h+i≦1)から成り、チャネル層5よりもバンドギャップが大きいバリア層6を、この順に基板1に積層する。

(もっと読む)

141 - 160 / 1,265

[ Back to top ]