Fターム[5F102GJ03]の内容

接合型電界効果トランジスタ (42,929) | 基板 (5,097) | 半導体材料(半絶縁性材料も含む) (3,925) | 4族 (2,421) | Si (1,156)

Fターム[5F102GJ03]に分類される特許

101 - 120 / 1,156

窒化物半導体装置およびその製造方法

【課題】オン抵抗の増加を抑制でき、さらにオフ時のゲートリーク電流およびドレインリーク電流を低減できるノーマリオフ型の窒化物半導体装置およびその製造方法を提供する。

【解決手段】上層の窒化物半導体層15を下層の窒化物半導体層14の格子定数より大きい材料とし、ゲート電極とソース電極およびドレイン電極との間の上層の窒化物半導体層表面15を、窒素ガスのプラズマ処理を施す。プラズマ処理を行うことにより、プラズマ処理なしの窒化物半導体層の積層構造により形成される2次元電子ガス層のキャリア濃度より、高いキャリア濃度の2次元電子ガス層16が形成され、特性の優れたノーマリオフ型の窒化物半導体装置となる。

(もっと読む)

窒化物系半導体層を含むエピタキシャルウエハ

【課題】ヘテロ接合電界効果型トランジスタに用いられ得る窒化物系半導体層を含むエピタキシャルウエハの反りと結晶性を改善する。

【解決手段】ヘテロ接合電界効果型トランジスタに用いられ得る窒化物系半導体層を含むエピタキシャルウエハは、Si基板上においてAlNまたはAlONの第1バッファ層、Al組成比を段階的に減少させたAlGaNの第2バッファ層、第2バッファ層の上に配置されていてAlaGa1−aN層/AlbGa1−bN層の繰返し多層からなる第3バッファ層、GaNチャネル層、および電子供給層をこの順に含み、第2バッファ層の最上部のAl組成比xが0≦x≦0.3の範囲内にある。

(もっと読む)

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、高いドレイン電流が実現できるようにする。

【解決手段】ドレイン電極107とゲート領域121との間のドレイン領域123の距離は、ソース電極106とゲート領域121との間のソース領域122の距離より長く形成され、加えて、ゲート電極104は、ゲート領域121からソース電極106の側に延在する延在部141を備えて形成されている。ゲート電極104のソース電極106の側への延在部141により、ゲート電極104に対する電圧印加でソース領域122のチャネル層101における電子濃度が増加可能とされている。

(もっと読む)

半導体装置の製造方法

【課題】高周波数動作が可能な半導体装置の製造方法を提供すること。

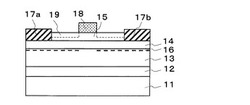

【解決手段】本発明は、成長炉内に配置した基板10上に、GaN電子走行層16を成長する工程と、成長炉に導入する混合ガス中の窒素原料ガスの分圧比を0.15以上0.35以下として、GaN電子走行層16上に、InAlN電子供給層18を成長する工程と、InAlN電子供給層18上に、ゲート電極26と、ゲート電極26を挟むソース電極28およびドレイン電極30と、を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

駆動回路および半導体集積回路

【課題】 高電子移動度トランジスタを用いて駆動回路を形成し、信頼性を低下させることなく、スイッチングトランジスタを高速に駆動する。

【解決手段】 駆動回路は、ドレインが第2ハイレベル電圧線に接続され、ソースが第1スイッチングトランジスタのゲートに接続される第1高電子移動度トランジスタと、ドレインが第1スイッチングトランジスタのゲートに接続される第2高電子移動度トランジスタと、ドレインが第2高電子移動度トランジスタのソースに接続され、ソースが接続ノードに接続される第1フィールドプレートと、第1および第2高電子移動度トランジスタを排他的にオンするために、第1および第2高電子移動度トランジスタのゲート電圧を生成し、第2高電子移動度トランジスタをオフするときに、第2高電子移動度トランジスタのゲートをロウレベル電圧線のロウレベル電圧に設定する制御部とを有している。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】窒化物半導体層上の層間絶縁膜の開口部が、電界の集中が緩和される形状に安定して精度良く形成された窒化物半導体装置及びその製造方法を提供する。

【解決手段】窒化物半導体層30と、窒化物半導体層30上に配置された第1の絶縁膜41と、第1の絶縁膜41上に配置された第2の絶縁膜42と、窒化物半導体層30上に互いに離間して配置された第1及び第2の主電極51,52と、第1及び第2の主電極51,52間で第2の絶縁膜42上に配置され、第1及び第2の絶縁膜に設けられた開口部を介して窒化物半導体層に接続するフィールドプレート60とを備える窒化物半導体装置であって、開口部において、窒化物半導体層30の表面と第1の絶縁膜41の側面とのなす第1の傾斜角が、窒化物半導体層30の表面と第2の絶縁膜42の側面を延長した線とのなす第2の傾斜角よりも小さく形成されている。

(もっと読む)

電界効果トランジスタ

【課題】動的な耐圧であるダイナミック耐圧の低下を抑制できるGaN系のHFETを提供する。

【解決手段】このGaN系のHFETでは、各ソース電極12の長手方向の長さL2が各ドレイン電極11の長手方向の長さL1よりも短く、ソース電極12の長手方向の両端12A,12Bがドレイン電極11の長手方向の両端11A,11Bよりも長手方向外方へ突出していない構成により、ソース電極12の端12A,12Bからドレイン電極11の端11A,11Bへ向かって電子流が集中することを回避できる。

(もっと読む)

ネスト化複合ダイオード

【課題】高いスイッチング速度を有し、電圧降伏耐性を強化したネスト化複合ダイオードを提供する。

【解決手段】ネスト化複合ダイオードの種々の実現を、本明細書に開示する。1つの実現では、ネスト化複合ダイオードが、複合ダイオードに結合されたプライマリ・トランジスタを含む。複合ダイオードは、中間型トランジスタとカスコード接続された低電圧(LV)ダイオードを含み、中間型トランジスタは、LVダイオードよりは大きく、プライマリ・トランジスタよりは小さい降伏電圧を有する。1つの実現では、プライマリ・トランジスタはIII-V族トランジスタとすることができ、LVダイオードはIV族LVダイオードとすることができる。

(もっと読む)

半導体装置

【課題】ヘテロ接合を有する半導体装置において、リーク電流と電流コラプスのトレードオフ関係を打破し、リーク電流と電流コラプスの双方を抑制すること。

【解決手段】半導体装置1の電子走行層4は、炭素が導入されている高抵抗領域4aを含んでいる。電子走行層4と電子供給層5のヘテロ接合5aと平行な断面において、高抵抗領域4aの炭素の濃度分布が、ドレイン電極12とソース電極18の少なくともいずれか一方の下方で相対的に濃く、ドレイン電極12と絶縁ゲート部16の間で相対的に薄くなるような断面が存在している。

(もっと読む)

GaN系半導体素子の製造方法

【課題】電極メタルがSiN絶縁膜に拡散することを抑制でき、電流コラプスの抑制とリーク電流の低減とを両立できるGaN系半導体素子の製造方法を提供する。

【解決手段】このGaN系HFETの製造方法によれば、GaN系積層体5上に形成したSiN保護膜7を熱処理により改質してから、Ti/Al電極15,16をGaN系積層体5上に形成し、Ti/Al電極15,16を熱処理してオーミック電極としてのソース電極15,ドレイン電極16とする。SiN保護膜7を熱処理した後に、Ti/Al電極15,16を熱処理(オーミックアニール)し、オーミック電極としてソース電極15,ドレイン電極16を形成することによって、電極メタルがSiN保護膜7に拡散することを抑制できる。

(もっと読む)

窒化物系半導体素子

【課題】本実施形態は、窒化物半導体層のクラックがほとんどなく、表面の粗度が極めて優秀であるので、全体的な安定性の向上された窒化物系半導体素子を提供する。

【解決手段】本実施形態の窒化物系半導体素子は、基板と、前記基板上に形成されるアルミニウムシリコンカーバイド(AlSixC1−x)前処理層と、前記前処理層上に形成されるAlがドーピングされたGaN層と、前記AlがドーピングされたGaN層上に形成されるAlGaN層とを含む。

(もっと読む)

III族窒化物エピタキシャル基板およびその製造方法

【課題】デバイス化の工程で割れが発生することを抑制することが可能なIII族窒化物エピタキシャル基板およびその製造方法を提供する。

【解決手段】本発明のIII族窒化物エピタキシャル基板10は、Si基板11と、該Si基板11と接する初期層14と、該初期層14上に形成され、Al組成比が0.5超え1以下のAlGaNからなる第1層15A1(15B1)およびAl組成比が0超え0.5以下のAlGaNからなる第2層15A2(15B2)を順次有する積層体を複数組有する超格子積層体15と、を有し、前記第2層のAl組成比が、前記基板から離れるほど漸減することを特徴とする。

(もっと読む)

半導体装置

【課題】高耐圧を確保でき、かつ大電流を流すことができるMOSトランジスタを備えた半導体装置を提供する。

【解決手段】P型拡散層15に起因してN型拡散層13に第1空乏層23が形成される。ゲート電極19にゲート電圧が印加されていない状態では、P型ポリシリコンからなるゲート電極19及びN型拡散層13の仕事関数差に起因してN型拡散層13に第2空乏層25が形成される。空乏層23,25によってソースコンタクト用拡散層9とドレインコンタクト用拡散層11が電気的に遮断される。ゲート電極19にゲート電圧が印加された状態では、第2空乏層25が消滅又は縮小することによってソースコンタクト用拡散層9とドレインコンタクト用拡散層11がN型拡散層13を介して電気的に導通する。

(もっと読む)

パワー素子およびその製造方法

【課題】本発明は、ノーマリーオフ動作が可能なパワー素子およびその製造方法を提供する。

【解決手段】本発明のパワー素子は、第1窒化物層を形成した後ゲート電極下部に第2窒化物層をさらに形成することによってゲート電極に対応する部分には2次元の電子ガス層が形成されないため、ノーマリーオフ動作が可能である。これによって、本発明の一実施形態に係るパワー素子は、ゲートの電圧に応じて2次元の電子ガス層の生成を調整することができ、ノーマリーオフ動作が可能であるため、消費電力を減少させ得る。また、ゲート電極に対応する第2窒化物層を形成するため、第1窒化物層を形成した後ゲート電極に対応する部分のみを再成長させたり、ゲート電極に対応する部分を除いた残り部分をエッチングする方法を用いることによって、リセス工程を省略することができることから素子の再現性を確保することが化膿であり、工程を単純化させることができる。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層104に形成された第1チャネル型の第1MISFET120の第1ソース124および第1ドレイン126が、第1半導体結晶層104を構成する原子と、ニッケル原子との化合物、または、コバルト原子との化合物、またはニッケル原子とコバルト原子との化合物からなり、第2半導体結晶層106に形成された第2チャネル型の第2MISFET130の第2ソース134および第2ドレイン136が、第2半導体結晶層106を構成する原子と、ニッケル原子との化合物、または、コバルト原子との化合物、または、ニッケル原子とコバルト原子との化合物からなる。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】精密なエッチング制御を必要とすることなく、ビアホール構造を形成することを可能とするとともに、エッチング後の洗浄を容易にする。

【解決手段】半導体装置において、第1の基板11と、第1の基板表面に形成された素子領域12,13と、素子領域と接続され、第1の基板11上に形成された電極14,15,16と、第1の基板11と積層される第2の基板17と、第2の基板17を貫通し、電極上に配置されるビアホール18a,18b,18cと、ビアホール内に形成される金属層19a,19b,19cと、を備える。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置においてオーミック特性を良好にし、かつ、酸・アルカリによる腐食に対し高い耐性を有することが可能な技術を提供することを目的とする。

【解決手段】半導体装置は、不純物が添加された高濃度不純物領域2を有する窒化物半導体層1と、高濃度不純物領域2上に順に積層された下地電極層3及び主電極層4を含む電極11とを備える。主電極層4は、窒化物半導体層1に対して下地電極層3よりも仕事関数が近い第1金属と、水素よりもイオン化傾向が小さい第2金属とからなる合金を主成分として含む。下地電極層3は、主電極層4よりも窒素との反応性が高い金属を主成分として含み、かつ、第1金属を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系トランジスタを簡便な構造で適切に保護することができる半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極110gと保護ダイオード用電極115pとが互いに接続されている。絶縁膜113は、所定値以上の電圧がゲート電極110gに印加された場合にリーク電流を保護ダイオード用電極115pと電子走行層104及び電子供給層103との間に流し、所定値は、HEMTがオン動作する電圧より高く、ゲート絶縁膜109gの耐圧よりも低い。

(もっと読む)

101 - 120 / 1,156

[ Back to top ]