Fターム[5F102GJ05]の内容

接合型電界効果トランジスタ (42,929) | 基板 (5,097) | 半導体材料(半絶縁性材料も含む) (3,925) | 3−5族 (1,455) | GaAs (578)

Fターム[5F102GJ05]に分類される特許

61 - 80 / 578

化合物半導体装置

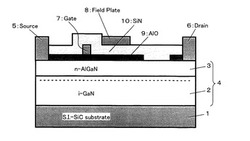

【課題】高耐圧特性と低オン抵抗特性とを両立した化合物半導体装置を実現する。

【解決手段】化合物半導体装置を、キャリア走行層2及びキャリア供給層3を含む窒化物半導体積層構造4と、窒化物半導体積層構造の上方に設けられたソース電極5及びドレイン電極6と、窒化物半導体積層構造の上方のソース電極とドレイン電極との間に設けられたゲート電極7と、ゲート電極とドレイン電極との間に少なくとも一部が設けられたフィールドプレート8と、窒化物半導体積層構造の上方に形成された複数の絶縁膜9、10とを備えるものとし、フィールドプレートとドレイン電極との間でゲート電極の近傍よりも複数の絶縁膜の界面の数を少なくする。

(もっと読む)

半導体装置、試験装置、および製造方法

【課題】閾値変動を抑えつつ、ゲートリーク電流を低減させた窒化物半導体HEMT。

【解決手段】窒化物系半導体で形成された半導体層と、半導体層上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、を備え、ゲート絶縁膜は、酸窒化膜で形成された第1絶縁膜と、タンタル、ハフニウム、ハフニウムアルミニウム、ランタン、およびイットリウムの少なくとも1つを含む第2絶縁膜と、を有する半導体装置を提供する。

(もっと読む)

電界効果トランジスタ、半導体スイッチ回路、および通信機器

【課題】半導体スイッチのチップサイズを大きくすることなく、高調波特性を改善する。

【解決手段】FET1において、化合物半導体基板上に形成され、所定の間隔を隔てて互いに平行状に設けられる複数のソース電極6を有するソース配線3と、化合物半導体基板上に形成され、所定の間隔を隔てて互いに平行状に設けられて複数のソース電極6に対して並列方向に交互に配置される複数のドレイン電極7を有するドレイン配線4と、化合物半導体基板上に形成され、少なくとも前記並列方向に互いに隣り合うソース電極6とドレイン電極7との電極間に位置する部分を有するゲート配線5と、ゲート配線5が形成される領域にてゲート配線5下に形成され、複数のソース電極6と複数のドレイン電極7との各電極間に独立して設けられる複数の埋め込みゲート層8とを備えた。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリ・オフ動作に適したMIS型を採用するも、電流コラプス特性を大幅に向上させて、デバイス効率及び耐圧に優れた信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成されたゲート絶縁膜6と、ゲート電極7とを含み、ゲート電極7は、ゲート絶縁膜6上に形成されたゲート基部7aと、ゲート基部7a上に形成されたゲート傘部7bとを有しており、ゲート傘部7bの下面が化合物半導体積層構造2とショットキー接触する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】材料の熱膨張係数の差に起因する反り等を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された電子走行層2と、電子走行層2上方に形成された電子供給層3と、が設けられている。基板1の表面に、電子走行層2よりも熱膨張係数が小さい第1の領域1bと、電子走行層2よりも熱膨張係数が大きい第2の領域1aと、が混在する。

(もっと読む)

トランジスタ用エピタキシャルウェハ

【課題】配管パージ等の作業を行うことなく、電気的特性等に影響を与える残留したTeやSeのエピタキシャル層中への混入を防止できるトランジスタ用エピタキシャルウェハを提供する。

【解決手段】基板100と化合物半導体層200とコンタクト層300とを有し、コンタクト層300は、n型不純物としてTe又はSeがドーピングされたIn組成比xが0.3≦x≦0.6で一定のn型InGaAs層からなり、n型InGaAs層は、n型不純物濃度が1.0×1019cm-3以上5.0×1019cm-3以下で、且つ、炭素濃度が1.0×1016cm-3以上3.0×1018cm-3以下であり、化合物半導体層200は、バッファ層400を備え、バッファ層400は、アンドープAlAs層からなる第1バッファ層401と、Al組成比yが0<y<1のアンドープAlGaAs層からなる第2バッファ層402とからなるものである。

(もっと読む)

エネルギー障壁を有するヘテロ接合トランジスタおよび関連する方法

【課題】チャネル内へのキャリアの閉じ込めを改善すること。

【解決手段】へテロ接合トランジスタは、III族窒化物を含むチャネル層14と、チャネル層の上のIII族窒化物を含む障壁層16と、チャネル層14が障壁層16とエネルギー障壁38との間にあるようにした、チャネル層14の上のインジウムを有するIII族窒化物の層を含むエネルギー障壁とを備えることができる。障壁層16は、チャネル層よりも大きなバンドギャップを有することができ、エネルギー障壁38のインジウム(In)の濃度はチャネル層14のインジウム(In)の濃度よりも高い可能性がある。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】HEMTの移動度の低下を抑制することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】高電子移動度トランジスタ構造層3を、気相成長法により成長温度600℃以上750℃以下、V/III比150以下の条件で成長し、バイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下、V/III比75以下の条件で成長し、さらにノンアロイ層18を、380℃以上450℃以下の成長温度で成長する。

(もっと読む)

半導体装置、及びその製造方法

【課題】低消費電力・低電圧動作で、高利得・低歪特性を有し、かつ低コスト化が実現可能な半導体装置とその製造方法を提供する。

【解決手段】本発明に係る半導体装置のpチャネルFET2は、ソース/ドレインを形成する高濃度p型半導体層33と、その直下層に配設された低濃度p型半導体層32と、高濃度p型半導体層33上に形成された第1電極層41と、低濃度p型半導体層32の下方に形成され、ゲートとなる高濃度n型半導体層22と、その上に形成された第2電極層42とを備える。nチャネルFET3は、ソース/ドレインを形成する高濃度n型半導体層22と、ゲートを形成する高濃度p型半導体層33と、その下方に形成された低濃度n型半導体層21と、第1電極層42と、第2電極層42とを備える。

(もっと読む)

トランジスタ装置

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能

するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース、ドレ

イン、およびゲートを含む。第1のスペーサ層が、活性領域の上方でソースとゲートの間

にあり、第2のスペーサ層が、活性領域の上方でドレインとゲートの間にある。第1のス

ペーサ層上の第1のフィールドプレート、及び第2のスペーサ層上の第2のフィールドプ

レートが、ゲートに接続される。第3のスペーサ層が、第1のスペーサ層、第2のスペー

サ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、

第3のフィールドプレートが、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

多重フィールドプレートトランジスタ

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能

するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース、ドレ

イン、およびゲートを含む。第1のスペーサ層が、活性領域の上方でソースとゲートの間

にあり、第2のスペーサ層が、活性領域の上方でドレインとゲートの間にある。第1のス

ペーサ層上の第1のフィールドプレート、及び第2のスペーサ層上の第2のフィールドプ

レートが、ゲートに接続される。第3のスペーサ層が、第1のスペーサ層、第2のスペー

サ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、

第3のフィールドプレートが、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

パッケージ

【課題】導体ベースプレートと金属外壁との熱膨張係数が異なることに伴う、銀ロウ付けする際の導体ベースプレートの反りを抑制したパッケージを提供する。

【解決手段】導体ベースプレートと、導体ベースプレート上に配置された半導体装置と、半導体装置を内在し、導体ベースプレート上に配置され、導体ベースプレートと接する面に複数の開放部を有する金属壁と、開放部を充填するブロックとを備えるパッケージ。

(もっと読む)

半導体デバイスの製造方法およびエピタキシャル成長用の支持基板

【課題】中間層の一部が露出している支持基板であっても、それに適切な処理を加えることにより、半導体デバイスを歩留まりよく製造することができる半導体デバイスの製造方法およびエピタキシャル成長用の支持基板を提供する。

【解決手段】本半導体デバイスの製造方法は、少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させることができる下地基板10と、下地基板10上に全面的に配置された中間層20と、中間層20上に部分的に配置されたGaN層30aとを含み、GaN層30aと中間層20の一部とが露出している支持基板2を形成する工程と、支持基板2の中間層20が露出している部分20p,20q,20rを選択的に除去することにより、下地基板10の一部を露出させる工程と、GaN層30a上に、III族窒化物半導体層をエピタキシャル成長させる工程と、を備える。

(もっと読む)

高電子移動度トランジスタ用エピタキシャルウェハの製造方法、及び高電子移動度トランジスタ用エピタキシャルウェハ

【課題】不純物のメモリー効果を低減できる高電子移動度トランジスタ用エピタキシャルウェハの製造方法、及び高電子移動度トランジスタ用エピタキシャルウェハを提供する。

【解決手段】本発明に係る高電子移動度トランジスタ用エピタキシャルウェハの製造方法は、AlxGa1−xAs(ただし、0≦x≦0.3)からなるバッファ層と、バッファ層の上方に設けられ、Se又はTeを含むコンタクト層20とを備えた高電子移動度トランジスタ用エピタキシャルウェハの製造方法であって、600℃以上750℃以下の成長温度、20以上200以下のV/III比の成長条件下で、バッファ層の酸素濃度を2.0E16cm−3以下に制御してバッファ層を単結晶基板上に形成するバッファ層形成工程と、350℃以上500℃以下の成長温度で、コンタクト層20の表面の表面粗さRaを0.5nm以上5.0nm以下の範囲に制御してコンタクト層20を形成するコンタクト層形成工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】電界集中を緩和させることにより、高耐圧、高信頼性を得ることが可能な半導体装置とその製造方法を提供する。

【解決手段】本発明の実施形態は、半導体基板と、半導体基板上に設けられるゲート電極と、ゲート電極を挟んで半導体基板上に設けられるソース電極及びドレイン電極と、ゲート電極の少なくともドレイン電極側のエッジの下部に設けられるリセスと、を備える。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】フェルミ準位ピン止めが低減された化合物半導体を用いたMOS型の化合物半導体装置がより容易に製造できるようにする。

【解決手段】化合物半導体からなる第1半導体層101を形成し、次に、第1半導体層101より小さいバンドギャップエネルギーの化合物半導体からなる臨界膜厚以下の第2半導体層102を、第1半導体層101の上に接して形成し、次に、第2半導体層102の上にアモルファス状態の金属酸化物からなる絶縁層103を形成する。

(もっと読む)

トランジスタ素子及びトランジスタ用エピタキシャルウェハの製造方法

【課題】GaAs基板からHBT構造層に伝搬する転位を抑制したトランジスタ素子及びトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】GaAs基板2上に高電子移動度トランジスタ構造層3が形成され、高電子移動度トランジスタ構造層3上にヘテロバイポーラトランジスタ構造層4が形成されたトランジスタ素子において、GaAs基板2の転位密度が10,000/cm2以上100,000/cm2以下であり、高電子移動度トランジスタ構造層3とヘテロバイポーラトランジスタ構造層4との間に、InGaPからなるエッチングストッパ層12と、エッチングストッパ層12上に設けられたGaAsからなる安定化層21と、を設けたものである。

(もっと読む)

半導体装置、試験装置、および製造方法

【課題】電流電圧のパルス特性を向上させて電流電圧のDC特性に近づける。

【解決手段】半導体層と、半導体層上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、ゲート絶縁膜上に設けられ、ゲート絶縁膜上におけるゲート電極の端部の少なくとも一部においてゲート電極と接するゲート境界膜と、を備え、ゲート境界膜およびゲート絶縁膜は、同種の絶縁材料を含む半導体装置を提供する。ゲート電極およびゲート境界膜上に設けられた絶縁性の保護膜を更に備え、保護膜は、ゲート境界膜およびゲート絶縁膜とは別種の絶縁材料を含んでよい。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリオフ動作を容易に実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1上方に形成されたAlGaN層3と、AlGaN層3上に形成されたAlGaN層4と、AlGaN層4上に形成された電子走行層5と、電子走行層5上方に形成された電子供給層6と、が設けられている。AlGaN層3の組成をAlx1Ga1-x1N、AlGaN層4の組成をAlx2Ga1-x2Nと表すと、「0≦x1<x2≦1」の関係が成り立つ。AlGaN層4の上面には、AlGaN層4の下面に存在する正の電荷よりも多くの負の電荷が存在している。

(もっと読む)

61 - 80 / 578

[ Back to top ]