Fターム[5F102GJ05]の内容

接合型電界効果トランジスタ (42,929) | 基板 (5,097) | 半導体材料(半絶縁性材料も含む) (3,925) | 3−5族 (1,455) | GaAs (578)

Fターム[5F102GJ05]に分類される特許

41 - 60 / 578

III−窒化物デバイスの製造方法およびIII−窒化物デバイス

【課題】高耐圧なIII−窒化物デバイスを提供する。

【解決手段】半導体基板1、基板1上の活性層のスタックであって、それぞれの層はIII−窒化物材料を含むスタック2−5、スタック2−5上のゲート8、ソース9およびドレインコンタクト10、および基板1の裏側(活性層のスタックに接する側に対向する側)から基板1に接する活性層のスタックの下層まで基板中を延びるトレンチであって、トレンチはドレイン領域を完全に囲み、ドレインに向かうゲート領域の端と、ゲートに向かうドレイン領域の端との間に配置され、基板のドレイン領域は本質的に半導体材料から形成されるような幅を有するトレンチを含むIII−窒化物デバイス。

(もっと読む)

トランジスタ素子

【課題】n型不純物としてTeを用いたノンアロイ層を有していても、ベース電流、コレクタ電流のリーク電流が少ないトランジスタ素子を提供する。

【解決手段】基板11と、基板11上に設けられた高電子移動度トランジスタ構造層28と、高電子移動度トランジスタ構造層28上に設けられたヘテロバイポーラトランジスタ構造層29とを備えたトランジスタ素子10において、ヘテロバイポーラトランジスタ構造層29のノンアロイ層26,27は、n型不純物としてTeがドーピングされており、n型不純物濃度が1.0×1019cm-3以上2.0×1019cm-3以下にされているものである。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】絶縁破壊耐性に優れた化合物半導体積層構造を備えて基板の絶縁破壊の十分な抑止を実現し、ピンチオフ状態とする際にもリーク電流が極めて少ない信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上に形成された化合物半導体積層構造2は、その厚みが10μm以下であって、AlNからなる厚い第1のバッファ層を有しており、III族元素(Ga,Al)の総原子数のうち、Al原子の比率が50%以上とされ、換言すれば、V族元素のNとの化学結合(Ga−N,Al−N)の総数のうち、Al−Nが50%以上とされる。

(もっと読む)

半導体素子の構造、半導体抵抗素子の製造方法およびFETスイッチ回路

【課題】薄膜抵抗又は基板抵抗によって数kΩから数十kΩの抵抗値を持つゲート抵抗のサイズが基板長さ、基板幅に比べて大きい。

【解決手段】能動層10を有する半導体基板11と、半導体基板の能動層10にオーミック接触するソース電極13及びドレイン電極14と、能動層10の上方に設けられたゲート電極15と、半導体基板11に設けられた非活性領域16と、非活性領域16上にゲート電極15の一部が引出されて接触する導体17と、非活性領域16上で直流電圧が印加されるパッド電極18と、パッド電極18及び導体17にオーミック接触し、非活性領域16に設けられたゲート抵抗領域19とを備え、ゲート抵抗領域19は半導体基板11へボロンイオンを注入することによって形成され、ボロンイオンの注入量によりゲート抵抗領域19上のシート抵抗値を高めたことを備えたことを特徴とする半導体素子の構造が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】放熱性と耐久性に優れた半導体装置およびその製造方法を提供する。

【解決手段】導電ベースプレートと、導電ベースプレート上に接合される半導体チップと、半導体チップと導電ベースプレートとの接合面の中央部に配置された第1接着剤と、半導体チップと導電ベースプレートとの接合面の周辺部に配置された第2接着剤とを備え、第1接着剤は第2接着剤よりも相対的に熱伝導率が高く、第2接着剤は第1接着剤より相対的に接合力が高い半導体装置。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

III−V族化合物半導体エピタキシャルウエハ

【課題】充分な選択比を備え、また、除去が比較的容易なエッチングストッパ層を得る。

【解決手段】GaAs基板10上に設けられた高電子移動度トランジスタ構造20と、高電子移動度トランジスタ構造20の上に設けられたヘテロ接合バイポーラトランジスタ構造40と、を備え、高電子移動度トランジスタ構造20とヘテロ接合バイポーラトランジスタ構造40との間には、As濃度が1.0×1016atoms/cc以上1.0×1021atoms/cc以下のInGaAsP層からなるエッチングストッパ層30を備える。

(もっと読む)

半導体装置

【課題】電流コラプスが抑制され、耐圧の高い半導体装置を提供する。

【解決手段】基板110と、基板110の上方に形成された窒化物系化合物半導体からなるバッファ層120と、バッファ層120上に形成された窒化物系化合物半導体からなるチャネル層130と、チャネル層130の上方に形成された窒化物系化合物半導体からなる電子供給層132と、電子供給層132の上方に形成された第1の電極136と、電子供給層132の上方に形成された第2の電極138と、を備え、第2の電極138の電位に対して、基板110の電位および第1の電極136の電位が同じ側であり、第2の電極138の下の領域のバッファ層120の厚さおよびチャネル層130の厚さの合計が、第1の電極136の下の領域のバッファ層120の厚さおよびチャネル層130の厚さの合計より、大きい半導体装置。

(もっと読む)

半導体装置及び電力増幅器

【課題】トランジスタの占有面積をほとんど増やすことなく、かつ、HBTとHFETとを接続する配線による悪影響を受けないBi−HFET(半導体装置)を提供する。

【解決手段】基板101上に形成されたHFET160と、HFET160上に形成されたHBT170とを備え、HFET160は、チャネル層102と、コンタクト層104とを有し、HBT170は、HFET160のコンタクト層104と接続、又は、一体化されたサブコレクタ層107と、コレクタ層108と、ベース層109と、エミッタ層110と、エミッタキャップ層111と、エミッタコンタクト層112とを有し、コレクタ層108、ベース層109及びエミッタ層110は、メサ形状の構造体であるベースメサ領域830を構成し、ゲート電極202は、第一のコレクタ電極203とベースメサ領域830との平面的な間に設けられたリセス領域820内に形成されている。

(もっと読む)

パッケージ

【課題】電流容量が高く、かつ生じる応力が低減されてクラックの発生が抑制され、信頼性の高いパッケージを提供する。

【解決手段】パッケージ外壁16と、パッケージ外壁16を貫通する貫通孔と、貫通孔にはめ込まれた凸状フィードスルー25と、凸状フィードスルー25に固定され端子電極21bとを備え、端子電極21bは、相対的に線熱膨張率は低いが抵抗率が高い第1の金属層90と、相対的に線熱膨張率は高いが抵抗率が低い第2の金属層80a,80bとを備える。

(もっと読む)

半導体装置

【課題】マルチフィンガーFETセル内のループ発振を抑制させ、かつチップ面積の増大を抑制する。

【解決手段】ユニットフィンガーの並列接続からなるマルチフィンガー単位FETセルと、マルチフィンガー単位FETセルのゲートフィンガーを並列接続する指定ゲートバスラインと、指定ゲートバスラインに接続されたゲート引き出しラインとを備え、ゲート引き出しラインと指定ゲートバスラインの接続点をマルチフィンガー単位FETセル内の中心からずらすことによって、接続点の一方に接続されたゲートフィンガー数が、他方に接続されたゲートフィンガー数よりも多くする。

(もっと読む)

MMIC用パッケージ

【課題】チップサイズの大きい高周波部品(MMIC)とパッケージ端子間を接続するインダクタンス成分を抑制し、高周波特性を改善したMMIC用パッケージを提供する。

【解決手段】導体ベースプレート200と、導体ベースプレート200上に配置され、入力端子24aおよび出力端子24bを有するMMIC基板24と、導体ベースプレート200上に配置され、MMIC基板24を囲むセラミック枠体180と、セラミック枠体180上に配置されたパッケージ入力端子21aおよびパッケージ出力端子21bと、MMIC基板24とセラミック枠体180との間の導体ベースプレート200上に配置された結合用基板25と、結合用基板25上に配置された結合ライン25aとを備え、パッケージ入力端子21aと結合ライン25a間、および結合ライン25aと入力端子24a間とが接続されている。

(もっと読む)

パッケージ

【課題】ベース面の反りの少ないパッケージを提供する。

【解決手段】導体ベースプレート200と、導体ベースプレート上に配置された半導体装置と、半導体装置を内在し、導体ベースプレート上に配置され、導体ベースプレートとは異なる材料からなる金属壁16とを備え、導体ベースプレートは、対抗する1対の端面100a・100bが緩やかな弧を有し、金属壁も緩やかな弧を有しているので、接合時や基板実装時、キャップ半田付け時の反りの発生を抑制できる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】バッファ層の結晶成長時に高抵抗化の不純物をドーピングすることなく上層の化合物半導体の結晶品質を保持するも、バッファ層を高抵抗化してオフリーク電流を確実に抑制し、信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2の裏面から、化合物半導体積層構造2の少なくともバッファ層2aに不純物、例えばFe,C,B,Ti,Crのうちから選ばれた少なくとも1種類を導入し、バッファ層2aの抵抗値を高くする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

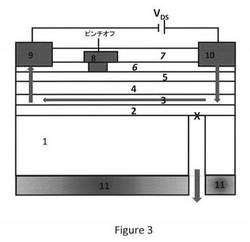

トランジスタ装置

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース18、ドレイン20、およびゲート22を含む。第1のスペーサ層26が、活性領域の上方でソースとゲートの間にあり、第2のスペーサ層28が、活性領域の上方でドレインとゲートの間にある。第1のスペーサ層上の第1のフィールドプレート30、及び第2のスペーサ層上の第2のフィールドプレート32が、ゲートに接続される。第3のスペーサ層34が、第1のスペーサ層、第2のスペーサ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、第3のフィールドプレート36が、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】比較的簡易な構成で、化合物半導体素子の低抵抗伝送を達成すると共に、半導体素子の十分な高放熱性を低コストで実現する半導体装置を得る。

【解決手段】表面に接続電極11が形成された化合物半導体素子10と、表面に接続電極28a及び凹部21が形成された樹脂回路基板20と、凹部21内で化合物半導体素子10を固定する金属材料32,33とを有する半導体パッケージであり、化合物半導体素子10は、凹部21内において、接続電極11,28aが近接するように偏倚した位置に固定されており、接続電極11,28aがワイヤ接続されており、金属材料32は、化合物半導体素子10の底面から側面の少なくとも一部まで被覆する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

エピタキシャル基板のシート抵抗評価方法

【課題】下地基板の導電性を問わずに非破壊でHEMT構造のシート抵抗を評価する方法を提供する。

【解決手段】HEMT構造を備えるエピタキシャル基板のシート抵抗評価方法が、障壁層におけるIII族元素の組成比を除いて評価対象エピタキシャル基板と同一の構造を有する複数のエピタキシャル基板のそれぞれについてフォトルミネッセンス測定を行い、得られたスペクトルからバンド端ピーク強度値を取得する第1予備測定工程と、複数のエピタキシャル基板のそれぞれについてシート抵抗値を測定する第2予備測定工程と、取得したバンド端ピーク強度値とシート抵抗値とから検量線を作成する検量線作成工程と、評価対象エピタキシャル基板についてフォトルミネッセンス測定を行ってバンド端ピーク強度値を取得する実測工程と、得られたバンド端ピーク強度値と検量線とに基づいて評価対象エピタキシャル基板のシート抵抗値を算出する工程と、を備える。

(もっと読む)

化合物半導体装置の製造方法及び洗浄剤

【課題】リセス等の形成に伴う処理で生じる残渣を適切に除去することができる化合物半導体装置の製造方法及び洗浄剤を提供する。

【解決手段】化合物半導体積層構造1を形成し、化合物半導体積層構造1の一部を除去して凹部4を形成し、洗浄剤を用いて凹部4内の洗浄を行う。洗浄剤は、凹部4内に存在する残渣と相溶する基材樹脂と溶媒とを含む。

(もっと読む)

41 - 60 / 578

[ Back to top ]