Fターム[5F102GJ05]の内容

接合型電界効果トランジスタ (42,929) | 基板 (5,097) | 半導体材料(半絶縁性材料も含む) (3,925) | 3−5族 (1,455) | GaAs (578)

Fターム[5F102GJ05]に分類される特許

561 - 578 / 578

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

本発明は、印刷可能半導体素子を製造するとともに、印刷可能半導体素子を基板表面上に組み立てるための方法及びデバイスを提供する。本発明の方法、デバイス、デバイス部品は、幅広いフレキシブル電子デバイス及び光電子デバイス並びにデバイスの配列を高分子材料を備える基板上に形成することができる。また、本発明は、伸張形態で良好な性能が得られる伸縮可能な半導体構造及び伸縮可能な電子デバイスも提供する。 (もっと読む)

再成長オーミックコンタクト領域を有する窒化物ベースのトランジスタの製作方法及び再成長オーミックコンタクト領域を有する窒化物ベースのトランジスタ

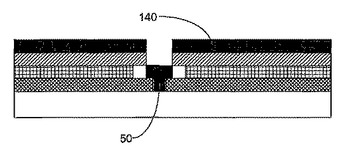

トランジスタ製作は、基板上に窒化物ベースのチャネル層を形成すること、窒化物ベースのチャネル層上に障壁層を形成すること、窒化物ベースのチャネル層のコンタクト領域を露出させるように障壁層にコンタクト凹部を形成すること、例えば、低温堆積プロセスを使用して、窒化物ベースのチャネル層の露出されたコンタクト領域上にコンタクト層を形成すること、コンタクト層上にオーミックコンタクトを形成すること、及びオーミックコンタクトに隣接した障壁層上に配置されたゲートコンタクトを形成すること、を含んでいる。また、高電子移動度トランジスタ(HEMT)及びHEMTの製作方法が提供される。HEMTは、基板上の窒化物ベースのチャネル層と、窒化物ベースのチャネル層上の障壁層と、チャネル層の中まで延びる、障壁層のコンタクト凹部と、コンタクト凹部の中の窒化物ベースのチャネル層上の窒化物ベースのn型半導体材料のコンタクト領域と、窒化物ベースのコンタクト領域上のオーミックコンタクトと、このオーミックコンタクトに隣接した障壁層上に配置されたゲートコンタクトと、を含んでいる。窒化物ベースのn型半導体材料のコンタクト領域及び窒化物ベースのチャネル層は、表面積拡大構造を含んでいる。  (もっと読む)

(もっと読む)

電界効果トランジスタ

第1の領域に配置されるエンハンスメントモードトランジスタデバイスと、横方向にずれた第2の領域に配置されるデプレッションモードトランジスタデバイスとを備える半導体構造である。チャネル層の上に、エンハンスメントモードトランジスタデバイスInGaPエッチストップ/ショットキーコンタクト層が配置され、InGaP層の上に、InGaPとは異なる第1の層が配置され、第1の層の上に、デプレッションモードトランジスタデバイスエッチストップ層が配置され、デプレッションモードトランジスタデバイスエッチストップ層の上に第2の層が配置される。デプレッションモードトランジスタデバイスは、第2の層及びデプレッションモードトランジスタデバイスエッチストップ層を貫通し第1の層で終止するゲートリセスを有する。エンハンスメントモードトランジスタデバイスは、第2の層、デプレッションモードトランジスタデバイスエッチストップ層、第1の層を貫通しInGaP層で終止するゲートリセスを有する。  (もっと読む)

(もっと読む)

スピントロニクス応用のための磁気電気電界効果トランジスタ

本発明の対象は、チャネル領域と、チャネル領域の一方の側に接続され、チャネル領域に電子を注入するように適合されたソースと、チャネル領域の反対側に接続され、スピン偏極した電子を検出するように適合されたドレインと、4つの磁気要素を備える磁気二重対要素を少なくとも1つ備えるゲートとを備える磁気電気電界効果トランジスタであって、各磁気要素がチャネル領域に磁界を誘導するように適合され、各磁気二重対要素の誘導された磁界の合計がほぼゼロになるように制御することが可能であり、ゲートがチャネル領域に電界を誘導するようにさらに適合された磁気電気電界効果トランジスタである。 (もっと読む)

電荷移動誘起エネルギー障壁を有する窒化物へテロ接合トランジスタおよびその製造方法

窒化物ベースの電界効果トランジスタは、 基板と、基板の上に形成されたInAlGaNを備えるチャネル層と、チャネル層と電気的に連絡しているソースおよびドレインオーミックコンタクトと、チャネル層の上に形成されたゲートコンタクトとを備える。少なくとも1つのエネルギー障壁が、チャネル層から離れるキャリアの動きに逆らう。エネルギー障壁は、チャネルから離れる方向に向けられた関連した電界を生成する正孔供給源層に近接した電子供給源層を備えることができる。いくつかの実施形態に従ったエネルギー障壁は、約0.5eVを超える拡散電位障壁を実現することができる。方法の実施形態もまた開示されている。  (もっと読む)

(もっと読む)

デバイス製造方法および基板

電磁放射線を用いた一回の露光プロセスでT−ゲートを製造する方法が開示される。  (もっと読む)

(もっと読む)

保護層および低損傷陥凹部を備える窒化物ベースのトランジスタならびにその製作方法

窒化物ベースの半導体チャネル層上に窒化物ベースの半導体バリア層を形成すること、および窒化物ベースの半導体バリア層のゲート領域上に保護層を形成することによって、トランジスタが製作される。パターニングされたオーム性接触金属領域が、バリア層上に形成され、第1および第2のオーム性接触を形成するためにアニールされる。アニールは、保護層をゲート領域上に載せたままで実施される。バリア層のゲート領域上に、ゲート接点も形成される。ゲート領域内に保護層を有するトランジスタも形成され、バリア層の成長させたままのシート抵抗と実質的に同じシート抵抗をもつバリア層を有するトランジスタも同様である。  (もっと読む)

(もっと読む)

モノリシック集積型エンハンスメントモードおよびデプリーションモードFETおよびその製造方法

【課題】 製造コストを低減し品質の均一性および安定性を高めたモノリシック集積型エンハンスメントモード/デプリーションモードFETデバイスを提供する。

【解決手段】 単一の半導体多層構造でデプリーションモード(Dモード)FETをエンハンスメントモード(Eモード)FETとモノリシックに集積回路化する。上記多層構造にはチャネル層を設け、その上に障壁層をオーバーレイし、さらにその上にオームコンタクト層をオーバーレイする。これらDモードFETおよびEモードFETのソースコンタクトおよびドレーンコンタクトをオームコンタクト層に接続する。またDモードFETおよびEモードFETのゲートコンタクトを障壁層に接続する。障壁層の中のEモードゲートコンタクトの下に非晶質化領域を設ける。この非晶質化領域が障壁層との間の埋込みEモードSchottkyコンタクトを構成する。代わりに実施例ではDモードFETのゲートコンタクトを障壁層にオーバーレイした第1の層に接続し、その第1の層の中にDモード非晶質化領域を形成する。

(もっと読む)

ひずみ印加半導体デバイス

多数キャリアが正孔であるトランジスタにおいて、少なくとも1つの狭いバンドギャップの領域または層が、p型にドーピングされるかまたは過剰の正孔を含み、かつ機械的圧縮ひずみを受け、これによって、正孔の移動度がかなり増大し得る。pチャネル量子井戸FETでは、量子井戸のInSb井戸のp型層5(変調ドーピングまたは直接ドーピングされている)が、In1−xAlxSb層4と、In1−xAlxSb層6との間にあるが、ここで、xは、軽い正孔および重い正孔が、kTをはるかに超える量だけ分離されるような範囲にまで、層5中にひずみを導入するに十分な値である。pnpバイポーラデバイスを含む、本発明の範囲内にあるトランジスタは、相補型論理回路における電子が多数キャリアである従来の等価物と一緒に用いられ得る。  (もっと読む)

(もっと読む)

増大した線形性および製造可能性を有するFETを含むBiFET

例示的一実施例によれば、基板上に位置するBiFETは、基板の上に位置するエミッタ層部分を含み、エミッタ層部分は第1のタイプの半導体を含む。HBTはエッチストップ層の第1の部分をさらに含み、エッチストップ層の第1の部分はInGaPを含む。BiFETは基板の上に位置するFETをさらに含み、FETはソース領域およびドレイン領域を含み、エッチストップ層の第2の部分はソース領域およびドレイン領域の下に位置し、エッチストップ層の第2の部分はInGaPを含む。FETはエッチストップ層の第2の部分の下に位置する第2のタイプの半導体層をさらに含む。エッチストップ層はFETの線形性を増大させ、HBTの電子の流れを低下させない。  (もっと読む)

(もっと読む)

半導体部品および半導体部品の製造方法

半導体部品は、半導体基板(110)と、半導体基板の上方のエピタキシャル半導体層(120)と、エピタキシャル半導体層内のバイポーラトランジスタ(770、870)と、エピタキシャル半導体層内の電界効果トランジスタ(780、880)とを含む。エピタキシャル半導体層の一部によって、バイポーラトランジスタのベースと電界効果トランジスタのゲートとが形成され、エピタキシャル半導体層のその一部は実質的に均一なドーピング濃度を有する。同じまたは他の実施形態においては、エピタキシャル半導体層の異なる部分によって、バイポーラトランジスタのエミッタと電界効果トランジスタのチャネルとが形成され、エピタキシャル半導体層のその異なる部分はエピタキシャル半導体層の一部の実質的に均一なドーピング濃度と同じかまたは異なる実質的に均一なドーピング濃度を有する。  (もっと読む)

(もっと読む)

方法と装置

ソース領域(9)、ドレイン領域およびソースとドレイン領域を互いに接続するチャネル層(11)を含む電界効果トランジスタを製造する方法。該方法は半導体材料(1)の一部にソース領域(9)などの半導体材料(1)中の移植物の縁部を確定するためにその縁部が使用される犠牲層(4)を提供する手順を含み、犠牲層(4)の縁部(4c)はその後ゲート(16)の縁部を画定するために使用される。

(もっと読む)

(もっと読む)

スプリットチャネル高電子移動度トランジスタデバイス

トランジスタ構造体であって、ガリウムヒ素(GaAs)半導体基板と、インジウムアルミニウムガリウムヒ素(InAlGaAs)格子整合層と、格子整合層の上に配設されるインジウムアルミニウムヒ素(InAlAs)バリア層と、バリア層上に配設されるInyGa1−yAs下部チャネル層であって、yは下部チャネル層のIn含有量のモル分率である、InyGa1−yAs下部チャネル層と、下部チャネル層上に配設されるInxGa1−xAs上部チャネル層であって、xは上部チャネル層のIn含有量のモル分率であり、xはyと異なる、InxGa1−xAs上部チャネル層と、InxGa1−xAs上部チャネル層上のInAlAsショットキー層とを有するトランジスタ構造体。下部チャネル層は、上部チャネル層のバンドギャップより大きいバンドギャップを有し、下部チャネル層は、上部チャネル層のバルク電子移動度より低いバルク電子移動度を有する。 (もっと読む)

半導体装置及びその製造方法

【課題】ゲート長の短いゲート電極を有し、しかも低抵抗で高周波特性が優れている半導体装置およびその製造方法を提供する。

【解決手段】少なくともノンドープInGaP層又はノンドープInAlGaP層からなる上層半導体層12と、この上層半導体層直下にGaAs層またはAlGaAs層からなる下層半導体層11を含む半導体基板に、上層半導体層表面から上層半導体層への浸入が、下層半導体層で略停止するショットキーゲート電極15と、このショットキーゲート電極部に接続して第1の電極の抵抗を低減する第2の電極部16からなるT字型ゲート電極を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 能動層に設ける窪みの側壁部分とゲート電極との間に隙間のない埋め込みゲート電極構造を有する半導体装置およびその製造方法を提供すること。

【解決手段】 窪み20をもつ能動層12が形成された半導体基板11と、この半導体基板11の能動層12の上方に設けられたソース電極14およびドレイン電極15と、能動層12の窪み20の部分に埋め込まれたゲート電極21と、ソース電極14およびドレイン電極15間の能動層12上に堆積された絶縁膜17とを具備した半導体装置において、窪み20の幅W1は、絶縁膜17に設けられた開口17aの幅W2よりも小さく形成され、ゲート電極21を構成する金属膜が能動層12に設けた窪み20の部分および絶縁膜17の開口17aの部分に埋め込まれている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】 電界緩和を図り高耐圧化を実現することに加え、デバイスサイズの更なる減少化、正孔の引き抜きを容易にして、信頼性の高い優れた化合物半導体装置を実現する。

【解決手段】 本発明の化合物半導体装置は、GaAs等の第1の化合物半導体層上に、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にない、即ちタイプII構造のバンド構造を有する属元素と6属元素の化合物からなるアモルファス層、例えばアモルファスGaS層(a−GaS層)を有するものである。

(もっと読む)

マイクロストリップ線路、その製造方法、インダクタ素子及び高周波半導体装置

【課題】 マイクロストリップ線路の線路幅の狭小化を行なったとしても、導体損失が増加しないようにする。

【解決手段】 半絶縁性GaAsからなる基板11上には、接地電極12と、厚さが約0.5μmのチタン酸ストロンチウムからなる誘電体層13と、線状導体層14とにより構成されるマイクロストリップ線路が形成されている。線状導体層14は、幅が約0.5μmの狭小部14aと、幅が約5μmの幅広部14bとにより構成されている。この線状導体層14は、異なる材料からなる積層体であって、基板11側から順次形成された、厚さが約0.1μmの窒化タングステンシリコンからなる第1層15と、厚さが約0.05μmのTiと厚さが約0.5μmのAuとの積層体からなる第2層16と、厚さが約3μmのAuからなる第3層17とから構成されている。

(もっと読む)

伝送線路、その電気的特性の調整方法、およびマイクロ波モノリシックIC

【課題】 コンパクトかつ電気的特性の良好な高性能・高歩留まりの高周波伝送線路およびその電気的特性の調整方法の提供を目的とする。

【解決手段】 コプラナ・ウェーブガイドのグラウンドパターン5の一部の上部に薄膜誘電体層6を選択的にパターニングして配置し、この薄膜誘電体層6の上に島状メタルパターン7を一定間隔で複数個配置する。島状メタルパターン7相互間、信号線4と島状メタルパターン7間、および島状メタルパターン7とグラウンドパターン5間の必要部分について、ボンディングワイヤ8で接続する。

(もっと読む)

561 - 578 / 578

[ Back to top ]