Fターム[5F102GM10]の内容

接合型電界効果トランジスタ (42,929) | ゲート下介在層(ゲートメタル電極底面とチャネル層表面間に介在する層) (3,125) | 組成(バンドギャップ)が不均一 (128)

Fターム[5F102GM10]に分類される特許

21 - 40 / 128

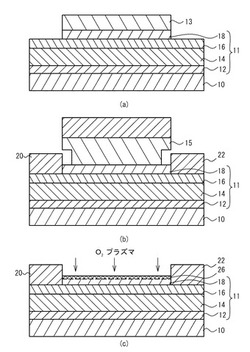

半導体装置の製造方法

【課題】信頼性を向上させることが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、窒化物半導体層11の表面に、パワー密度が0.2〜0.3W/cm2である酸素プラズマ処理を行う工程を有する半導体装置の製造方法である。本発明によれば、酸素プラズマ処理によって、窒化物半導体層11に導電層26が形成されることにより、イオンマイグレーション現象が抑制される。このため、半導体装置の信頼性が向上する。

(もっと読む)

電界効果トランジスタ

【課題】クラックを低減した窒化物半導体電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、基板101の上に形成された半導体層積層体と、半導体層積層体の上に形成されたソース電極107及びドレイン電極108と、ソース電極とドレイン電極との間に形成されたゲート電極109とを備えている。半導体層積層体は、第1の凹部102aを有する第1の窒化物半導体層102と、第1の凹部の底面上に形成された第2の窒化物半導体層105と、第1の凹部を除く領域の上及び第1の凹部の側面上に形成された第3の窒化物半導体層106とを有している。バンドギャップエネルギーの平均値が、第2の窒化物半導体層は第1の窒化物半導体層よりも大きく、第3の窒化物半導体層は第1の窒化物半導体層よりも大きく且つ第2の窒化物半導体層よりも小さい。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、窒化物系半導体装置を提供することを目的とする。

【解決手段】ドレイン電極26とゲート電極28との間に設けられたSBD金属電極30がAlGaN層20とショットキー接合されている。また、SBD金属電極30とソース電極24とが接続されており、電気的に短絡している。これにより、ゲート電極28にオフ信号が入ると、MOSFET部32がオフ状態となり、MOSFET部32のドレイン側の電圧がドレイン電極26の電圧値と近くなる。ドレイン電極26の電圧が上昇すると、SBD金属電極30の電圧値が、MOSFET部32のドレイン側の電圧値よりも低くなるため、SBD金属電極30によってMOSFET部32のドレイン側とドレイン電極26とが電気的に切断される。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧向上や短チャンネル効果の抑制を可能とする半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、半導体基板であるSiC基板1上に形成された、バッファ層2と、バッファ層2上に形成された、バッファ層2よりもバンドギャップが小さいチャネル層3と、チャネル層3上に形成された、チャネル層3よりもバンドギャップが大きいバリア層4と、バリア層4上に互いに離間して形成された、ソース、ドレイン電極7、8と、ソース、ドレイン電極7、8下から、バリア層4を通ってチャネル層3中にそれぞれ達する、不純物領域5とを備え、不純物領域5の下端は、バッファ層2に達しない。

(もっと読む)

半導体装置

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

半導体素子用エピタキシャル基板および半導体素子

【課題】InAlN/GaNヘテロ構造を有し、かつオーミックコンタクト特性の優れた半導体素子用のエピタキシャル基板を提供する。

【解決手段】半導体素子用エピタキシャル基板10Aが、下地基板1と、GaNからなるチャネル層3と、AlNからなるスペーサ層4と、III族元素としてInとAlとGaとを含む障壁層5と、を備え、障壁層が、InxAl1-xN(0<x<1)からなるマトリックス層にGa原子がドープされ、障壁層のGa原子の濃度が1.2×1020cm-3以下であるようにする。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および電子装置

【課題】 高い閾値電圧と、低いオン抵抗とを両立可能であり、かつ、パラレル伝導を抑制できる電界効果トランジスタを提供する。

【解決手段】

基板601上に、III族窒化物のバッファ層602、チャネル層603、障壁層605、およびキャップ層606が、前記順序で積層され、

各半導体層の上面は、(0001)結晶軸に垂直なIII族原子面であり、

バッファ層602は、格子緩和され、

障壁層605は、引っ張り歪みを有し、

チャネル層603およびキャップ層606が圧縮歪みを有するか、または、チャネル層603が格子緩和され、キャップ層606が引っ張り歪みを有し、

障壁層605上の一部の領域に、キャップ層606、ゲート絶縁膜607、およびゲート電極608が、前記順序で積層され、他の領域に、ソース電極609とドレイン電極610が形成されていることを特徴とする電界効果トランジスタ。

(もっと読む)

III族窒化物半導体素子、III族窒化物半導体素子の製造方法、および電子装置

【課題】 アクセス抵抗およびオン抵抗が低いIII族窒化物半導体素子、III族窒化物半導体素子の製造方法、および電子装置を提供する。

【解決手段】

障壁層902は、チャネル層901上方にヘテロ接合され、

チャネル層901の上部の一部およびその上方の障壁層902が除去されて凹部が形成され、

チャネル層901および障壁層902の一部にn型導電層領域904が形成され、

n型導電層領域904は、前記凹部の表面を含み、

n型導電層領域904の深さTimpが、n型導電層領域904表面の各部から前記表面と垂直方向の測定値で15nm以上であり、

オーミック電極906および907は、前記凹部の表面を介して前記n型導電層領域にオーミック接触していることを特徴とする、III族窒化物半導体素子。

(もっと読む)

トランジスタ及びその製造方法

【課題】動作層に与える影響が小さく且つ絶縁性を向上した下地層を備えたトランジスタを実現できるようにする。

【解決手段】トランジスタは、基板300の上に形成された下地層301と、下地層301の上に形成された窒化物半導体からなる動作層302とを備えている。下地層301は、複数の窒化物半導体層が積層された積層体である。下地層301は、遷移金属であるコバルト、ニッケル、ルテニウム、オスミウム、ロジウム及びイリジウムのうちの少なくとも1つを含む遷移金属含有層を有している。

(もっと読む)

半導体装置

【課題】ゲート耐圧を確保しつつ、増幅率を増加する半導体装置を提供する。

【解決手段】半導体装置10は、チャネル層13とゲート電極19と、を備え、チャネル層13とゲート電極19との間には、チャネル層13上に配置されるスペーサ層14と、スペーサ層14上に配置される電子供給層15と、電子供給層15上に配置されるバリア層16と、が配置される。スペーサ層14の伝導帯の下端のエネルギー準位Ec1は、電子供給層15の伝導帯の下端のエネルギー準位Ec2よりも低く、バリア層16の伝導帯の下端のエネルギー準位Ec3は、電子供給層15の伝導帯の下端のエネルギー準位Ec2よりも高い。

(もっと読む)

窒化物半導体デバイス

【課題】 窒化物半導体デバイスを提供する。

【解決手段】 一実施形態では、デバイスはIII族窒化物チャネル層(3)とIII族窒化物チャネル層(3)上のIII族窒化物障壁層(4)とを含み、III族窒化物障壁層(4)は第1部分(4−1)と第2部分(4−2)とを含み、第1部分(4−1)は第2部分(4−2)より薄い厚さを有する。pドープIII族窒化物ゲート層部(5)は、III族窒化物障壁層(4)の少なくとも第1部分(4−1)上に配置され、ゲートコンタクト(10)はpドープIII族窒化物ゲート層部(5)上に形成される。

(もっと読む)

半導体装置およびその作製法

【課題】窒化物半導体を用いたヘテロ構造電界効果トランジスタにおいて、オーミック接触抵抗を大きく低減し、同時に、ソース電極2からチャネルまでの抵抗(アクセス抵抗)を大きく低減し、その結果として、高速化および低損失化(低消費電力化)が可能となる半導体装置およびその作製法提供すること。

【解決手段】ソース電極2とドレイン電極4とに、それぞれオーミック接触し、チャネル層窒化物半導体よりも小さいバンドギャップを有する再成長窒化物半導体(2)と、前記チャネル層窒化物半導体との間を、再成長組成傾斜窒化物半導体(1)を介して接続することによって、ソース電極2とチャネルとの間、および、ドレイン電極4とチャネルとの間を、それぞれ結ぶ電路中の半導体バンドギャップの不連続が解消されていることを特徴とするヘテロ構造電界効果トランジスタを構成する。

(もっと読む)

ゲルマニウムベースの量子井戸デバイス

量子井戸トランジスタは、ゲルマニウムの量子井戸チャネル領域を有する。シリコンを含有したエッチング停止領域が、チャネル近くへのゲート誘電体の配置を容易にする。III−V族材料のバリア層がチャネルに歪みを付与する。チャネル領域の上及び下の傾斜シリコンゲルマニウム層によって性能が向上される。複数のゲート誘電体材料によって、high−k値のゲート誘電体の使用が可能になる。  (もっと読む)

(もっと読む)

窒化物半導体装置

【課題】パワートランジスタに適用可能なノーマリオフ型の窒化物半導体装置に生じる電流コラプスを抑制できるようにする。

【解決手段】窒化物半導体装置は、サファイアからなる基板11と、該基板11の上に形成されたGaNからなるチャネル層13と、該チャネル層13の上に形成され、該チャネル層13よりもバンドギャップエネルギーが大きいAlGaNからなるバリア層14と、該バリア層14の上に形成され、p型AlGaN層15及びp型GaN層16を含むp型窒化物半導体層と、該p型窒化物半導体層の上に形成されたゲート電極19と、該ゲート電極19の両側方の領域にそれぞれ形成されたソース電極17及びドレイン電極18とを有している。p型窒化物半導体層は、ゲート電極19の下側部分の厚さが該ゲート電極19の側方部分の厚さよりも大きい。

(もっと読む)

電界効果トランジスタ

【課題】 二次元電子ガスを高効率に生成させることができ、かつコンタクト抵抗の抵抗値が小さな電界効果トランジスタを提供することである。

【解決手段】 電界効果トランジスタ10においてスペーサ層13は、チャネル層12のバンドギャップよりも大きなバンドギャップを有する。第1電子供給層14は、厚み方向一方Z1に向かうにつれて、アルミニウム存在比が連続的に大きくなる組成に設定される。第2電子供給層15は、第1電子供給層14におけるアルミニウム存在比の最大値以上のアルミニウム存在比に設定される。

(もっと読む)

電界効果トランジスタ

【課題】蛇行した形状に形成されたリセス部を備えることにより、オン抵抗を低減することができる電界効果トランジスタを提供することを目的とする。

【解決手段】電界効果トランジスタ1は、チャネル層11と、チャネル層11とヘテロ接合を構成するキャリア供給層12と、キャリア供給層12の表面から掘り下げて形成されたリセス部13と、リセス部13に沿って形成された第1絶縁層31と、第1絶縁層31の上に形成された第1ゲート電極23と、リセス部13に対してチャネル長方向の一方側に形成されたソース電極21と、リセス部13に対してチャネル長方向の他方側に形成されたドレイン電極22とを備える。リセス部13は、ソース電極21とドレイン電極22とが平面視で平行に対向するチャネル長の範囲内において、蛇行しながらチャネル長方向と交差する方向に延長されている。

(もっと読む)

窒化物系化合物半導体装置、及びその製造方法

【課題】オーミック電極のオーミックコンタクト抵抗を確実に低減させる。

【解決手段】各オーミック電極3、4は、GaNキャップ層26表面のリセス28周辺部位に接触する第1電極51と、第1電極51に接触して、リセス28を介して2次元電子ガス層27に及ぶ第2電極52とを有している。第1電極51は、リセス28の開口部を囲む環状のものである。第2電極52は、第1電極51に重なる頭部52a、及びリセス28内に形成された柱状部52bからなる。第1及び第2電極51、52を第1及び第2温度でそれぞれ熱処理しているので、第1及び第2電極51、52のオーミックコンタクト抵抗を共に低減させ、各オーミック電極3、4そのもののオーミックコンタクト抵抗を低減させることができる。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗の上昇を抑制しつつ閾値電圧を大きくできる電界効果トランジスタを提供する。

【解決手段】キャリア走行層13である第1窒化物半導体層13と、第1窒化物半導体層13の上に設けられた、第1窒化物半導体層よりもバンドギャップエネルギーの大きい第2窒化物半導体層14と、第2窒化物半導体層14の上に順に設けられた、InGaN16層と、p型窒化物半導体層18と、ゲート電極22とを備える電界効果トランジスタであって、InGaN層16は、ゲート電極22直下の表面に第1の凹部19を有する。これにより、オン抵抗を一定に抑えつつ、閾値電圧を大きくすることができ、ノーマリオフ型のトランジスタが実現できる。

(もっと読む)

ゲートリセスの形成方法、AlGaN/GaN−HEMTの製造方法及びAlGaN/GaN−HEMT

【課題】閾値電圧(Vth)のばらつきの発生を抑制した、ゲートリセスの形成方法、ノーマリオフ型のAlGaN/GaN−HEMTの製造方法及びAlGaN/GaN−HEMTを提供する。

【解決手段】光電気化学エッチングにより、バンドギャップエネルギーが、ゲート開口部19から層方向に変化する半導体層の表面から前記半導体層内の所定の半導体層のバンドギャップエネルギーに相当するエネルギーを有するUV光を照射しながら、SiN表面保護層17の前記ゲート開口部から前記半導体層内の所定のバンドギャップエネルギーの半導体層をエッチングすることを特徴とするゲートリセス20の形成方法。

(もっと読む)

電界効果トランジスタ

【課題】十分に大きな電流密度を得ることができるノーマリオフ型の窒化物半導体からなる電界効果トランジスタ及びその製造方法を提供する。

【解決手段】基板101上にAlNバッファ層102、アンドープGaN層103、アンドープAlGaN層104、p型GaN層105、高濃度p型GaN層106が順に形成され、ゲート電極111が高濃度p型GaN層106とオーミック接合する。アンドープAlGaN層104の上にはソース電極109及びドレイン電極110が設けられる。アンドープAlGaN層104とアンドープGaN層との界面で発生する2次元電子ガスとp型GaN層105とによって生じるpn接合がゲート領域に形成されるのでゲート電圧を大きくすることができる。

(もっと読む)

21 - 40 / 128

[ Back to top ]